Δ-Σ 转换器信噪比有何不同之处

发布时间:2010-9-21 10:58

发布者:eetech

|

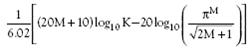

许多工程师仍努力使 (Δ-Σ) 转换器这个圆形销子适应标准 ADC 这个方形孔 当我还是孩子的时候,父母给我买了一个直径为 1 英寸的闭壳龟。我为此兴奋不已!为了保护这个海龟,我准备把它放到我的货车上。车上有个狭槽可以插入方形、三角形和圆形的销子。妈妈看到我拿走一个锤子,就知道肯定不会有好事,于是她对我说:“你是无法将一个方形的销子(或是一个海龟)放进一个圆形的孔中去的”。 这个教训也同样适用于下面的 Δ-Σ 调制器和 ADC 中——一个从 20 世纪 30 年代就被提出的基本概念。该转换器的拓扑结构与其他拓扑的结构有一点点不同。然而,许多工程师仍努力使转换器适应标准的 ADC 方形孔。 Δ-Σ 转换器远远不止是一款简单的模数转换器。它拥有过采样机制、一个调制器和一个数字滤波器。过采样机制在较宽的频率范围内扩展噪声功率。调制器形成低频噪声或将其推至更高频率。数字滤波器可以对噪声信号加以平均并将其从高频信号中消除。理想的逐次逼近寄存器和管线式转换器的 SNR(信噪比)为6.02N+1.76(见参考书目 1),其中 N 为转换器位数。Δ-Σ 转换器的信噪比为 6.02 (N+NINC)+1.76,其中,N 为调制器位数,NINC 为增加的精度,具体为:  在这个公式中,M 为调制器阶数,K 为转换过程中的过采样速率。 带有一阶调制器的理想的 Δ-Σ 转换器信噪比为 6.02N+1.76–5.17 +30log10OSR,其中 OSR 为过采样速率,N 为调制器位数而不是转换器的位数(见图1)。.  图1、带有一阶调制器的 Δ-Σ 转换器输入端的信噪比为 6.02N+1.76–5.17 +30log10OSR 这些理想公式均假设 ADC 和 DAC(通常为一位器件)的线性度、噪声以及偏移误差是完美的,且数字滤波器也有一个理想的砖墙响应。事实上,Δ-Σ 转换器并不像我们希望的那么理想。 这些理想的理论只能作为参考,最好的方法仍然是依靠转换器性能的基准数据。这些数据将向你展示转换器性能的真实特点。凭借这些基准数据,并通过对 DC 输入信号进行上百次的采样,您就可以测量出转换器的均方根噪声。在这种情形下,公式 20log10(VRMS-FS/VRMS-NOISE) 可以用来描述任何 ADC 信噪比。 |

网友评论