高速Σ-ΔADC的误差校正方法研究

发布时间:2010-9-21 10:56

发布者:eetech

|

1 概述 Σ-Δ调制是目前国际上的A/D转换器设计中很受欢迎的一种技术,与传统的Nyquist频率采样的A/D转换器工作原理有所不同,采用的是过采样和低位量化结合的方法。其中,过采样技术在模/数混合电路中的应用,能够避免传统A/D或D/A转换方法实现中遇到的诸多困难,尤其是在对低频信号要求高分辨率的应用领域,传统转换方法需要较高精度的模拟结构(模拟电阻、电容等),从而使整个A/D转换器的成本很高。Σ-ΔADC能够避免使用高精度模拟电路,将噪声推向高频,具有分辨率高,量化结构简单等优点。由于电磁环境日益恶化,对接收机的动态范围要求越来越高,跳频、扩频等宽带信号的应用又要求使用宽带测量设备,这些都对ADC的分辨率和速度提出了更高的要求。 调制器(Modulator)属于Σ-ΔADC电路中的模拟电路部分,它的结构选择和电路参数设计都极大地影响着整个ADC的信噪比(SNR)等性能指标。在Σ-Δ调制器中,使用了过采样、噪声成形等关键技术。这些技术还使它另外具有一系列固有的优点,如易于与数字信号处理系统单片集成,无须采样保持电路,对输入端抗混迭滤波器要求很低等。下面先讨论过采样与MASH噪声成形的主要单元分析,最后针对DAC失真误差,设计并仿真了一种数字误差校正技术。 2 基本原理与技术 2.1 Σ-ΔADC基本原理及调制器的组成 Σ-ΔADC由两部分组成:调制器和数字抽取滤波器。其中调制器的工作原理是采用远远大于Nyquist频率的时钟对输入模拟信号进行”过采样”,采样频率与Nyquist频率之比定义为过采样率M,是调制器的重要结构参数之一。由于采样频率很高,则无需传统的PCMADC中的保持电路。采样后的信号与前一时刻的采样信号相比较,对其差值做出低位量化,输出低位码流,并根据量化器的输出决定返回+Δ或-Δ反馈信号。调制器的基本结构如图1所示,主要由采样环节、积分器、量化器以及D/A反馈组成,其中fs表示采样时钟频率,K1,K2分别表示输入信号和反馈信号的增益系数。  图1 Σ-Δ调制器基本结构 习惯上,定义调制器中含有的积分器个数为调制器的阶数L,量化器的个数为级数。对调制器的线性模型做离散域的z变换分析,并将量化误差模型化为噪声信号,可以推导出输出信号Y对输入信号X与量化误差E的传递函数,在有效信号频率内,输入信号保持不变而噪声信号被差分衰减,即 Y(z)=z-LX(z)+(1-z-1)LE(z) (1) 通常,对调制器性能评测的重要参数之一是信噪比SNR,即信号功率与噪声功率之比  (2) (2) 这里ps为有效信号的功率,对正弦信号来说,ps=  ,A为幅度;pq是信号频带内总的量化噪声功率,由E(z)的传递函数在有效信号频带内积分得到  (3) (3) 从上式可以看出,分别提高M或L都能带来SNR的提高。但当信号频率达到几十MHz以上的高频范围后,M的提高势必会受到现有工艺,以及功耗等制约。目前,更多的研究改善SNR的方法是针对L的提高。 从调制器内在稳定性考虑,针对高阶调制器(L≥3),又有两种结构上的取向,即单级single-loop结构和多级级联的MASH结构。 2.2 过采样及MASH(多级噪声成形)技术 本文中使用记号fN来表示Nyquist调制器工作时的采样率,而它与基带信号最高频率fB的关系工程上一般为fN≈2.2fB~2.5fB。所谓过采样,就是指采样速度fs远大于fN。这里称M=fs/fN为“过采样比”。在Σ-ΔADC的设计中,M远大于1,且取为2的整数次幂(如32、64等)。过采样带来的好处为压缩基带内量化噪声,降低对输入端模拟滤波器的要求等。 但是,光凭过采样来压缩基带内噪声是低效率的,提高4倍采样率才相当于提高1bit分辨率。为了更有效地衰减基带内量化噪声,应在过采样条件下进一步加入噪声成形(noise shaping)技术。最基本的一阶噪声成形器即所谓的一阶Σ-Δ调制器,其原理此处不再讨论。这里只指出,它可被转化为如图2所示的离散时间等效模型。  图2 一阶Σ-Δ调制器离散时间等效模型 图2中的积分器用I(z)=(1-z-1)-1等效描述,而1bit ADC被加性噪声源q(n)替代。嵌在反馈环路中的1bit DAC被一个单位时延z-1取代,以避免在离散时间模型中出现无时延反馈环。q(n)是与输入信号无关的白噪声,用它能够方便地描述Σ-Δ调制器在大量信号作用下的平均行为,分析可得其输入、输出关系式为 Y(z)=X(z)+(1-z-1)Q(z) (4) 由上式可知,在信号频谱X(z)未变的同时,白噪声Q(z)被(1-z-1)加权而成为“高通”形状。此现象正是所谓“噪声成形”。加权函数(1-e-j2πfT)的零点f=0使得基带内噪声被大大压缩;而在带外的高频端,噪声却略有上升。 在实际应用中,为更有效地压低量化噪声达到分辨率要求,还得考虑高阶噪声成形。一般地,将L个一阶Σ-Δ调制器组合起来,可以实现(1-z-1)L(L阶噪声成形)。 标准的MASH(Multistage Noise Shaping,多级噪声成形)结构如图3。它实际上是L个一阶Σ-Δ调制器的串联,其中前一级调制器内的1bit ADC的量化误差被送入下一级进行再量化,然后将各级的输出码流送入运算节点进行处理。最后输出了经(1-z-1)L成形处理后的低分辨率码流。显然,这样的前馈结构不会存在任何稳定方面的问题。  图3 MASH结构框图 MASH中的数字处理节点所做的工作是抵消各级的量化误差: 第一级:Y1(z)=X(z)+(1-z-1)Q1(z),将-Q1(z)送入第2级,有Y2(z)=-Q1(z)+(1-z-1)Q2(z),再将-Q2(z)送入第3级,有Y3(z)=-Q2(z)+(1-z-1)Q3(z),..直至YL(z)=-QL-1(z)+(1-z-1)QL(z),而运算节点使得 Y(z)=Y1(z)+(1-z-1)Y2(z)+...+(1-z-1)L-1YL(z)=X(z)+(1-z-1)LQL(z) (5) 这样,就等效实现了(1-z-1)L噪声成形。除MASH外,还有许多新颖的采用计算机辅助设计的Σ-Δ噪声成形方案,用其可实现更高效的噪声成形。 3 一种DAC非线性误差校正方法 在MASHΣ-ΔADC中,与一位(1bit)量化相比,采用多位量化器具有增大信噪比(SNR),增加稳定性以及降低运算放大器规格等优点。然而,内部DAC的非线性导致性能瓶颈,通常要求其最少具有与整个ADC同样好的线性。现在,对于较大过采样比(OSR>32),采用即时数字校准、失配整形可解决此问题。但在宽带ADC中,OSR较小(通常≤4),失配整形法就变得无效。本文描述了一种数字即时校准方法。不同于较早的技术,其对低过采样比状态有效。并且,此方法可以跟随漂移。 3.1 校正系统 以二阶Σ-Δ调制器(DS1)为例来说明给出的校正技术。如图4所示,内部DAC有两个输出:v1和vT,分别输入到循环滤波和校准ADC(DS2)。由校准ADC得到^eD,即所有输出电平的DAC误差eD的数字估计,并且其被存储在RAM中。在转换时,通过FIR滤波器NLF(z)过滤RAM的输出,从而校正内部DAC误差,并从DS1的数字输出d1中减去过滤输出结果。获得^eD的过程和系统的详细分析在以下内容中给出。  图4 带有误差校正的Σ-Δ调制器 在图4所示系统中,假设单独DAC输出为两个积分器提供反馈信号。系数b1、b2的不匹配对系统线性没有影响。值得注意的是,系统没有对内部ADC的非线性误差进行校正。这些误差被与量化噪声同样的噪声传输函数所抑制,其很少作为问题提出。当使用很低的OSR时,这样是不够的,就高线性而言,需要增加阶数或使用ADC元件失配整形。 3.2 校正方法 实际DAC输出电平误差的即时获得适应于DAC的结构。如果DAC可提供多重输入和输出,那么离线校准能够被传输到后台进程。如果那样,对于DAC的每个可能的输入,数字校准信号dT将提供阶梯波形。通过校准Σ-Δ转换器DS2,每个DAC输出电平vT被转换成数字形式d2,然后通过LPF低通滤波而消除DS2的量化误差。然后,减去dT从而补偿电平误差eD,这样,得到误差估计^eD并将其存储在RAM中,并且对每一输出d1将再次调用^eD并校正。在运行过程中,周期性地重复校准,以追踪DAC输出电平中产生的漂移。 在低过采样率(OSR)和低阶循环滤波器情况下,从DAC的输出v1到DS1的输出d1的传输函数不能由NLF(z)=-1正确地近似。为了得到精确的误差校准,如图4所示,RAM的输出需要被实际的NLF(z)(此处为-2z-1+z-2)过滤。 在一些DAC的实现中,使用了N个等价单位元件(电流源、电容、电阻等)。如果在DAC中执行N+1个元件,可使用上述算法,利用DS2逐个顺序地测量它们的误差。换句话说,输出信号d1与校准信号dT一样可被使用。利用n个单位元件通过调用d1值从而产生v1,剩余的N-n个单位元件被用来产生vT。如果DAC增益和偏移误差是可以被接受的,为了使所有单位元件误差总和可取零,那么vT中的误差是v1中误差的负数。因此,通过将vT中的模拟采样分类进入通道,使用其中一个通道专用于每个可能输入(d1)码和其补码,DS2可用来以数字形式产生单独DAC电平。由于为每一DAC电平复制存储元件(反馈电容),DS2的运算可容易地在通道中多重复用。 由于线性运算,校准ADC(DS2)自身必须要有高的线性。这需要在DS2中使用1位内部量化器。但是,由于DAC非线性信息保持,线性影响(增益和偏移误差)在DS2中是可以接受的。同样,实际DAC误差传输函数(从v1至d1)和其数字复制部分NLF(z)之间的匹配误差对整个转换器的线性仅有较小的影响。 3.3 仿真结果 数字校正ADC(如图4的DS2)的运行仿真条件如下述。假设5bit(322电平)内部ADC和DAC,在DAC中有0.1%线性梯度误差。这符合中等误差0.4%的要求。在所有电路中,所有运放和任意失配电容(有0.1%标准偏差)的有限直流增益设定为54dB。使用OSR=4。在DS1中加入峰值为0.45V的中频双音调输入信号u1,采用二阶单位Σ-ΔADC实现DS2。为了论证利用校准可得到的高线性,DS1被接入在220MASH(包含10bitADC作为其第二级)中。这里不考虑在MASH(多级噪声整形)各级中的失配,它同样可由数字方法校正。 采用理想DAC、非理想运放和电容,系统运行计算出的频谱如图5(a)所示。图5(b)给出了使用误差校准的非线性DAC得到的频谱。可以看出,产生了大的谐波,SFDR仅为52dB。当使用了本文提出的数字校正技术后,频谱结果如图5(c)所示,得到SFDR>100dB。为了得到这样高的SFDR所需要的充分精确的eD估计,DS2对DAC的每一电平进行了218采样(如果DS2时钟控制在fs=5MHz,那么后台校准完整循环需要约4秒)。最后,图5(d)说明了使用NLF(z)=-1后的有害影响,即SFDR由101dB降至60dB。  图5 MASH的输出频谱(215采样,64倍FFT,fB=fs/8,OSR=4) 5 结论 本文介绍了Σ-Δ调制器的基本原理和技术,并针对采用多位内部量化器的MASH Σ-ΔADC提出了一种即时数字校正方法。对于低过采样比的模数转换器,采用通常的失配整形技术效果不佳,但本方法可有效应用于此。通过仿真证明,使用本文提出的即时数字校正法可得到极好的线性。 |

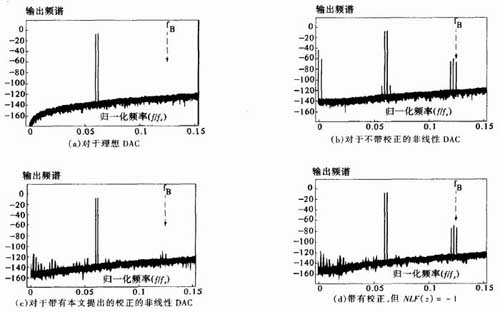

网友评论