1.1GHzМЏГЩЕЅЦЌЫјЯрЦЕТЪКЯГЩЦїMC145190

ЗЂВМЪБМфЃК2010-9-18 17:06

ЗЂВМепЃКtechshare

ЙиМќДЪЃК

MC145190 , ЦЕТЪКЯГЩЦї

|

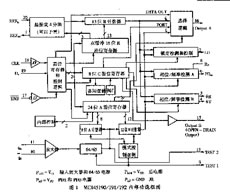

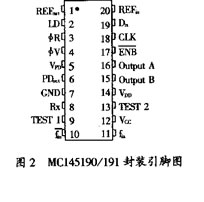

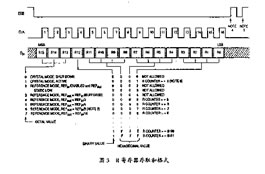

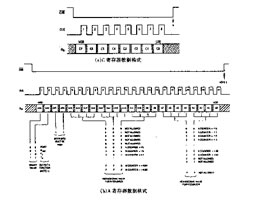

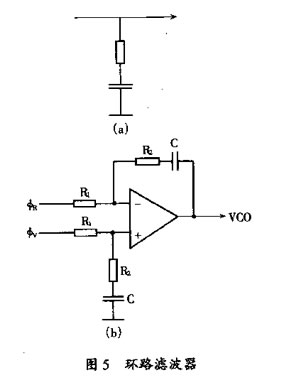

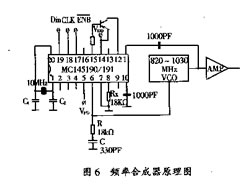

ЫцзХИпЫйМЏГЩЙЄвеММЪѕЕФЗЂеЙЃЌЫјЯрЦЕТЪКЯГЩЦїЕФМЏГЩЛЏГЬЖШвбДѓДѓЬсИпЁЃФПЧАвбГіЯжСЫвЛЯЕСаНЋИпЫйЧАжУКЯЦЕЦїМЏГЩдкЦЌФкЕФЕЅЦЌМЏГЩЦЕТЪКЯГЩЦїаОЦЌЁЃР§ШчУРЙњMotorolaЙЋЫОЕФMC145190ЃЏ191ЃЏ192ЁЂMC145200ЃЏ201КЭШеБОИЛЪПЭЈЕФMA101XTЁЂMB1501ЃЏ1504ЯЕСаЕШЕШЁЃЦЌФкИпЫйЛЛФЃЧАжУЗжЦЕЦїЭЈГЃЮЊЙЬЖЈЁТ64ЃЏ65ЛђЁТ32ЃЏ33ЃЌЙЄзїЦЕТЪПЩДя500MHzЁЋ2GHzЁЃМЏГЩЕЅЦЌPLLЦЕТЪКЯГЩЦїаОЦЌИјЦЕТЪКЯГЩЦїЕФЕчТЗЩшМЦДјРДСЫМЋДѓЕФЗНБуЃЌЖјЧвЪЕЯжСЫЕчТЗНсЙЙЕФаЁаЭЛЏЃЌвђДЫБЛЙуЗКгУдкИіШЫвЦЖЏЭЈаХЪжЛњЁЂЮоЩўЕчЛАКЭГЕдивЦЖЏЭЈаХЪжЛњжаЁЃ ЯТУцОЭMotorolaЙЋЫОЕФ1.1GHzЕЅЦЌЦЕТЪКЯГЩЦїаОЦЌMC145190ЃЏ191ЃЏ192ЕФадФмНсЙЙКЭЕчТЗЩшМЦзїНщЩмЁЃ 1 MC145190ЃЏ191ЃЏ192ЕФНсЙЙЬиЕуКЭв§НХЙІФм MC145190ЃЏ191ЃЏ192ЪЧДјгаДЎааПкЕФзюИпКЯГЩЦЕТЪПЩДя1.1GHzЕФЕЅЦЌМЏГЩЫјЯрКЯГЩЦїаОЦЌЁЃгЩгкЦЌФкВЩгУСЫУцЯђзжНкЕФЬигаЬхЯЕНсЙЙЃЌвђЖјЪЙЦфФкВПБрГЬБфЕУЗЧГЃШнвзЁЃгЩгкФкВПМФДцЦїЪЙгУСЫзЈУХЩшМЦЕФадФмгХСМЕФѓщЮЛМФДцЦїЃЌЪЙЕУетШ§ИіМФДцЦїЕФЪ§ОнЫцЛњДцШЁВЛ ашвЊЕижЗПижЦЮЛМДПЩЭъГЩЁЃЦЕТЪКЯГЩЦїЦЕТЪЕФЧаЛЛПЩЭЈЙ§DinЁЂCLKЁЂENBШ§ИіДЎааПкЃЌАбЪ§ОнДЋИј24ЮЛѓщЮЛМФДцЦїAРДЪЕЯжЁЃЭЌЪБЃЌЛЙдЪаэѓщЮЛМФДцЦїCЙиБеВЛЪЙгУЕФЪфГіПкЃЌвдМѕЩйЯЕЭГдыЩљКЭНгПкв§ШыдыЩљЁЃНгПкЖдSP1КЭMICROWIRETMОљМцШнЁЃ MC145190ЃЏ191ЃЏ192ЕФЦЌФкЙІФмПђЭМШчЭМ1ЫљЪОЁЃгЩЭМжаПЩжЊЃЌИУЦїМўЦЌФкзЈУХАВХХЕФШ§ИіѓщЮЛМФДцЦїЗжБ№ЮЊЃК24ЮЛѓщЮЛМФДцЦїAЁЂ16ЮЛѓщЮЛМФДцЦїRКЭ8ЮЛѓщЮЛМФДцЦїCЁЃЦфжа24bit AМФДцЦїДцДЂAЁЂNМЦЪ§ЦїЪ§ОнКЭПижЦЪ§ОнЃЌ16bit RМЦЪ§ЦїДцДЂЁТRВЮПМЗжЦЕЦїКЭОЇеёПижЦЪ§ОнЃЌЖј8bit CМФДцдђДцДЂПижЦЪ§ОнЁЃЗжЦЕЪ§ОнКЭПижЦЪ§ОнЭЈЙ§ЪБжгПкCLKЁЂЪ§ОнПкDinКЭЪЙФмПкENRОгЩТпМПижЦЕЅдЊДЎааЫЭШыетШ§ИіѓщЮЛМФДцЦїЁЃетжжЦїМўБИгаЫЋЖЫЦЕТЪЯрЮЛМьВтЪфГіІЕRЁЂІЕVКЭЕЅЖЫЦЕТЪЯрЮЛМьВтЕчСїБУЪфГіPDoutЕФСНжжМјЯрЪфГіЗНЪНЁЃетСНжжЯрЮЛМьВтЪфГіОљгаЯпадДЋЪфЬиадЃЌВЛДцдкМјЯрЫРЧјЁЃЕЋЕЅЖЫМјЯрЪфГіЕФзюДѓЕчСїгЩRxЙмНХЕНЕиЕФЭтНгЕчзшОіЖЈЁЃ ВЮПМЦЕТЪПЩжЇГжЭтМгОЇеёВњЩњЛђжБНггЩREFinЖЫЪфШыЃЌШЛКѓОПЩХфжУЕФ4ЗжЦЕЦїКѓЫЭШы13bitЕФПЩБрГЬЁТRВЮПМЗжЦЕЦїЃЌЛёЕУЫљашЗжБцТЪfRЁЃЪфШыЦЕТЪгЩfinЛђfinЖЫЪфШыЃЌзюИпЦЕТЪЮЊ1.1GHzЃЌЪфШыЗљЖШЮЊ200mVPЃPЁЃОЦЌФкЪфШыЗХДѓЦїINPUTAMPЗХДѓКѓЫЭШыЁТ64ЃЏ65ЫЋФЃЗжЦЕЦїЗжЦЕЃЌШЛКѓНјШыAКЭNМЦЪ§ЦїЃЌЫљвдfinКЭfvжЎМфЕФЗжЦЕБШЮЊN64ЃЋAЁЃ ДЫЭтЃЌаОЦЌЛЙОпгаСНИіЭЈгУЪ§ОнЪфГіПкOutput AКЭOutputBЁЃЦфжаOutput AЕБЖЈвхЮЊDATAOUTЪБЃЌПЩдЪаэаОЦЌМЖСЊЪЙгУЃЌЖјOutput BдђЮЊТЉМЋПЊТЗЪфГіПкЁЃ  Pin12= VCCЪфШыЗХДѓЦїКЭ64ЃЏ65ЕчдД Pin14= VDDзмЕчдД Pin5= VPD PDAКЭPDBЕчдД Pin7 = GND Еи ЭМ1 MC145190ЃЏ191ЃЏ192ФкВПЙІФмПђЭМ MC145190ЕФVDDЮЊ8 ЁЋ 9.5VЃЌMC145191ЕФVDDЮЊ4.5 ЁЋ 5.5VЃЌMC145192ЕФVDDЮЊ 2.7 ЁЋ 5VЁЃЫќУЧЕФДЎааПкзюИпЫЭЪ§ЫйТЪПЩДя4MbpsЃЌвђДЫПЩвдЪЕЯжИпЫйЬјЦЕЫЭЪ§ЁЃ MC145190ЃЏ191ЃЏ192ЕФЗтзАга20НХЬљЦЌЗтзАЪНКЭЫЋСажБВхЪНЗтзАСНжжЃЌЦфв§НХЙІФмЭМШчЭМ2жаЫљЪОЁЃгЩЭМжаПЩжЊЃЌет20жЛв§НХПЩЗжЮЊ5РрЃК2жЛВЮПМаХКХв§НХREFinКЭREFoutЃЌ7жЛЛиТЗв§НХfinЁЂfinЁфЁЂPDoutЁЂRxЁЂІЕRЁЂІЕvКЭLDЃЌ5жЛЪ§зжНгПкв§НХDinЁЂCLKЁЂENB'ЁЂOutput AКЭOutput BЃЌ2жЛМьВтв§НХTEST1КЭTEST2ЃЌ4жЛЕчдДв§НХVDDЁЂVCCЁСVPDКЭGNDЁЃ  REFin КЭREFoutв§НХЮЊPin20КЭPinlЃЌетСНИів§НХПЩзїЮЊЭтНгОЇЬхЛђЪфШыВЮПМаХКХЪЙгУЁЃЦфЙІФмФЃЪНгаОЇЬхФЃЪНКЭВЮПМФЃЪНСНжжЃЌФЃЪНПижЦгЩRМФДцЦїжаЕФR13ЁЂR14ЁЂR15ПижЦЮЛРДЪЕЯжЁЃ R13ЁЂR14ЁЂR15ПижЦЮЛЕФЪ§ОнИёЪНЃЌЪОгкЭМ3ЕФRМФДцЦїЪ§ОнДцШЁКЭИёЪНЭМжаЁЃЕБR13ЁЂR14ЁЂR15ЮЊАЫНјжЦ1зДЬЌЃЌМД001ЪБЃЌЮЊЭтНгОЇеёЙЄзїФЃЪНЃЌЕБR13ЁЂR14ЁЂR15ЮЊАЫНјжЦ3зДЬЌЃЌЮЊВЮПМЦЕТЪЪфШыФЃЪНЃЌЧвREFout=REFinЁЃ ЦфЫћ4ЁЂ5ЁЂ6ЁЂ7ЗжБ№ЮЊREFout=FEFinЃЏ2ЃЌREFout=REFinЃЏ4ЃЌREFout=REFinЃЏ8ЃЌREFout=REFinЃЏ16ЕШФЃЪНЁЃ Din(Pin19)ДЎааЪ§ОнЪфШыНХЁЂCLK(Pin18)ДЎааПкЪБжгЪфШыНХКЭENBЁф(Pin17)ДЎааЪЙФмЖЫЪфШыЕШзщГЩДЎааЪ§ОнЪфШыПкЃЌENBЁфЕЭЕчЦНгааЇЁЃМДENBЁфгЩИпЕчЦНБфЮЊЕЭЕчЦНЪБЃЌЪБжгCLKаХКХЕФЩЯЩ§биНЋDinЖЫЕФДЎааЪ§Онж№ЮЛвЦШыЯргІЕФМФДцЦїЁЃ Output A(Pin6)ПЩБрГЬЪ§ОнЪфГіЖЫПкЁЃИУв§НХПЩзїЮЊfRЛђfvЕФЪфГіПкЃЌвВПЩвдгУзїЪ§ОнЪфГіЖЫПкЁЃЦфЙІФмгЩAМФДцЦїЕФзюИпСНЮЛA23ЁЂЃС22ОіЖЈЃЌA23ЁЂA22ПижЦЮЛЕФЪ§ОнИёЪНЪОгкЭМ4ЕФAМФДцЦїЪ§ОнДцШЁКЭИёЪНЁЃЭМжаЃКA23 =A22=1ЪБЃЌOutputAзїfRЪфГіПкЃЌетЪБЕФfRЪЧОЇеёЦЕТЪЕФ13ЮЛRМЦЪ§ЦїЕФЗжЦЕЛКГхЪфГіЁЃвђДЫЃЌВтжЊfRжЕОЭПЩШЗЖЈRМЦЪ§ЦїЕФМЦЪ§жЕЁЃгЩгкМјЯрЦїЕФзюИпЙЄзїЦЕТЪЮЊ2MHzЃЌЫљвдfRБиаыЕЭгк2MHzЁЃ A23=1ЁЂA22=0ЪБЃЌOutputзїfv ЪфГіПкЃЌетЪБЕФЪфГіЦЕТЪfv ЪЧЪфШыЦЕТЪfinЕФ(N*64ЃЋA)ЗжжЎвЛЃЌЭЌбљвЊЧѓfvаЁгк2MHzЁЃ A23=0ЃЌA22=1ЪБЃЌOutput AзїЪ§ОнЪфГіПкЁЃетЪЧИі24ЮЛвЦЮЛМФДцЦїЕФДЎааЪфГіПкЃЌдкЪБжгТіГхЕФЩЯЩ§биж№ИіЪфГіДЎааЪ§ОнЃЌетжжЗНЪНгУвдЖрИіЦїМўМЖСЊЙЄзїЁЃ A23=0ЃЌA22=0ЪБЃЌOutput AзїЮЂЛњПижЦЖЫПкЕФРЉеЙПкгУЃЌаХКХдкCМФДцЦїЕФportЮЛC1=0ЪБЖЫПкЮЊЕЭЃЌC1=1ЪБЖЫПкЮЊИпЁЃ OutputB(Pin15)ТЉМЋПЊТЗЪ§зжаХКХЪфГіПкЃЌПЩвдгУзїMCUЖЫПкЕФРЉеЙПкЁЃИУЖЫПкЪмCМФДцЦїжаЕФoutBЮЛC0ЕФПижЦЃЌC0=0ЪБаХКХЮЊЕЭЃЌC0=1ЪБЖЫПкДІИпзшзДЬЌЃЌетЪБПЩЭтНгвЛИіЩЯРЕчзшЃЌЪЙЦфЪфГіЕчЦНРЕНаЁгкЛђЕШгкVPDЗЖЮЇФкЕФФГИіжЕЁЃ fin КЭfinЁф (Pin11ЁЂ10)ЦЕТЪЪфШыв§НХЃЌЪфШыЗљЖШЮЊ200mVPPЃЌзюИпЦЕТЪ1.1GHzЃЌВЩгУ1000PFЕчШнёюКЯЪфШыЁЃШєжЛгУfinНХЪфШыЪБЃЌfinЁфБиаыЭЈЙ§1000PFЕчШнёюКЯЕНЕиЁЃ PDoutКЭІЕRЁЂІЕV(Pin16КЭPin3ЁЂ4)ЗжБ№ЮЊЕЅЖЫМјЯрЪфГіКЭЫЋЖЫМјЯрГіЁЃMC145190ЃЏ191ЃЏ192ЕФМјЯрЦїгыMC145146ЕФМјЯрЙІФмЛљБОЯрЭЌЃЌЕЋPDoutЕФСїШыСїГіЕчСїПЩЭЈЙ§CМФДцЦїжаЕФC3ЁЂC2ЮЛПижЦ(МћЭМ4(a)CМФДцЦїЪ§ОнИёЪНЭМ)ЃЌЖјЧвЛЙПЩвдЭЈЙ§RxЖЫ(Pin8)ЭтНгЕчзшRxЕїНкЁЃ Rx(Pin8)ЭтНгЕчзшв§НХЁЃЭтНгЕчзшжЕНсКЯCМФДцЦїC3ЁЂC2ШЗЖЈPDoutзЂШыСїГіЕчСїжЕЃЌЕБC3=C2=1ЪБЃЌPDoutПЩЕУЕНзюДѓЕчСїЁЃЖдMC145191RxЕФзюМбжЕбЁдёдк18kЁЋ40kІИжЎМфЃЌетЪБPDoutЕФСїШыСїГіЕчСїдк1ЁЋ2mAЗЖЮЇФкЁЃ LD(Pin2)ЛЗТЗЫјЖЈжИЪОЖЫПкЃЌЪфГіЕчЦНдкЕиЛђVDDжЎМфБфЛЏЁЃЛЗТЗЫјЖЈЪБЃЌLDЖЫПкЪфГіЮЊИпзшЕчЦНМгеТіГхаХКХЁЃ TEST1ЃЈPin9)ЫЋФЃЧАжУЗжЦЕЦїЁТ64ЃЏ65ФЃЪНПижЦаХКХШыПкЖЫЁЃЕБTEST1ЮЊЕЭЕчЦНЪБЃЌЫЋФЃЧАжУЗжЦЕЦїАДЁТ65ЗжЦЕЃЛЕБTEST1ЮЊИпЕчЦНЪБЃЌдђАДЁТ64ЗжЦЕЁЃ TEST2ЃЈPin13)ЧАжУЗжЦЕЦїЁТ64ЃЏ65ЪфГіЖЫПкЃЌЪфГіЦЕТЪгІЮЊЪфШыЦЕТЪfinЕФ1ЃЏ64Лђ1ЃЏ65ЁЃ VDDЃЈPin14)ЦїМўCMOSЪ§зжВПЗжЙЉЕчв§НХЃЌЖдMC145191ЃЌVDD= 4.5 ЁЋ 5.5VЁЃ VCCЃЈPin12 )ЦїМўRFЗХДѓЦїКЭЫЋФЃЧАжУЗжЦЕЦїЁТ64ЃЏ65ЕФЙЉЕчв§НХЃЌЖдMC145191ЃЌ VCC=4.5 ЁЋ 5.5VЁЃ VPD (Pin5)ЮЊМјЯрЦїPDAЁЂPDBЕФЙЉЕчв§НХЃЌЖдMC145191ЃЌVPD= 4.5 ЁЋ 5.5VЁЃ GND(Pin7)ЮЊЙЋЙВНгЕиЖЫЁЃ 2 MC145190ЃЏ191ЃЏ192ЕФЪ§ОнИёЪНгыБрГЬ MC145190ЃЏ191ЃЏ192ЕФCЁЂRЁЂAМФДцЦїОљЮЊѓщЮЛМФДцЦїЃЌЪ§ОнСїЕФЪфШыВЛашвЊЕижЗКЭПижЦаХКХЃЌЖјЪЧгЩЪ§ОнСїЕФзжГЄЖШРДОіЖЈЪфШыЕНФФИіМФДцЦїЁЃ8ИіЪБжгжмЦкЕФЪ§ОнСївЦШыCМФДцЦїЃЌ16ИіЪБжгжмЦкЕФЪ§ОнСївЦШыRМФДцЦїЃЌ24ИіЪБжгжмЦкЕФЪ§ОнСївЦШыAМФДцЦїЁЃЪ§ОнСїАДИпЮЛЫГађЯШвЦШыЃЌЖјCЁЂRЁЂAЕФгааЇЮЛдђАДЕЭЮЛЫГађМЦЫуЁЃ RМФДцЦїЕФДцШЁКЭЪ§ОнИёЪНШчЭМ3ЫљЪОЁЃИпЮЛR15ЁЂR14ЁЂR13ЕФПижЦЙІФмШчЭМжаЫљЪОЃЌЕЭЮЛR0 ЁЋ R12ЮЊ13ЮЛRМЦЪ§ЦїЕФЪ§ОнФкШнЃЌR=0ЁЋ8191ЁЃ CМФДцЦїЮЊ8ЮЛПижЦМФДцЦїЃЌЪ§ОнИёЪНШчЭМ4(a)жаЫљЪОЁЃ C7ЃPOLЮЛгУвдбЁдёМјЯрЦїЕФЪфГіМЋадЁЃЕБC7=1ЪБЃЌPDoutЪфГіЗДМЋадЃЌЧвІЕRКЭІЕvЛЅЛЛЙІФмЃЛC7=0ЪБЃЌPDoutЪфГіе§МЋадЃЌЧвІЕRКЭІЕvЙІФмВЛБфЁЃ C6ЃPDAЃЏBЮЛгУвдбЁдёМјЯрЦїPDAЛђPDBЃКC6=1ЪБбЁгУPDAЃЌЖјPDBдђНћжЙЃЛC6=0ЪБдђбЁгУPDBЃЌPDAетЪББЛНћгУЁЃ C5ЃLDEЮЛЮЊЛЗТЗЫјЖЈжИЪОМьВтЮЛЃЌИУЮЛЭЈГЃжУЁА0ЁБЁЃC4ЃSTBYЮЛгУвдПижЦЦїМўДІгкЫЏУпБИгУзДЬЌЃЌПЩНкЪЁЙІКФЁЃ C4=1ЪБЃЌPDoutКЭІЕRЁЂІЕvОљДІИпзшзДЬЌЃЌЧвRxЕчСїЙиЖЯЃЌAЁЂNЁЂRМЦЪ§ЦїЭЃжЙМЦЪ§ЃЌетЪБЦїМўДІгкЫЏУпБИгУзДЬЌЃЛC4=0ЪБЃЌPDoutКЭІЕRЁЂІЕvЃЌвдМАAЁЂNЁЂRМЦЪ§ЦїНјШые§ГЃЙЄзїзДЬЌЁЃ C3ЁЂC2ЮЛгУвдПижЦPDoutСїШыСїГіЕчСїЕФДѓаЁЃЌЕБетСНЮЛОљжУИпЮЛЁА1ЁБЪБЃЌПЩЕУЕНзюДѓЕчСї100%ЁЃPDoutЕчСїЕФДѓаЁВНГЄЛЙЪмC1ЃportЪ§ОнПижЦЁЃЕБOutputAВЛзїЪ§ОнЖЫПкЪЙгУЪБЁВЭЈЙ§AМФДцЦїжаЕФA23ЁЂA22ЮЛжУЪ§ПижЦЃЌМћЭМ4(b)AМФДцЦїДцШЁКЭЪ§ОнИёЪНЭМЁГЁЃ C1=0, дђPDoutАД10%ВНГЄБфЛЏЕчСїЃЌC1=1, дђPDoutАД25%ВНГЄБфЛЏЕчСїЁЃOutputAгУзїЪ§ОнЖЫПкЪЙгУЪБЃЌдђC1ОіЖЈOutputAЕФзДЬЌЃЌC1=1, дђOutput AЮЊИпЃЌC1=0, дђOutput AЮЊЕЭЁЃ C0ЃoutBЮЛОіЖЈOutput BЕФзДЬЌЃЌC0=1ЪБOutput BЮЊИпЃЌC0=0ЪБOutput BЮЊЕЭЁЃ   AМФДцЦїЕФЪ§ОнИёЪНШчЭМ4(b)жаЫљЪОЃЌAМФДцЦїЮЊ24ЮЛѓщЮЛМФДцЦїЁЃЦфжаИп4ЮЛЮЊПижЦТыЃЌA23ЁЂA22ШЗЖЈOutputAЕФЪфГіЙІФмЃЌA21 ЁЂA20ЮЊФкВПТпМПижЦТыЃЌБиаыЖМжУЁА1ЁБЁЃA0ЁЋA7ЮЊ8ЮЛТіГхЭЬГ§МЦЪ§ЦїЕФЪ§ОнТыA=0ЁЋ255ЃЌA8ЁЋA11ЮЊ12ЮЛжїМЦЪ§ЦїNЕФЪ§ОнТыN=5ЁЋ4095ЃЌNНћжЙаЁгк5ЁЃЯдШЛNМЦЪ§ЦїЕФШнСПДѓгкAМЦЪ§ШнСПЁЃдкЛЗТЗЩшМЦЪБЃЌвВБиаыЪЧNЃОAЁЃ 3 гІгУЩшМЦОйР§ ВЩгУMC145109ЃЏ191ЃЏ192ЩшМЦЕЅЛЗЦЕТЪКЯГЩЦїЪБЃЌБиаыЭтНгЛЗТЗТЫВЈЦїКЭХфЩЯвЛжЛЯргІЕФбЙПиеёЕДЦїVCOЁЃЭтНгЛЗТЗТЫВЈЦїЕФНсЙЙШчЭМ5ЫљЪОЃЌЭМ5(a)ЪЪгУгкPDAЃЌМДНггкPDAoutЪфГіЖЫЃЌетЪБЛЗТЗЩшМЦЙиЯЕЪНЮЊKІЕЁЄKVCO=Іиn2 * MCКЭ2ІЦ=ІиnRCЃЌЪНжаMЮЊЛЗТЗЗжЦЕБШЁЃ ЭМ5(b)ЪЪгУгкPDBЃЌетЪЧвЛИігадДТЫВЈЦїЃЌЛЗТЗЩшМЦЙиЯЕЪНЮЊKІЕЃЫVCO=Іиn2MCR1КЭ2ІЦ=ІиnR2CЁЃ  ВЩгУPDAЕФPDoutЪфГіЭМ5(a)ЪБЃЌМјЯрдівцKІЕ=IpoutЃЏ2ІаAЃЏradЁЃIpoutЮЊPDoutЕФСїШыСїГіЕчСїЃЌЧАУцвбжИГігЩCМФДцЦїПижЦТыКЭRxШЗЖЈЦфжЕЁЃ ШєВЩгУPDBЕФЭМ5(b)гадДТЫВЈЦїЪБЃЌKІЕ=VPDЃЏ2ІаVЃЏradЁЃ ЯТУцвдвЦЖЏЭЈаХGSMЦЕЖЮЦЕТЪКЯГЩЦїЮЊР§ЃЌНщЩмMC145191ЕФгІгУЩшМЦЗНЗЈЁЃвЦЖЏЭЈаХGSMБъзМЕФКЯзїЦЕЖЮЮЊ935ЁЋ960MHzКЭ890ЁЋ915MHzЃЌЫЋЙЄМфИєЮЊ45MHzЃЌЦЕЕРМфИєЮЊ200kHzЃЌЛЛЦЕЪБМфаЁгк5msЁЃвд935ЁЋ960MHzЦЕЖЮЮЊР§ЃЌИУЦЕТЪКЯГЩЦїЕФVCOгІТњзуЕФЦЕТЪЗЖЮЇЮЊЃК 2f0minЃf0max=2*935Ѓ960=910MHzЃЌ 2f0maxЃf0min=2*960Ѓ935=985MHz БфШнЙмЕФПижЦЕчбЙЕїаГЗЖЮЇЮЊ1ЁЋ5.5VЃЌдђбЙПиСщУєЖШЮЊЃК K0 =(985Ѓ910)/(5.5Ѓ1) = 17*106(HzЃЏV)=2Іа*17*106(radЃЏsЃЏV) ЦЕТЪКЯГЩЦїЕФдРэЭМШчЭМ6жаЫљЪОЁЃ  ЕЅЛЗЦЕТЪКЯГЩЦїЕФЦЕТЪМфИєЁїf0=fR=200kHzЃЌЭМжаВЩгУ10MHzОЇеёЁЃRМФДцЦїЕФR15ЁЂR14ЁЂR13жУГЩ001ЃЌREFin?КЭREFout?ЮЊЭтНгОЇеёЙІФмЃЌЫљвдЁТRМЦЪ§ЦїЕФЗжЦЕБШЮЊЃК NR = (fosc / fR) = (10*106) /200*103 = 50 НЋ50ЛЏЮЊЖўНјжЦЪ§ЃЌМДОЭЪЧ13ЮЛRМЦЪ§ЦїR0ЁЋR12ЕФЪ§ТыЁЃЛЗТЗПЩБрГЬађЗжЦЕБШM ЮЊЃК M1 = ( f01 / fR) = ( 960 / 0.2 = 4800 M2 = ( f02 / fR) =(935 / 0.2 = 4675 ЛЗТЗГЬађЗжЦЕЦїВЩгУЛЛФЃЭЬГ§МЦЪ§ЗНЪНЃЌЫљвдгаЃК M = PNЃЋA ЕФЙиЯЕЁЃЦфжаNЮЊжїМЦЪ§жЕЃЌAЮЊЭЬГ§ТіМЦЪ§жЕЃЌPЮЊИпЫйЧАжУЗжЦЕЦїЕФФЃжЕЃЌMC145191жаP=64ЁЃШєвдM2=4675ЮЊР§ЃЌгЩЩЯЪіЙиЯЕПЩШЗжЊ: N = 73ЃЌA = 3ЃЌМДM = PNЃЋA = 64*73ЃЋ3 = 4675ЁЃ НЋA=3ЃЌN=73ЛЏЮЊЖўНјжЦЪ§жЕЃЌМДОЭЪЧA0 ЁЋA7ЁЂA8 ЁЋA19ЕФЪ§ОнТыжЕЁЃЦфЫћЛЗТЗЗжЦЕБШЕФMжЕОљПЩвдгУДЫЗНЗЈРДШЗЖЈA0 ЁЋ A19ет20ЮЛЪ§ОнжЕЃЌДгЖјЪЕЯжБрГЬжУЪ§ЁЃ МјЯрЦїВЩгУPDAЃЌCМФДцЦїЕФC6=1ЃЌМјЯрдівцKІЕ=IpoutЃЏ2ІаAЃЏradЁЃЮЊЕУЕНзюДѓ100%ЕФСїШыСїГіЕчСїЃЌCМФДцЦїжаЕФC2=C3=1ЃЌRxШЁ18kІИЃЌPDoutСїШыСїГіЕчСїдМ2mAЃЌМДKІЕ=2*10-32ІаAЃЏradЁЃ бЙПиеёЕДЦїЕФбЙПиЬиадЮЊе§ЯђПижЦЬиадЃЌЫљвдЯЃЭћPDoutЪфГіе§МЋадЃЌМДC7=0ЃЌАД10%ВНГЄБфЛЏЕчСїЃЌМДC1=0ЁЃЫљвдCМФДцЦїжаC7ЁЋC0ЮЊЁА01001100ЁБПижЦТызДЬЌЁЃ КЯГЩЦїЕФЪфГіЦЕТЪдк935ЁЋ960MHzЃЌПчЖШЮЊ25MHzЁЃгЩЩЯЪіПЩжЊЃЌЛЗТЗПЩБфЗжЦЕБШдк4800ЁЋ4675ЗЖЮЇФкБфЛЏЁЃЯдШЛЃЌетЪБЫјЯрЛЗТЗЕФІЦКЭІиnвВНЋЪЧПЩБфЕФЃЌетжжБфЛЏНЋжБНггАЯьЦЕТЪКЯГЩЦїЕФЫВМфЬиадЁЃЮЊБЃжЄКЯГЩЦїадФмЃЌЭЈГЃзшФсЯЕЪ§ІЦгУІЦ=0.707РДНјааЛЗТЗЩшМЦЃЌЕБШЛЮЊЪЙЛЗТЗТњзуПьЫйЛЛЦЕЬиадЃЌвВПЩвдЗХПэЕНЁм1РДНјааЩшМЦЁЃІЦ=0.707вдКѓЃЌЛЗТЗЕФЩЯЯоЦЕТЪІиH Ёж ІиnЁЃ ПМТЧЛЗТЗЖдМјЯрВЈЮЦЕФвжжЦзїгУЃЌЭЈГЃвЊЧѓІиH Ём ( 1/5)*ІиnЃЌ МДІиn Ём ( 1/5*ІиR = 0.2 * 2Іа * 200 * 103(radЃЏs)ЁЃ гЩгкВЩгУPDAМјЯрЦїЃЌЛЗТЗТЫВЈЦїНггкPDoutЖЫПкЃЌШчЭМ6жаЫљЪОЁЃЛЗТЗЩшМЦЙиЯЕЮЊ: KІЕKVCO= Іиn2MCКЭ2ІЦ=ІиnRCЃЌМДЃК C = KІЕKVCO / Іиn2M R=2ІЦЃЏІиnR ЪНжаMШЁЛЗТЗПЩБфЗжЦЕБШжааФжЕЃЌ МДM = ( 1 / 2)(M1ЃЋM2ЃЉ= ( 1 / 2)(4800ЃЋ4675) = 4737.5ЁЃ Ыљвд гаC = (2*10Ѓ3ЃЏ2Іа*46.7*106)ЃЏ((1 / 5)*2Іа*200*103)2 ЁС4737.5 = 311.42 PF R=(2*0.707)ЃЏ(1 / 5)*2Іа*200*103ЁС311.42ЁС10Ѓ12=18.3 kІИ ЪЕМљжаCПЩвдШЁ330PFЃЌRПЩШЁ18kІИНгШыЕчТЗжаЁЃ ЛЗТЗЫјЖЈЪБМфПЩвдгУЯТЪННјааЙРЫуЃК ts = ( 4 / ІЦ*Іиn) = 22.5 ІЬs ПМТЧЪЧДЎааЫЭЪ§жУЪ§ЃЌвдМАЮЂЛњжИСюЪБМфдкФкЃЌдђЦЕТЪКЯГЩЦїЕФЦЕТЪЧаЛЛЪБМфtpЃМ1msЪЧЭъШЋПЩвдзіЕНЕФЁЃ |

ЭјгбЦРТл