FPGAдкжЧФмвЧБэжаЕФгІгУ

ЗЂВМЪБМфЃК2010-9-16 16:29

ЗЂВМепЃКtechshare

|

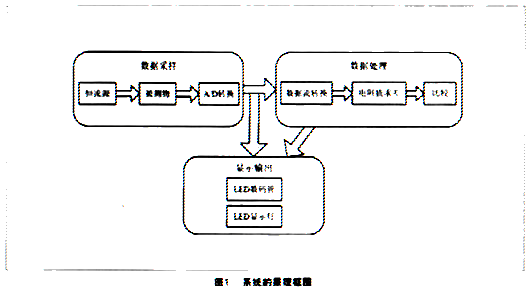

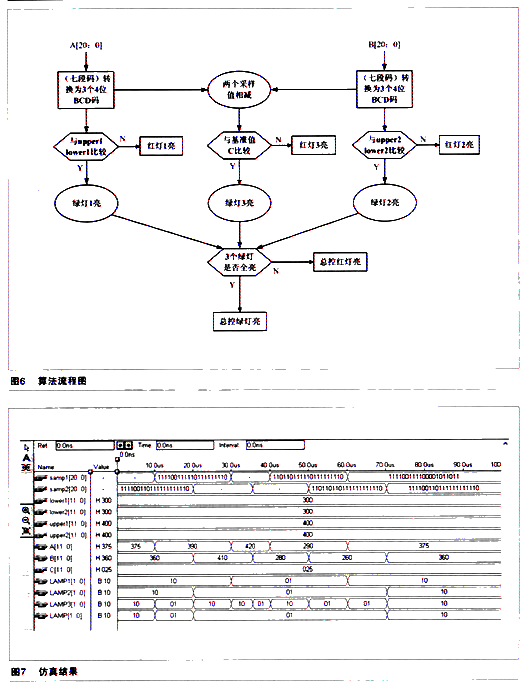

ЫцзХЮЂЕчзгММЪѕЕФЗЂеЙЃЌВЩгУЯжГЁПЩБрГЬУХеѓСа(FPGA)НјааЪ§зжаХКХДІРэЕУЕНСЫЗЩЫйЗЂеЙЁЃгЩгкFPGAОпгаЯжГЁПЩБрГЬЕФЬиЕуЃЌПЩвдЪЕЯжзЈгУМЏГЩЕчТЗЃЌвђДЫдНРДдНЪмЕНгВМўЕчТЗЩшМЦЙЄГЬЪІУЧЕФЧрэљЁЃ ФПЧАЃЌдкздЖЏЛЏМрВтгыПижЦвЧЦїКЭзАжУжаЃЌДѓЖрвд8ЮЛЛђ16ЮЛMCUЮЊКЫаФВПМўЁЃШЛЖјАщЫцзХЩњВњММЪѕЕФНјВНКЭЗЂеЙЃЌЖдМрВтгыПижЦЕФвЊЧѓвВдкВЛЖЯЬсИпЃЌУцЖдШевцИДдгЕФМрВтЖдЯѓКЭПижЦЫуЗЈЃЌДЋЭГЕФMCUЭљЭљВЛПАжиИКЁЃАбFPGAдЫгУЕНетаЉвЧБэКЭЩшБИжаЃЌПЩвдМѕЩйетаЉвЧЦїЁЂЩшБИЕФПЊЗЂжмЦкЃЌДѓЗљЖШЬсЩ§етаЉвЧЦїЕФадФмЃЌМѕЩйзмГЩБОКЭЬхЛ§ЁЃ дкЕЭзшжЕЁЂИпОЋЖШЯпШІЕчзшВтЪдвЧжаЙиМќВПЗжгУFPGAгВМўЕчТЗРДЪЕЯжЃЌПЩвдНкЪЁЯЕЭГЕФУцЛ§ПЊЯњЁЂМѕЩйЫљгУЕФаОЦЌЪ§КЭPCBАхПщЪ§ЃЌЬсЩ§ЯЕЭГадФмЃЌВЂНЕЕЭГЩБОЁЃ ЕЭзшжЕЁЂИпОЋЖШВтЪдвЧЯЕЭГНсЙЙНщЩм  ЯЕЭГЕФД§ВтЬхЪЧвЛИіШЦгаШ§зщЭЯпШІЕФЛњЙЙЃЌЭтаЮГпДчДѓдМЪЧ7ЁС7ЁС6(mm)ЃЌЭтаЮНсЙЙНЯИДдгЁЃгЩгкЯЕЭГвЊЭЈЙ§ВтСПД§ВтЯпШІЕФзшжЕЃЌРДШЗЖЈЯпШІЕФШІЪ§ЃЌвђДЫЃЌвЊЧѓгаБШНЯИпЕФВтСПОЋЖШЁЃАДееЙЄГЇСїЫЎЯпзївЕЕФвЊЧѓЃЌД§ВтЬхЕчзшжЕОљдк5QвдЯТЃЌВтСПОЋЖШдкЁР0.01ІИвдФкЃЌЗДгІЫйЖШдк0.8sвдФкЁЃећИіВтЪдЯЕЭГгЩЪ§ОнВЩбљФЃПщЁЂЪ§ОнДІРэФЃПщКЭЯдЪОЪфГіФЃПщзщГЩЃЌШчЭМ1ЫљЪОЁЃ Ъ§ОнВЩбљВПЗж гЩгкБОЯЕЭГвЊЖдЮЂаЁЕчзшНјааОЋШЗВтСПЃЌвђДЫВЩгУЫФв§ЯпжЦВтСПЗЈЃЌХфвдИпОЋЖШЁЂЕЭЮТЦЏЕФКуСїдДЁЃБОЯЕЭГЕФAЃЏDзЊЛЛаОЦЌВЩгУIntersilЙЋЫОЕФШ§ЮЛАыAЃЏI)зЊЛЛЦїICL7107ЃЌКуСїдДВњЩњЕФ10mAЕчСїСїОД§ВтЯпШІЃЌВњЩњвЛИігыЯпШІзшжЕГЩе§БШЕФбЙНЕЁЃДЫбЙНЕЭЈЙ§Ш§ЮЛАыAЃЏDзЊЛЛЦїжБНгзЊЛЛЮЊЦпЖЮТыаЮЪНЕФЪЎНјжЦЪ§ОнСїЃЌжБНгЫЭжСЯдЪОЪфГіВПЗжЃЌгЩLEDЪ§ТыЙмЯдЪОЪфГіЁЃ Ъ§ОнДІРэВПЗж етВПЗжгаШ§ИіЙІФмЃК (1)НЋAЃЏDзЊЛЛЦїЪфГіЕФЦпЖЮТыаЮЪНЕФЪ§ОнзЊЛЛЮЊBCDТыЃЛ (2)НЋзЊЛЛКУЕФЕФBCDТыЪ§ОнНјааЯрМѕЃЌЪЕЯжЕчзшжЕЧѓВюЙІФмЃЛ (3)НЋзЊЛЛКУЕФBCDТыЪ§ОнгыЩшЖЈЕФЩЯЯТЯоНјааБШНЯЃЌЕк2ВНЕУЕНЕФЕчзшВюжЕгыЛљзМБШНЯжЕНјааБШНЯЃЌЪЕЯжБШНЯЙІФмЁЃ БОЮФзХжиНщЩметвЛВПЗжЕФдРэвдМАЪЕЯжЁЃеыЖдЪ§ОнДІРэВПЗжЃЌетвЛВПЗжЙІФмПЩвдВЩгУШ§жжЗНАИРДЪЕЯжЃК (1)ВЩгУALUКЭ7485ЯЕСааОЦЌРДЪЕЯжЃЌетжжЗНАИашвЊ6ИіALUЕЅдЊ(3ЦЌДІРэ4ЮЛBCDМѕЗЈЕФЕЅдЊКЭ3ЦЌДІРэНшЮЛЕФЕЅдЊ)КЭ18ЦЌ74LS85аОЦЌ(зїЮЊЪ§зжБШНЯЦї)ЃЌеМгУЯрЕБДѓЕФЯЕЭГУцЛ§ЃЌВЂЧвПДЦ№РДЗЧГЃЗБЫіЙІФмИДдгЃЌВЛжБЙлЁЃЪБМфбгГйДѓЃЌВтСПЮѓВювВБШНЯДѓЁЃ (2)ЭъШЋВЩгУЪ§зжзщКЯТпМЕчТЗРДЪЕЯжЃЌетвЛЗНАИЩшМЦУХМїБШНЯЕЭЃЌЕЋЪЧеМгУЕФЯЕЭГУцЛ§ЁЂЙІКФКЭВтСПЮѓВюБШЕквЛжжЗНАИДѓЕФЖрЃЌДяЕННЯФбвдЪЕЯжЕФЕиВНЁЃ (3)ВЩгУFPGAРДЪЕЯжЃЌАбБОВПЗжвЊЪЕЯжЕФЙІФмЭъШЋМЏГЩдквЛПщFPGAЩЯЃЌгыЩЯЪіСНИіЗНАИБШНЯЃЌДѓДѓНкЪЁУцЛ§ЃЌЯЕЭГЙІФмШУШЫвЛФПСЫШЛЃЌЖјЧввЧЦїЮШзМЖШИќИпЃЌЗДгІЫйЖШИќПь ЯдЪОЪфГіВПЗж ИУВПЗжгаLEDЯдЪОЕЦ(КьЁЂТЬ)КЭLEDЪ§ТыЙмзщГЩЃЌИљОнЪфШыЯдЪОЯргІНсЙћЁЃ FPGAЪЕЯжЕФЪ§ОнДІРэЙІФм ВтЪдвЧжаЭЈЙ§Д§ВтЯпШІЕФбЙНЕЭЈЙ§Ш§ЮЛАыAЃЏI)зЊЛЛЦїICL7107КѓЃЌвЛЪфГіЕФЪ§Он(samplelЁЂsample2)ОљЮЊЦпЖЮТыаЮЪНЕФЪЎНјжЦШ§ЮЛЪ§(ИіЁЂЪЎЁЂАйЮЛ)ЃЌвЊЧѓгыСНИіПЩЕїЕФЩЯЯТЯо(BCDТыВІТыЪфШы)НјааБШНЯЃЌШєдкБШНЯЯоЖШФкдђССТЬЕЦ(greenlЁЂgreen2)ЃЌЗёдђССКьЕЦ(rerllЁЂred2)ЁЃСэЭтЃЌСНИіВЩбљжЕЯрМѕЃЌШєЦфВюжЕ(sub)дкЙЬЖЈЗЖЮЇвдФкдђССТЬЕЦ(green3)ЃЌЗёдђССКьЕЦ(red3)ЁЃЫљгаЕФТЬЕЦССЃЌзмПиЕФТЬЕЦ(greerl)ВХССЃЌЗёдђЃЌзмПиКьЕЦ(red)ССЁЃЩшМЦЗНАИАДееTOPЁЊDOwNЕФЫМЯыЖдЯЕЭГНјааећЬхЙІФмЛЎЗжЃЌдйвдBOTTOMЁЊuPЗНЪННјааЩшМЦЪфШыЃЌЪЙЯЕЭГОпгаВуДЮИа(hierarchy)ЃЌИїИіЙІФмФЃПщФкАќКЌаЁЕФФЃПщЃЌвВБугкФЃПщЕФжиИДЕїгУЃЌзюКѓНјаааОЦЌЕФЙІФмЁЂадФмЕШИїЯюФЃФтЁЃИїФЃПщЙІФмМАНсЙЙЭМНщЩмШчЯТЃК datachange(Ъ§ОнзЊЛЛ)ФЃПщ НЋЪфШЫЮЊЦпЖЮТыЕФЪ§ОнзЊЛЛЮЊBcDТыЃЌЪфГізЊЛЛКѓЕФЪ§ОнЃЌжБНгЫЭЕНЯдЪОЪфГіВПЗжЃЌдкLEDЪ§ТыЙмЩЯЯдЪОГіРДЃЌШчЭМ2ЫљЪОЁЃ  suball(МѕЗЈ)ФЃПщ ЯЕЭГЪ§ОнДІРэЕФКЫаФВПЗжЃЌАќРЈ3ИізгФЃПщЃЌРДЪЕЯжВЩбљЕФСНИі12ЮЛBCDТыЪ§жЎМфЕФЯрМѕЁЃЦфжаЕФКЫаФзгФЃПщЮЊ4ЮЛBcDМѕЗЈФЃПщЃЌЭЈЙ§НшЮЛЃЌНЋДЫФЃПщДЎНгЃЌЪЕЯжФЃПщИДгУЁЃНЋВюжЕЫЭЕНЯдЪОЪфГіВПЗжЃЌдкLEDЪ§ТыЙмЩЯЯдЪОГіРДЃЌШчЭМ3ЫљЪОЁЃ compareall(БШНЯ)ФЃПщ ЪЕЯжзЊЛЛКѓЪ§Он(AЁЂB)ЭЌЩшЖЈЕФЩЯЯТЯо(ЭМжаЮЊupperlЁЂlowerЁЃ1КЭupper2ЁЂlower2)НјааБШНЯЃЛМѕЗЈФЃПщЕУГіЕФВюжЕ(sub)ЃЌгыЩшЖЈЕФЛљзМжЕcНјааБШНЯЁЃзюКѓЪфГіБШНЯНсЙћЃЌНЋНсЙћЫЭЕНЯдЪОЪфГіВПЗжЃЌвдLEDЯдЪОЕЦаЮЪНРДЯдЪОНсЙћЃЌШчЭМ4ЫљЪОЁЃ lampФЃПщ змПиЯдЪОЕЦбЁдёФЃПщЃЌИљОнЪфШыЕФНсЙћРДОіЖЈЪфГіЕЦЕФбеЩЋЃЌШчЭМ5ЫљЪОЁЃ ОпЬхЫуЗЈСїГЬШчЭМ6ЫљЪОЁЃ  ЗТецбщжЄ Ъ§ОнДІРэФЃПщВЩгУverilogгябдБраДЃЌгУMaxplus IIНјааЙІФмЗТецЃЌЩшЖЈupperlгыupperl2жЕОљЮЊ400(МДЩЯЯо4.0ІИ)ЃЌlowerlгыlower2жЕОљЮЊ300(МДЯТЯо3.0ІИ)ЃЌЛљзМБШНЯжЕCЮЊ025(МДЕчзшВюжЕзюДѓЯоЖШЮЊ0.25)ЃЌВЩгУСљзщВЛЭЌЧјМфЪ§ОнзїЮЊВЩбљЪфШыЃЌЗТецНсЙћШчЭМ7ЫљЪОЁЃ ВЈаЮЯдЪОИУЫуЗЈЭъШЋе§ШЗЃЌЙІФмДяЕНЩшМЦвЊЧѓЁЃЮвУЧВЩгУAlteraЙЋЫОCycloneЯЕСаЕФEPlC3аОЦЌЃЌНјааFPGAЗТецЃЌВЂНЋЦфгІгУгкЪЕМЪЯЕЭГжаЃЌЭъШЋДяЕНдЄЦкаЇЙћЁЃЮЊСЫМьбщЯЕЭГЕФОЋШЗЖШЃЌВЩгУОЋУмЪ§зжЮЂХЗМЦНјаааЃбщЃЌИУвЧБэВтСПзМШЗЖШДя0.1ЃЅЃЌЗжБцТЪзюИпПЩДя1mІИЁЃ БОЮФЬсГіЕФЩшМЦЗНЗЈЃЌДгЪЕМЪгІгУРДПДЃЌНкЪЁСЫУцЛ§ПЊЯњЃЌвЧЦїЮШзМЖШИќИпЃЌЗДгІЫйЖШИќПьЃЌВЂЧвНЕЕЭСЫЯЕЭГећЬхЕчТЗЕФИДдгЖШЃЌЬсИпСЫЯЕЭГМЏГЩЖШЁЃОШэМўЗТецКЭЪЕМЪЙІФмбщжЄЃЎжЄУїЩшМЦПЩППЁЂЩшМЦЗНАИПЩааЃЌдкЪЕМЪгІгУжагаНЯДѓЕФЪЕгУМлжЕЁЃ |

ЭјгбЦРТл