S3C44B0X应用设计 - 存储器接口设计

发布时间:2010-9-13 13:46

发布者:techshare

|

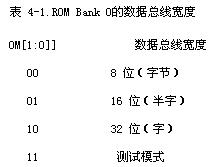

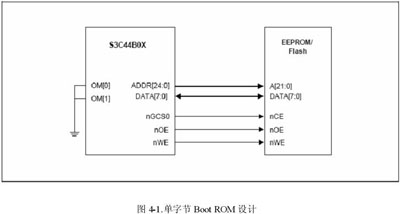

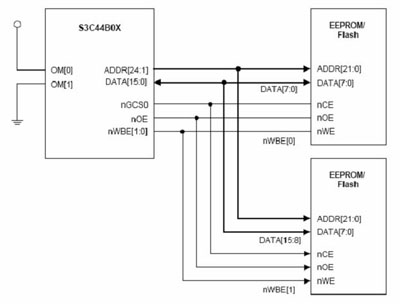

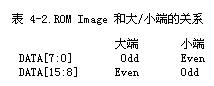

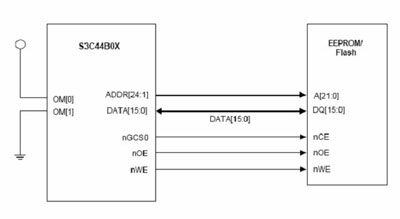

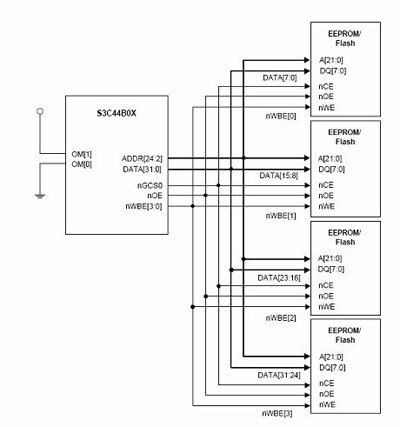

介 绍 三星的 S3C44B0X 16/32 位 RISC 处理器被设计来为手持设备等提供一个低成本高性能的方案。 S3C44B0X 提供以下配置: 2.5V ARM7TDMI 内核带有 8KB cache(高达 75MHZ 的 SAMBA总线结构) ; 可选的 internal SRAM; 外部储存控制器(FP/EDO/SDRAM 控制、片选逻辑); LCD Controller(最大支持 256 色 STN),带专用 DMA的 LCD 控制器(最大支持 256 色 DSTN); 两个通用的 DMA通道,两个带外部请求引脚的外围 DMA通道; 两个 UART/一个 SIO(IRDA1.0,16 字节的 FIFO); 一个多主控器的 IIC总线控制器和一个 IIS 总线控制器 l 5 个 PWM 定时器和一个内部定时器; 看门狗定时器; 71 位的通用 I/O 接口/8 个外部中断源; 电源控制:Normal,Slow,Idle 和 Stop 模式; 8 通道的 10位 ADC; 带日立功能的实时时钟(RTC); 片上带 PLL 的时钟发生器 因此,你可以用 S3C44B0X 做不同的系统 S3C44B0 的应用系统 如果你的产品需要接入网络,三星的带 16/32 位的 RISC S3C44B0X 微控制器可以降低你的成本,下面是一些系统可以用 S3C44B0X 设计。 l GPS 电话 l PDA(个人数字助理) l Fish Finder l 掌上游戏机 l 指纹识别系统 l TWM(Two Way Messaging) l 终端汽车导航系统 l MP3 播放机等等。 存储器接口设计 Boot ROM设计 当系统复位时,S3C44B0X 访问地址 0x00000000,在复位后 S3C44B0X 必须做一些系统变量的配置,因此这段特殊的代码(BOOT ROM 映像)应当位于地址为 0x00000000 处,启动 ROM 可以由不同宽度的数据总线,总线宽度是受 OM[1:0]引脚控制的。   编译和烧写一个字节的ROM映像 当编译一个字节的 ROM 映像,应当用来自编译和联接带到的二进制文件,用字节EEPROM/FLASH设计半字Boot ROM ,图 4-2 为用字节 EEPROM/FLASH设计的半字 BOOT ROM。  图 4-2 为用字节 EEPROM/FLASH设计的半字 BOOT ROM 编译和烧写用字节EEPROM/Flash 设计的半字ROM映像 当制作半字的 ROM 映像,可以分成两个文件 EVEN 和 ODD.。图 4-3 为用半字的 EEPROM/FLASH设计的半字 BOOT ROM。   图 4-3 为用半字的 EEPROM/FLASH设计的半字 BOOT ROM 用字EEPROM/FLASH 设计的字Boot ROM。  图 4-4 为用字节 EEPROM/Flash设计的字启动 ROM 编译和烧写用字节EEPROM/Flash 设计的字ROM映像,当你制作字 ROM 映像,可以分成四个映像文件。 |

网友评论