аТаЭD/AБфЛЛЦїAD9755МАЦфгІгУ

ЗЂВМЪБМфЃК2010-9-3 13:37

ЗЂВМепЃКtechshare

ЙиМќДЪЃК

AD9755

|

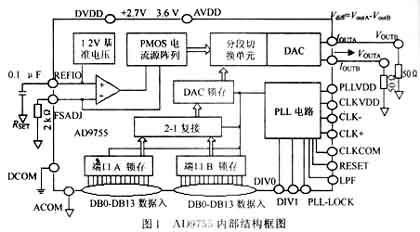

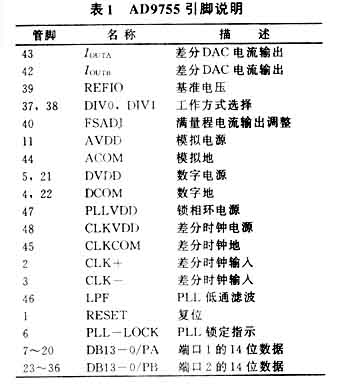

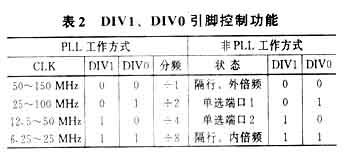

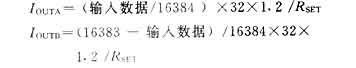

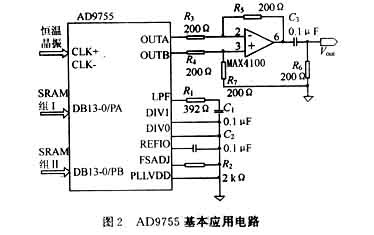

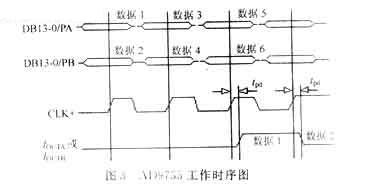

AD9755ЪЧAnalog DeviceЙЋЫОЩњВњЕФвЛжжГЌИпЫйЫЋЖЫЪ§ОнИДгУЁЂЕЅТЗЪфГіЕФ14ЮЛЪ§ФЃзЊЛЛаОЦЌЁЃВЩгУCMOSжЦдьЙЄвеЃЌдкЕЅИіаОЦЌЩЯМЏГЩСЫИпЦЗжЪ14-TxDAC+(r)КЫЁЂвЛИіЛљзМЕчбЙдДЁЂМцШнTTLЪ§зжНгПкЕчТЗЕЅдЊвдМАPPLЪБжгБфЦЕЦїЕШЁЃЫќЕФзЊЛЛЫйЖШКмИпЃЌПЩвдДяЕН300 Ms/sЁЃ ИУаОЦЌЖдЭтЮЇЕчТЗашЧѓЩйЃЌЩшМЦЪЙгУСщЛюЗНБуЁЃAD9755ЮЊБмУтЪЙгУИДдгЁЂИпФмКФЕФECLЕчТЗЃЌЖјжБНгРћгУTTLЪ§зжНгПкРДЭъГЩ300 MHzвдЯТЕФИпадФмЪ§УўзЊЛЛЃЌЬсЙЉСЫ1ЬѕЗЧГЃБуНнЕФЭООЖЁЃПЩЙуЗКгІгУгкЭЈаХЯЕЭГаХКХдДЁЂЪ§зжаХКХКЯГЩМАжЧФмвЧЦїжаЁЃЦфжївЊЬиЕуЮЊЃК (1)зЊЛЛЫйТЪ300 Ms/sЃЛ (2)ДЙжБЗжБцТЪ14 BЃЛ (3)ЙЄзїЕчбЙ3 VЃЛ (4)ЮодгЩЂЖЏЬЌЗЖЮЇ SFDRЮЊ73 dBc(Fout=50.2 MHz, fDATA=150 MHzЬѕМўЯТ)ЃЛ (5)ЪфШыНЈСЂЪБМф2.0 nsЃЛ (6)ЪфГіНЈСЂЪБМф11.0 nsЃЛ 1 AD9755ЕФЙЄзїдРэ AD9755жївЊгЩСНзщ14ЮЛЪ§ОнЪфШыНгПкЁЂ2-1ИДНгЦїЁЂDACЫјДцЦїЁЂЛљзМЕчбЙЁЂPMOSЕчСїдДеѓСаЁЂЗжЖЮЧаЛЛЦїЁЂPLLЕчТЗвдМАDACЕЅдЊЕШЙЙГЩЃЌЦфФкВПНсЙЙШчЭМ1ЫљЪОЁЃВЩгУ48еыLQFPЗтзАаЮЪНЃЌЭМжа2Иі14ЮЛМцШнTTLЕчЦНЪ§ОнЪфШыЖЫПкЃЌУПИіЖЫПкЕФзюДѓЪфШыЦЕТЪЪЧ150 MHzЃЌ2ТЗЪ§ОнСїдкЦЌФкЫјДцКѓЃЌО2-1ИДНгЦїКЯГЩЮЊ1ТЗ300 MHzВЂааЪ§ОнСїЃЌдйОDACЫјДцЦїЫјДцКѓДЋЪфЕНЗжЖЮЧаЛЛВПМўНјааДІРэЁЃ AD9755ФкжУСЫЛљзМЕчбЙдДЃЌЪЁШЅСЫГЃЙцИпОЋЖШDAзЊЛЛаОЦЌашвЊЭтНгЛљзМЕчбЙЦїМўЕФТщЗГЁЃЭМ1 жаЕФPMOSЕчСїдДеѓСаЪЧЮЊБЃжЄШЋСПГЬЪфГіЕчСїIЃЯЃеЃдЃЦЃгЖјЬиБ№ЩшМЦЕФЃЌIЃЯЃеЃдЃЦЃгЕФДѓаЁгЩФкВПЕФЛљзМПижЦЗХДѓЦїМАЭтЕчзшRЃгЃХЃдОіЖЈЁЃаОЦЌФкВЩгУСЫЗжЖЮНсЙЙЃЌМДНЋЪ§ОнЮЛЗжГЩзюИп5ЮЛЃЌжаМф4ЮЛКЭзюЕЭ5ЮЛЃЌЖдИїЖЮЕФЪ§ОнВЩгУВЛЭЌЕФЪ§УўзЊЛЛЗНЗЈЃЌвдБЃжЄЪ§УўзЊЛЛЕФОЋЖШЁЃЗжЖЮЧаЛЛВПМўНЋНгЪеЕНЕФPMOSЕчСїдДеѓСаЪфГіЕчСїЃЌКЭОDACЫјДцЦїЫјДцКУЕФ14ЮЛЪ§ОнвЛЦ№НјааЯрЙиДІРэКѓЃЌЪфЫЭжСФЉМЖЕФDACВПМўБуЪЕЯжСЫећИіЪ§ФЃзЊЛЛЙ§ГЬЁЃ  AD9755гаЪЙгУЫјЯрЛЗЃЈPLLЃЉКЭВЛЪЙгУЫјЯрЛЗСНжжЙЄзїЗНЪНЃЌШЁОігкPLLVDDНХНгЕчдДЛђЕиЁЃЕБЪфШыЪБжгЕФеМПеБШВЛЪЧ50%ЪБЃЌПЩЪЙгУPLLЙЄзїЗНЪНЁЃPLLЕчТЗФкВПЕФVCOПЩаЮГЩ100"400 MHzЕФжмЦкаХКХЃЌгУЛЇЭЈЙ§ЩшЖЈDIV0ЁЂDIV1НХРДОіЖЈИУжмЦкаХКХЕФЗжЦЕЕШМЖЃЈШчБэ2ЫљЪОЃЉЁЃPLLдкЖдИУЗжЦЕаХКХКЭЭтВПЪфШыЪБжгНјааЯрЮЛМьВтКѓЃЌгыЫјЯрЛЗТЗвЛЦ№РДЭъГЩЪБжгЦЕТЪЕФЫјЖЈЁЃЕБВЛЪЙгУЫјЯрЛЗЪБЃЌ DIV0ЁЂDIV1НХОіЖЈСЫШчБэ2ЫљЪОЕФ4жжЙЄзїзДЬЌЁЃдкИєааЁЂЭтБЖЦЕЗНЪНЯТЃЌЭтВПЪБжггІЪЧЪфШыЪ§ОнТЪЕФСНБЖЃЛдкЕЅбЁ1ЃЈЛђ2ЃЉЖЫПкЗНЪНЃЈМДжЛЭъГЩ1ТЗDAБфЛЛЪБЃЉЃЌвдМАдкИєааЁЂФкБЖЦЕЗНЪНЪБЭтВПЪБжггІЩшжУГЩгыЪфШыЪ§ОнТЪЯрвЛжТЁЃ   AD9755ЬсЙЉСЫ1ЖдЛЅВЙЕчСїЪфГіIЃЯЃеЃдЃС,IЃЯЃеЃдЃТ,ЫќУЧЖМЪЧЪфШыЪ§ОнЕФКЏЪ§ЃЌПЩБэЪОЮЊЃК  ШчЭМ1ЫљЪОЃЌIЃЯЃеЃдЃС,IЃЯЃеЃдЃТ,ПЩжБНггЩ50 ІИЕчзш(зюКУЪЙгУгаСМКУЮТЖШЬиадЕФОЋУмЕчзш)НгЕНФЃФтЕиЁЃзюжеЕФВюЗжЪфГіЕчбЙжЕЮЊЃКЃЈIЃЯЃеЃдЃС-IЃЯЃеЃдЃТЃЉЁС50ЁЃ 2 гІгУЩшМЦ ЯТУцИјГівЛИівдAD9755зїЮЊЪ§ФЃзЊЛЛЦїРДВњЩњШЮвтВЈаЮЕФЪЕР§ЁЃЪзЯШдкPCЛњЩЯНјааВЈаЮБрМЃЌОпЬхЗНЪНПЩвдЪЧБэвГЪфШыЁЂЪ§бЇБэДяЪНЛђЭЈЙ§ЪѓБъЛцжЦЭМаЮЁЃгЩШэМўбЁдёе§ЯвВЈЁЂЭЈгУКЏЪ§ЛђЮБЫцЛњдыЩљЕШЃЌВЂЩшЖЈаХКХЕФЗљЖШЁЂЦЕТЪЁЂЦЋжУСПЃЌдйОПьЫйбнЫуЕУЕНВЈаЮЪ§ОнЁЃВЈаЮЪ§ОнОPCIПЈаДШыЕНСНзщДѓШнСПSRAMЦїМўЃЈIDT71V3558ЃЌзюИпЙЄзїЦЕТЪ200 MHzЃЉКѓЃЌЕШД§ЩЯВуЯЕЭГЕФDAЦєЖЏУќСюЁЃ DAЦєЖЏКѓЃЌгЩISPаОЦЌЃЈisp2128VE,зюИпЙЄзїЦЕТЪ250 MHzЃЉаЮГЩ75 MHzЕФИпЫйЕижЗЃЌЧ§ЪЙЫЋТЗSRAMЪ§ОнСЌајВЂааЪфГіЁЃетСНТЗЪфГіЕФЪ§ОнЗжБ№ЪфЫЭжСAD9755ЕФЪ§ОнЖЫПк1КЭЪ§ОнЖЫПк2ЁЃгЩгкЯЕЭГВЩгУСЫИпадФмЕФ150 MHzКуЮТОЇеёЃЌвђДЫAD9755ЕФЙЄзїЗНЪНМђЕЅЩшЖЈЮЊВЛЪЙгУЫјЯрЛЗЕФИєааЁЂЭтБЖЦЕЗНЪНЃЌгІгУЕчТЗЭМШчЭМ2ЫљЪОЁЃ  жЕЕУжИГіЕФЪЧЃЌAD9755газХБШНЯСщЛюЕФЪБжгНгШыЗНЪНЁЃПЩвдЪЧВюЗжНгШыЃЌвВПЩвдЪЧЕЅЖЫНгШыЃЌЩѕжСПЩвджБНгЪЙгУVЃаЃЃадк1 VвдЩЯЕФе§ЯвВЈЃЌВЛЭЌЕФНгШыЗНЪНгІЪЙгУгыжЎЯрЪЪгІЕФТЫВЈЭјТчЁЃЖјЖдгкЪфГіаХКХвЊЧѓМЋЮЊбЯИёЕФгІгУГЁКЯЃЌЮЊСЫдкЪфГіаХКХЩЯгааЇвжжЦдгЩЂЕчЦНКЭЯћГ§ЯрЮЛдыЩљЃЌЪБжгЭЌВНЕФДІРэвЫбЁгУЗзЊЫйЖШБШНЯКУЕФИпадФмЦїМўЃЛвдБЃжЄаХКХЕФБпбиЖИЧЭЁЂЧАКѓЖЖЖЏзюаЁЁЃ ЭМ3ИјГіСЫAD9755ЕФЙЄзїЪБађЭМЁЃгЩгкЪфШыЪ§ОнЖЫПкЫјДцМАDACЫјДцЖМЗЂЩњдкCLKЕФЩЯЩ§биЃЌЮЊСЫБЃжЄзуЙЛЕФЪ§ОнНЈСЂЪБМфКЭЪ§ОнЕФе§ШЗадЃЌСНИі14ЮЛЪ§ОнЖЫПкЪ§ОнЕФБфЛЏзюКУдкCLKЕФЯТНЕбиЭъГЩЁЃDACЕФБфЛЏЪБМфГіЯждкЕк3ИіЪБжгжмЦкЩЯЃЌВЂга1ИіtЃаЃФаЁгк1nsЕФДЋВЅбгГйЁЃВЛФбПДГіЃЌAD9755ЕФЙЄзїЪБжге§КУЪЧЪ§ОнБфЛЏТЪЕФ2БЖЃЌвРДЮЭъГЩСЫ2ИіЪ§ОнЭЈЕРЕФНЛЬцЪ§ФЃзЊЛЛЁЃSRAMзщЂёДцЗХЕФЪЧШЮвтВЈаЮЕФЦцЪ§ЕуЪ§ОнЃЌЖјSRAMзщЂђДцЗХЕФЪЧВЈаЮЕФХМЪ§ЕуЪ§ОнЃЌIЃЯЃеЃдЃСЛђIЃЯЃеЃдЃТЩЯЗДгГЕФЪЧгыдЪ§ОнЫГађвЛжТЕФDACЁЃ  гЩгкШЮвтВЈаЮЕФЦЕТЪГЩЗжвьГЃЗсИЛЃЌЙВФЃдыЩљМАИпДЮаГВЈЕФГіЯжВЛПЩБмУтЕиЛсНЕЕЭЪфГіаХКХжЪСПЁЃЮЊСЫИФЩЦDAБфЛЛЕФЯпадЖШЃЌзюДѓГЬЖШЕивжжЦЪЇецгыдыЩљЃЌВЂЬсИпаХКХдДЕФИКдиФмСІЃЌЭМ2жаЕФЪфГіЗНЗЈгыЭМ1жажБНгСЌ50ІИЕНФЃФтЕиЕФЗНЗЈВЛЭЌЃЌМДв§ШыСЫПэДјдЫЗХMAX4100(ДјПэЮЊ500MHz)ЁЃ зюКѓашвЊЧПЕїЕФЪЧЃЌИпЫйTTLЪ§зжЕчТЗЁЂИпЫйФЃФтЕчТЗЃЌвВгІКЭECLЕчТЗвЊЧѓвЛбљЃЌЭЈЙ§зшПЙЦЅХфРДПЫЗўаХКХЕФЙ§Гхе№ЕДЁЃАДееДЋЪфЯпРэТлРДЩшМЦКУДјЯпКЭЮЂДјЯпЃЌPCBСЌЯпЕФзшПЙжЕгыЕчТЗАхЭВКёЖШЁЂАхВужЎМфЬюГфНщжЪВФСЯМАЦфИпЖШЯрЙиЃЌМЦЫуАьЗЈВЮМћЮФЯз2ЁЃбЁгУСЫЖрВужЦАхЃЌШЗЖЈЕчТЗАхВуЪ§ЕФИљОнЪЧЃКNL=5logЃлAЃюЃцЃУЃЬЃЫЃнЁЃЦфжаЃЌAЃюЮЊЪ§ОнзмЯпПэЖШЃЌЃцЃУЃЬЃЫЮЊзюИпЙЄзїЦЕТЪЁЃ |

ЭјгбЦРТл