用创新的技术侦测及找出混合信号设计中的问题

发布时间:2010-9-1 09:02

发布者:techshare

|

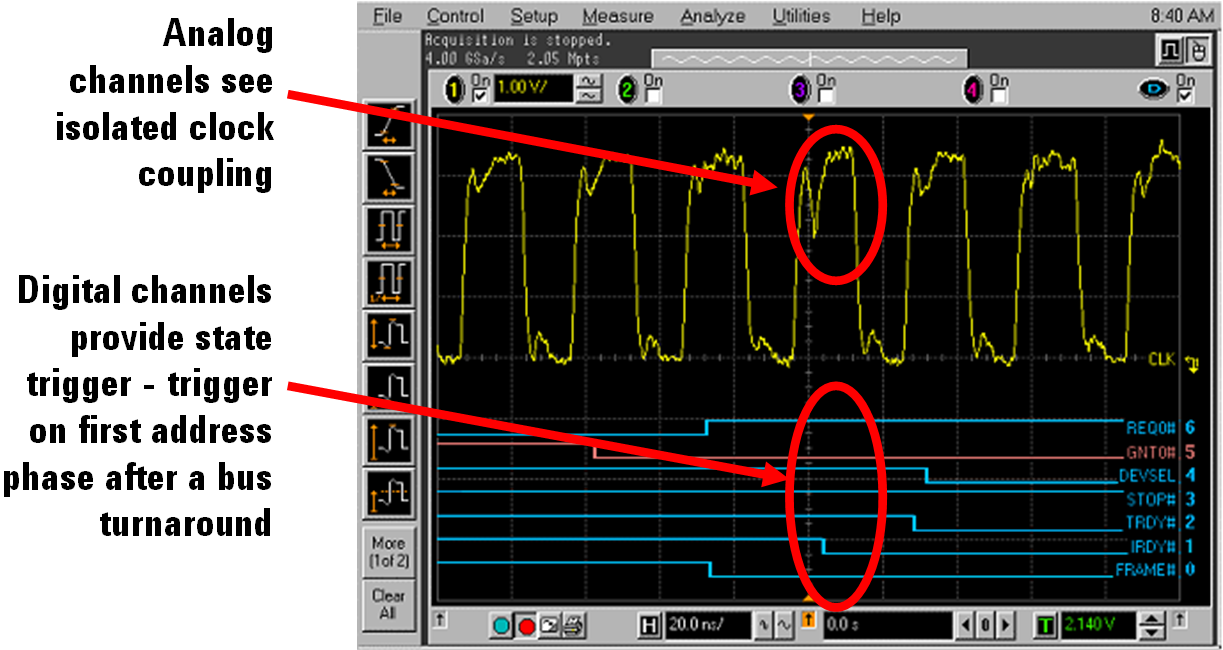

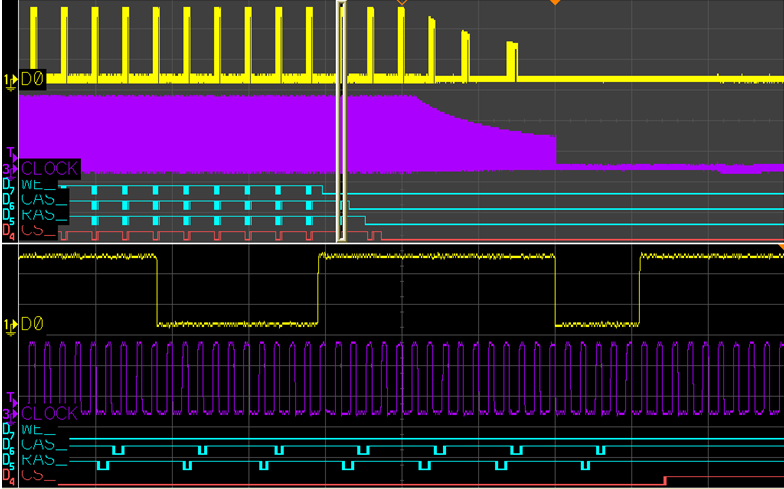

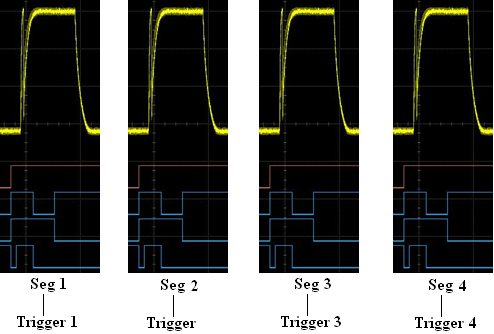

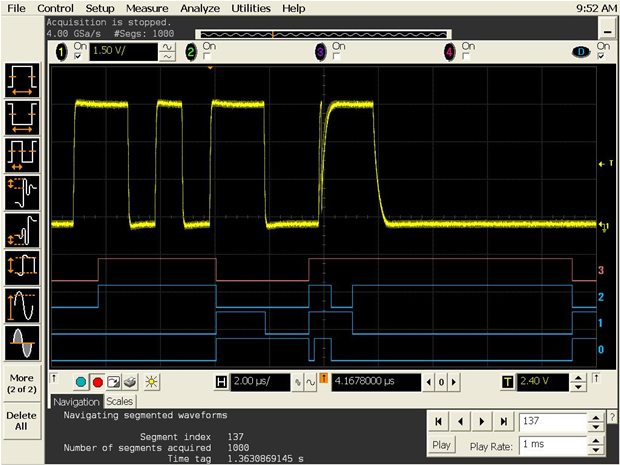

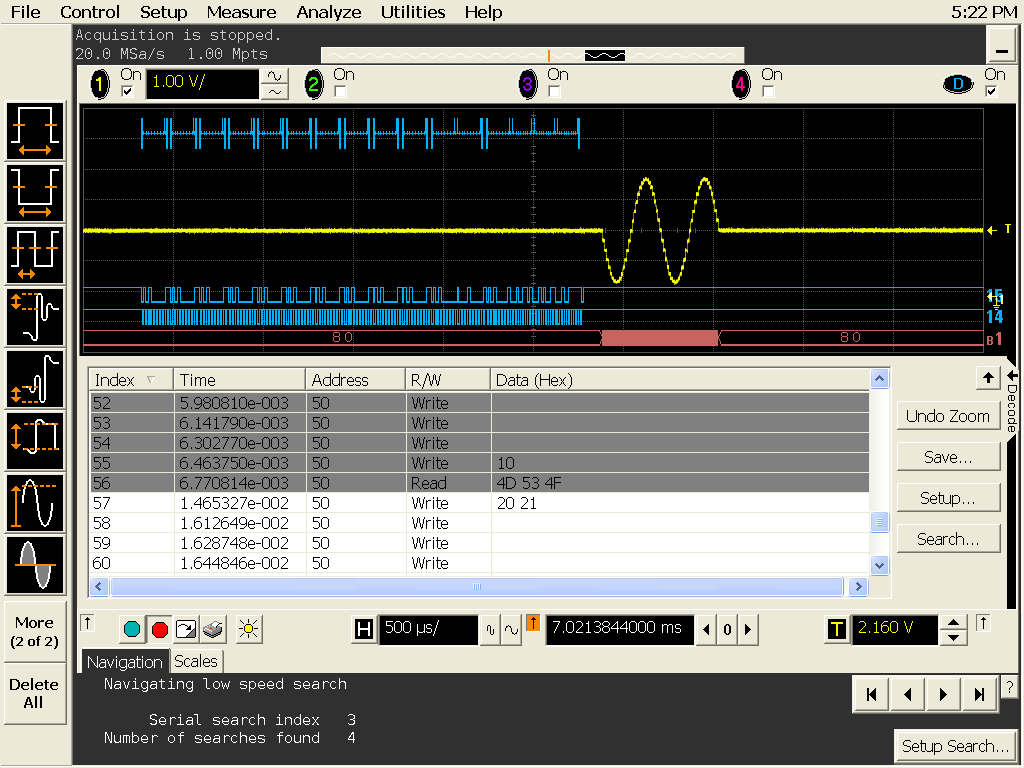

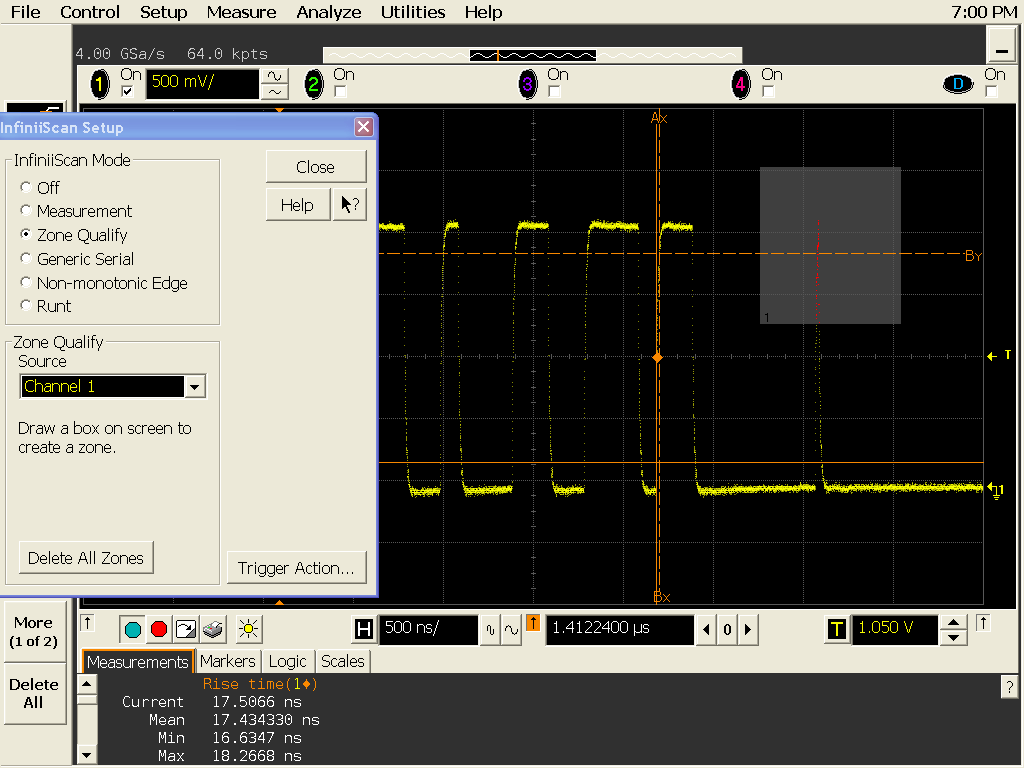

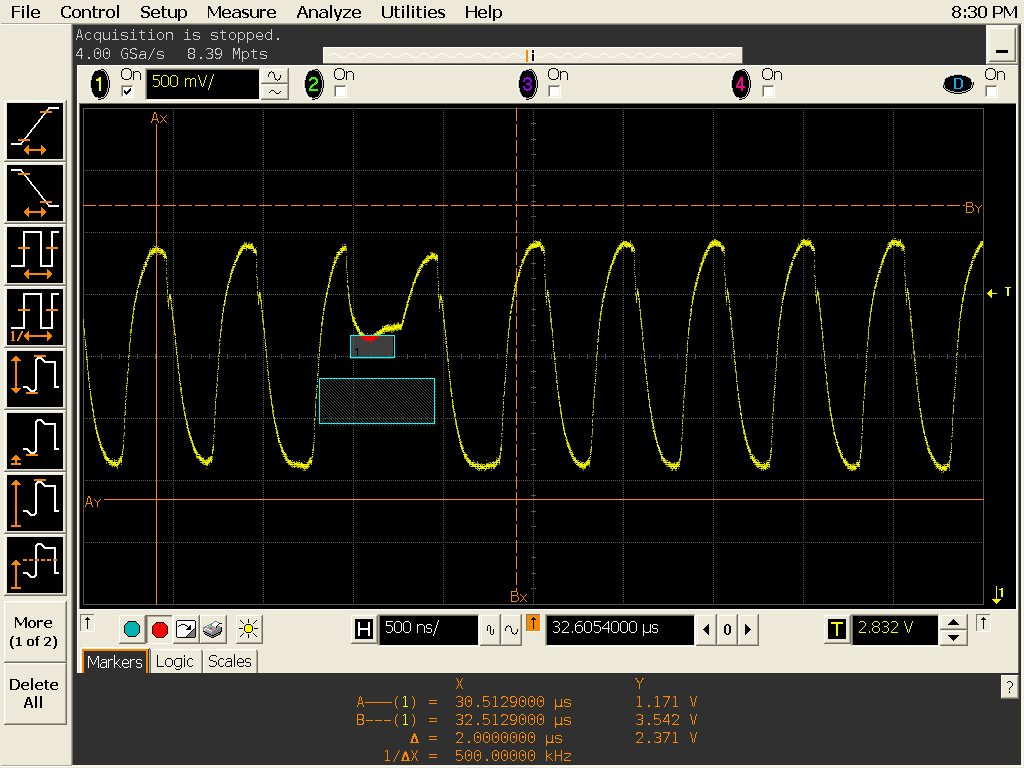

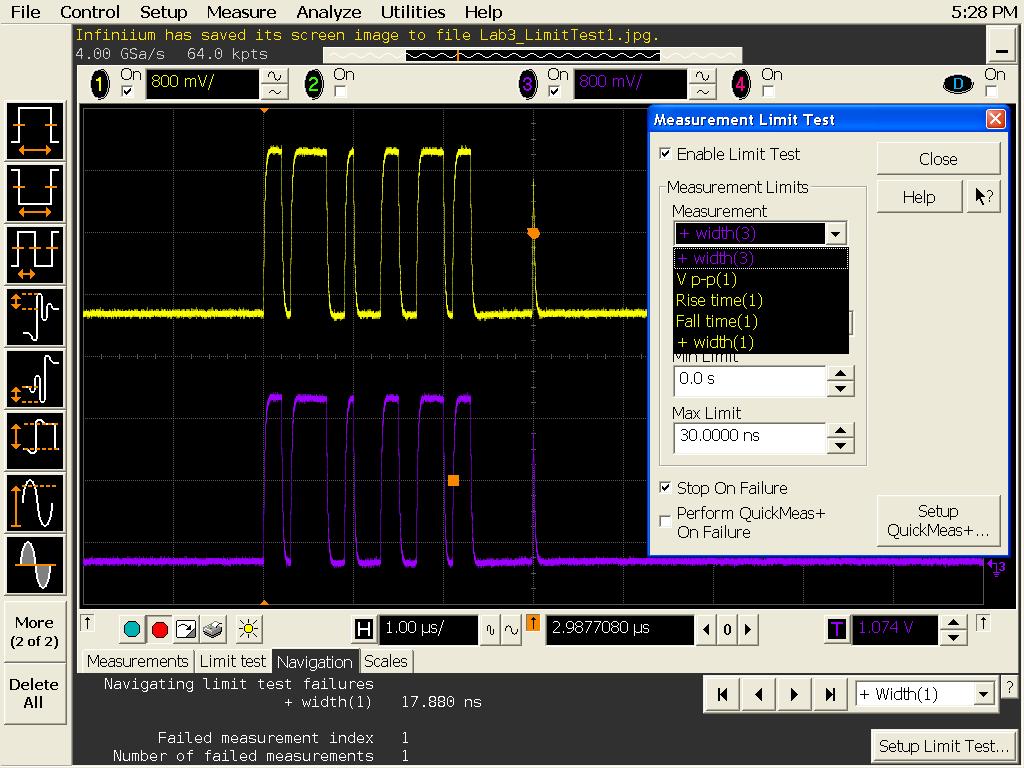

据产业消息来源的估计,目前大约有百分之七十的电子工程师所从事的设计都大量混合了模拟和数字信号的成份,因此,设计人员愈来愈需要具备能够将设计内的模拟和数字器件或芯片间的信号时间相互关联的能力。此外,高速的数字信号更加需要深入测量其信号质量,因为这攸关信号完整性的容限大小(signal integrity margin)。针对特定的测量选择合适的测试设备时,有效性、效率、以及价格/性能比是最主要的考虑因素。Johnnie Hancock在一篇标题为「运用MSO混合信号示波器侦测及找出嵌入式混合信号设计的问题」的应用文章中,探讨了选择测试设备时,需要考虑的主要因素,包括:通道数、带宽、采样率、以及MSO混合信号示波器(如安捷伦科技的MSO6000系列示波器)具备的各种类型的混合信号触发能力。本文将介绍一个更先进的产品所提供的独特价值,那就是新近推出的MSO8000系列混合信号示波器。我们将为读者说明MSO8000支持的一些独特功能,这些功能可以协助使用者找出各种信号问题,这是其它测量解决方案,例如传统「数字示波器加上逻辑分析仪的组合」,所无法取代的。 找出死锁问题的根本原因 安捷伦科技的工程团队最近在设计一块新的数据采集电路板(acquisition board)时,遭遇到一个难缠的问题,这块板子一般时候都可以正常运作,但偶而却会死机。团队人员利用Windows debugger确定了造成死锁(lock-up)的原因是:有一个 “配置写入”周期有时候无法收到确认信号。他们修改固化软件,重复“配置写入”,将死锁情形的出现频率由每隔几小时提高到每隔几分钟出现一次。图1a显示了利用MSO8104A示波器的状态触发能力,在总线信号处理权交还给CPU后,第一次开始寻址那一时刻的结果。由图中可以看出与时钟信号有关的一个异常的电压跌落,这是因相邻地址线的电容耦合所造成的。在图1b中可以看出,在较长的时基范围下检视这些信号,当电路进入死锁的状态时,系统中一些周期性出现的信号会停止改变状态, ,设计团队运用示波器的“逾时”(time-out)触发能力,成功隔离出死锁的状况,并依据逻辑信道在死锁的状态,找出了时序的问题。  图1a  图1b 重要事件的出现频率 在图1a所示的例子中,出现系统死锁情形的概率/频率非常低 -大约每2到8小时才出现一次。此处需要设想的问题是:如果工程师无法利用debugger将问题复制出来怎么办?我们要如何确定该问题与“配置写入”周期之外的其它总线周期无关呢?所幸,安捷伦科技的MSO8000系列示波器提供了一个称为“分段式存储”(segmented memory)的先进功能,可透过优化调整示波器存储器的设置和重新预准备(re-arm)时间,让该特定总线周期只要一出现,示波器就把它捕获下来,可以连续捕获数千个该特定动作对应的总线周期信号,图2a显示的就是一个例子。  图2a  图2b MSO混合信号示波器的模拟信道和数字信道的采集存储器可被分为许多段,当示波器的触发条件第一次出现的时候,波形数据会被填入第一段的存储器,当触发条件第二次出现时,则会填入第二段的存储器,依此类推。在图2b显示的例子中,利用示波器的分段式存储器采集模式,依序采集到出现了1000次的重要事件。事实上,利用MSO8000的采集存储器(示波器通道选件深达128 M,逻辑信道是标配每信道32M),最多可以采集32,000段的波形。在采集到指定的区段数之后,可以使用荧屏右下方的浏览控制键,轻易地逐一回放每个区段,以便清楚地查看信号异常是否只与示波器的逻辑信道所采集到的一个重要时序事件有关,或是DUT还有其它关键的总线动作也会造成信号异常的现象?分段式存储器采集模式同时支持示波器信道和逻辑信道,对内嵌式系统设计的除错有很大的帮助,因为这种设计大多是以状态机(state machine)为主,您可以透过逻辑信道来设定触发条件,观察每一个状态的信号行为。 浏览控制功能不仅在使用分段式存储器采集模式时可以使用,而且在串行总线译码模式下也可以使用。图3所示为I2C总线的信号,与译码窗口内的信号是时间相互关联的。虽然I2C不是一种高速的串行总线,而且就这种低速总线的时钟与数据信号而言,信号完整性的问题可能也不是主要的考虑点,但是利用这种通讯信号进行触发,并且让示波器同步进行采集,或许可以揭露出系统中其它时间相互关联之模拟和/或高速数字信号的信号完整性问题。在某些情况下,我们可能会知道待测信号或许会出现问题,但却不知道何时会发生问题,或是问题跟哪个信号有关。在串行总线译码功能的协助下,示波器可以显示出图3a中的情形:只有当一个特定的I2C读取动作发生时,才会出现一个双周期的雷达chirp输出信号。您可以浏览译码列表窗口中的每一个读取动作,以验证该特定的事件(其它相关信号)是否有发生。这个概念与FPGA的除错方式很类似,安捷伦科技的MSO8000支持Xilinx FPGA内部节点自动切换和测试,可以将FPGA内部节点(> 1000个多个待切换测试的节点)与外部信号的时间相互关联来显示和分析(这个主题不在这篇文章的讨论范围内)。一旦工程师知道这些问题何时会发生,以及问题与哪个信号和/或总线周期相关联之后,通常就可以快速地解决设计的问题。  图3 InfiniiScan = 问题找寻工具 很多时候,想要找出设计中的串行接口与并行总线的潜在问题是相当耗费时间的事情,特别是当问题出现地相当随机和/或出现的频率不高时。设计工程师有时候会修改固化软件(韧体/HDL),让系统进入一种特殊的反复循环来试着复现问题,也就是藉由强迫出现特定条件的方式,让问题比较容易出现,如前所述。但即使采用这种方法,如果手上没有创新设计的利器,有时候依然很难隔离和找出问题点。  图4a  图 4b 您在设计时可能会碰到许多不同类型的信号问题,例如设定(set up)和保持(hold)时间违规、过多的过冲与振铃(ringing)问题、随机出现的毛刺、甚至是可能在不对的时间不对的空间出现不该有的脉冲信号等。要找出这些问题可能会有一定的难度,特别是如果问题不常出现或如果您不知道发生的原因时,又会更加地困难。安捷伦科技的MSO8000系列示波器最近推出了一项称为“InfiniiScan”的新功能,可协助找出各种信号问题 -如信号出现在不该出现的地方、或是该出现时却没有出现的问题。举例来说,图4a显示的丛发脉冲串就是在最后一个完全传送的比特(位)之后,原本不应该再出现脉冲,却又跑出一个脉冲信号的情形,如图4a所示,在最后一个比特(位)之后大约600 ns的地方,有时候会随机出现一个突波。此时您可以使用鼠标(或是用您的手指在触控式荧屏上操作),在不应该出现信号的范围拉出一个“方框”,告诉示波器如果其显示屏的这个方形区域/范围内出现信号异常状况/脉冲时,就停止反复采集的动作,或是只显示出有问题的状况,接下来示波器就只会显示含有问题脉冲的采集画面了。 图4b所示为一个时钟信号的问题,其中的压降造成一个错误的时钟脉冲。为了采集这个特殊的问题,我们利用InfiniiScan设定了一个双区域的扫描范围,第一个区域定义为“信号必须通过” 的范围,第二个区域则定义为“信号不可通过” 的范围。 除了指定必须通过/不可通过的“范围”组合之外,InfiniiScan也可以设定为只显示包含”指定之合格和/或不合格参数量测结果”的采集画面。图5 是一个设定示波器来同时监测五组量测的例子,当任何一组参数量测的结果超过了指定的限制范围时,就会将波形存储下来或停止波形采集。接下来,您还可以运用 InfiniiScan的浏览控制功能,轻松地在“不符合限制测试条件” 的波形上扫视任何位置的波形,查看信号的细节。  图5 高阶的应用:LA+DSO或 LA+MSO? 大部分的MCU和DSP内部都有地址和数据线,因此通常由外部无法监测这些地址和数据线。大部分内嵌了MCU/DSP的设计中需要监测的外部信号一般会包括数字I/O(每个通常最多8位)、控制线、串行总线线(如I2C或SPI)、以及一些模拟I/O信号(如A/D、D/A和传感器的输入信号)。不论 MCU/DSP 本身是多少位(8、16或32位),使用4+16信道的MSO混合信号示波器来检视这些类型的信号都相当合适不过。然而,对某些需要的通道数超过20个的高阶应用来说,例如有外部总线的微处理器系统,或许需要考虑使用时间相互关联的双机解决方案:逻辑分析仪+示波器。LA+DSO/MSO解决方案的主要优点之一是示波器信道和逻辑分析仪信道之间的时间可以相互关联,不仅是模拟和数字波形的时间是相互关联的,而且两部仪器之间的时序光标也可以相互关联(如使用安捷伦的逻辑分析仪和示波器组合方案),这表示无论您将逻辑分析仪显示屏上的时序光标移到什么地方,示波器上相关联的时序光标也会移到同一个时间关联的位置。这虽是一项简单的功能,但除非您使用的是安捷伦科技的DSO/MSO+逻辑分析仪,否则目前市面上所有的LA+DSO解决方案都无法提供这样的功能。 由于MSO和逻辑分析仪都能提供多个逻辑采集信道,您可能会直觉地认为将MSO和逻辑分析仪的时间相互关联是多余的,但事实上,当您需要较多的通道时,MSO+LA通常才是最佳的解决方案(相较于DSO+LA),主要的原因在于MSO的许多功能都无法由“DSO+LA”的组合来取代。虽然使用时间上相互关联的DSO+LA,可以让您在同一个荧屏(LA的荧屏)上显示所有的示波器波形和逻辑波形,但不幸的是,您将无法看到“活生生”、实时更新的显示画面(逻辑信道和示波器信道在一个屏幕上同时更新)。做为一种除错工具,波形更新速率是非常重要的,会影响您能否揭露出设计中隐藏的问题,另外一个实际例子是,若要观察DDR信号的读眼图或写眼图,您必须同时连接时钟信号、片选信号、写使能、行选、列选并它们状态设置成和读操作或写操作,同时用示波器的某个通道观察数据信号的眼图,该测量一方面需要快速波形更新率,另一方面要求逻辑通道的触发抖动很小,这两点都是“DSO+LA”组合方案无法做到的。此外,安捷伦科技的MSO也是唯一可以同时对示波器信道和逻辑信道同时进行触发条件设定的(混合信号触发)工具。最后,如果20个混合模拟和数字信号的采集信道对您的应用大部分时间来说已经够用了,那么MSO就可以做为您主要的首选工具,而不一定要将两部仪器合在一起,换句话说,您大部分的应用只要使用MSO就够了,唯有在必要时,才需结合MSO和逻辑分析仪,这时利用两台仪器的全局光标功能时间相关地同屏或分屏显示和分析信号。 结语 当您考虑要购买下一部测试设备,以测试混合信号的设计时,了解不同解决方案的独特价值将能协助您做出正确的选择。安捷伦科技建议使用MSO或MSO+LA 的解决方案(视您的预算和量测需求而定),这样就足以协助您既有效又有效率地找出和解决各种问题了。安捷伦科技的MSO8000不仅是一部混合信号示波器,也是一套可以协助您找出许多电路问题根本原因的工具。 |

网友评论