高频锁相环的可测性设计

发布时间:2010-8-30 15:09

发布者:techshare

|

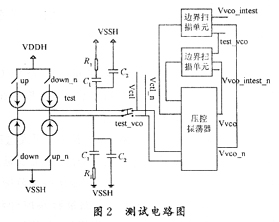

可测性设计(Design for Test,DFT)最早用于数字电路设计。随着模拟电路的发展和芯片 集成度的提高,单芯片数模混合系统应运而生,混合电路测试,尤其是混合电路中模拟电路的测试,引起了设计者的广泛关注。边界扫描是数字电路可测性设计中常用的技术,基于IE EE11491边界扫描技术。本文针对一款应用于大规模集成电路的CMOS高频锁相环时钟发生器,提出了一种可行的测试方案,重点讲述了锁相环的输出频率和锁定时间参数的测试,给出了具体的测试电路和测试方法。对于应用在大规模电路系统中的锁相环模块,该测试方案既可用于锁相环的性能评测,也可用于锁相环的生产测试。 1 锁相环结构及原理 本文所要测试的是用于大规模集成电路的锁相环时钟发生器,他是一款基于0.18 μm CMOS 数字工艺设计的高频电荷泵锁相环(Charge Pump Phase Locking Loop,CPPLL),最高输出频率达1.2 GHz。 此锁相环的电路结构如图1所示,他包括输入分频器、鉴频鉴相器(Phase Frequency Detec t,PFD)、电荷泵(Charge Pump,CP)、压控振荡器(Voltage Controlled Oscillator, VCO)、环路低通滤波器(Lowpass Filter,LPF)和反馈分频器等基本单元。输入信号经过输入分频器分频为参考信号,压控振荡器的输出信号经过反馈分频器分频为反馈信号;参考信号和反馈信号在鉴频鉴相器中进行相位比较,得到相位差信号;电荷泵和低通滤波器将相位差信号转换为相应的电平信号;该电平信号控制压控振荡器的输出频率。通过反馈环路,最终达到相位锁定。锁定状态时,参考信号和反馈信号同频同相。 为了更好地抑制噪声,锁相环采用了差分的电路结构。其中,压控振荡器采用环形振荡器结 构实现,主要由3个完全相同的延迟单元顺次连接而成。 2 测试方案 模拟电路传统的测试方法比较简单,将输入输出信号直接引出,检测输入信号对应的输出响 应即可。随着工作频率的升高,封装管脚和引线寄生参数不容忽视,传统的测试方法也受到挑战。由于模拟信号的抗干扰能力差,轻微的扰动都可能会影响电路的性能,测试电路应该尽量简单,以避免引入不必要的噪声。 最高输出频率、输出频率范围和锁定时间等都是高频锁相环需要测试的重要性能参数。对于工作频率高达GHz的高频锁相环,显然难以采用传统的测试方法来完成,需要进行专用测试电路设计,即在芯片内设计一定的测试电路以便投片后进行测试。 2.1 输出频率测试 作为时钟发生器,锁相环一般工作于整个电路系统的最高频率,而压控振荡器工作于锁相环的最高频率。如图1所示,锁相环的输出频率就是压控振荡器的工作频率,因此锁相环的输出频率测试实质上是对压控振荡器的最高振荡频率和振荡范围的测试。 由于输出管脚的引线存在寄生的电感电容,这些寄生参数容易引入较大的高频耦合噪声;高频信号经过这些引线输出到管脚通常会产生较大的衰减。因此,压控振荡器的高频输出信号很难引出芯片外直接测量。另一方面,高频信号的测试对测量仪器要求很高,测试板上的外加信号一旦经过高频通路耦合到电路内部,就会影响测试结果,甚至干扰电路的工作。 一种简单的测试方法就是将输出频率分频,通过测量分频后的频率fout推算VC O的振荡频率。这种分频器测试方法比较简单,只需要在VCO的输出端增加输出分频器,检测降频后的信号频率,即可由公式: 推算出VCO的振荡频率。式中N为输出分频器的分频值。 按照分频测试的方法来测试,每次都必须在锁相环达到稳定的锁定状态时才能测量。GHz高 频锁相环的锁定时间一般为微秒量级,于是锁相环的频率测量通常需要几毫秒。对于电路 测试来说,这是一个相对较长的时间。更为理想的测试方法是尽量采用简单的硬件资源,在 不影响电路性能的情况下,在较短的测试时间内完成测试。 边界扫描是目前大规模集成电路中常用的测试方法。IEEE1149?1规范了边界扫描方法和指 令。基于集成电路中常见的边界扫描单元电路,本文将介绍一种边界扫描的测试方 案来测试锁相环。 如前所述,要测试的锁相环采用了环形VCO振荡器,环形VCO的振荡频率与其延时存在如下关系: 其中:Tdelay是环形振荡器的延迟时间;fvco是VCO的振荡频率。采用边界扫描电路测量出VCO模块的延迟Tdelay,进而计算振荡器的工作频率。 VCO的输出频率受控制电压的控制,可通过改变控制电压的大小并检测每个控制电压对应的VCO延迟,利用式(2)计算输出频率,最后得到输出频率范围。 这种方案将闭环电路的频率测量转换成开环电路的延迟测量(通常该延迟为纳秒量级),时间 的节省将非常可观。同时,已经成熟的边界扫描技术,并不会增加太大的设计难度和测试复杂度,对设计者和测试者来说,只需遵照一定的规范完成即可。采用标准的边界扫描单元,硬件的开销也不大。对大规模集成电路中的锁相环电路,采用边界扫描测试方案显然优于前一种分频测试方案。 2.2 锁定时间测试 锁相环的锁定时间是锁相环的重要指标。如何判断锁相环已经达到锁定状态以及锁定时间的计算也是锁相环要测试的内容。 根据锁相环的原理,锁相环的重要功能就是锁定相位。电路锁定时,鉴频鉴相器的2个输入信号:参考信号和反馈信号相差为0,鉴频鉴相器输出无效电平,电荷泵开关处于开启状态,VCO的控制电压保持恒定。因此,参考信号和反馈信号、鉴频鉴相器的输出信号、VCO的控制电压等都可以作为电路锁定的判别依据。本文选取了VCO的控制电压作为判断依据,当VCO的控制电压稳定时,锁相环就达到锁定状态。锁定时间即电路从失锁状态到锁定状态的时间,VCO的控制电压从最初的不稳定状态到稳定状态的时间差就是锁相环的锁定时间。 3 测试电路实现 3.1 测试电路 按照边界扫描测试方案设计的测试电路如图2所示。针对差分结构锁相环,在电路中相应地 采用了2个边界扫描单元。边界扫描单元用于检测VCO的延迟,根据该延迟可推算VCO的振荡频率。利用VCO的2个控制信号Vctl和Vctl_n可以完成输出频率范围和锁定时间的测试。 在压控振荡器的控制信号处设置开关,开关闭合时,锁相环处于正常工作模式;开关打开时 ,锁相环处于测试模式。在测试模式时,Vctl和Vctl_n是输入信号,控制VCO的振荡频率,同时利用边界扫描单元测量振荡频率,调整输入控制电压的大小,就能测量VCO的振荡频率范围。正常工作模式时,Vctl和Vctl_n是输出信号,其电压值就是电路正常工作时VCO的控制电压,测量该信号就能推算锁相环实际的输出频率大小和范围。 锁定时间的测试必须要求电路完成锁定过程才能测量,因而相对较慢。在电路正常工作时, VCO的控制信号Vctl和Vctl_n是输出信号,观察该信号是否稳定就能判断环路是否达到锁定状态。测量控制信号从不稳定到稳定的时间差就是锁相环的锁定时间。 3.2 边界扫描电路 边界扫描单元电路如图3所示。Vvco是VCO的输出信号,Vvco_intest是边界扫描的测试矢量输入,test_vco是VCO的测试模式选择信号,shift_DR,clk_DR,update_DR都是边界扫描单元要求的时钟或控制信号。这些信号与集成电路中的边界扫描控制信号配合使用即可。相应另一个边界扫描单元的信号也与此类似,只是VCO的输入输出取相反信号。   锁相环正常工作时,边界扫描只相当于一条连线;在测试模式时,VCO的振荡环路被打开, 测试信号从边界扫描电路输入,经过VCO后再从输出端输出,检测这些信号在VCO内部的延迟 Tdelay,就能推算出VCO的振荡频率。该延迟是VCO控制电压的函数,扫描控制电压的值就可得到VCO的工作频率和振荡范围。 边界扫描单元的工作用IEEE1149.1标准中的Intest指令来完成。Intest指令借助于一个测试矢量来进行内部扫描测试。一旦该指令被装载到指令寄存器,测试矢量信号(VCO的输入信号Vvco_intest 和Vvco_intest_n)就被存储于边界扫描单元中的扫描寄存器,经过各级延迟在VCO输出端输出。  4 仿真结果 理想的测试电路既可以有效地测试电路性能又不影响电路的正常工作。锁相环作为时钟发 生器,需要给大规模电路提供稳定的时钟信号,因此影响锁相环性能的测试方案是不可取的。 为了检测本文所述的边界扫描测试方案的有效性,对增加测试电路前后的锁相环电路网表分别进行了Hspice仿真,如图4所示的波形是增加测试电路前后锁定时锁相环的输出波形图。 由图4看到,对1 GHz的高频输出,增加测试电路后信号周期没有明显变化,经测量两者最大相位差为25 ps。由测试电路仿真结果可以看出,该测试方案对原锁相环的功能特性影响不大,是有效可行的。 5 结语 本文将基于IEEE1149.1标准的边界扫描技术应用于模拟电路可测性设计中,对一款高频锁相环提出了测试方案,并给出了相应的测试电路。并对采用该方案进行测试的高速锁相环在增加测试电路前后电路的仿真结果进行了比较。结果表明,本文所提出的高频锁相环测试方案对锁相环本身的功能影响很小。 |

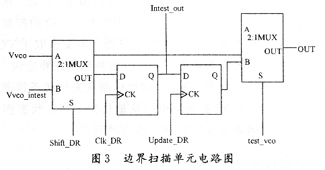

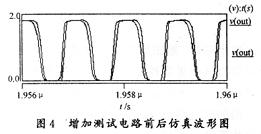

网友评论