在系统可编程器件isp1032E在高精度数据采集系统中的应用

发布时间:2010-8-30 13:54

发布者:techshare

|

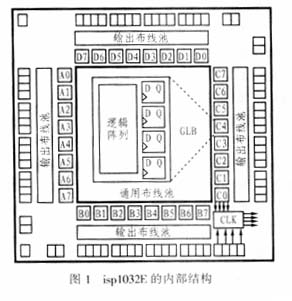

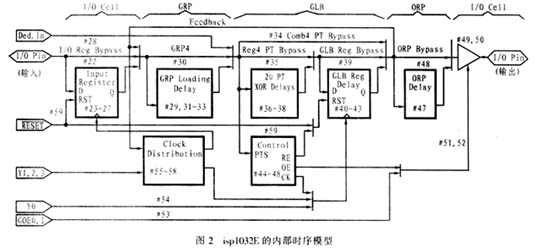

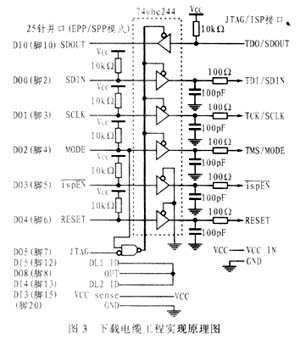

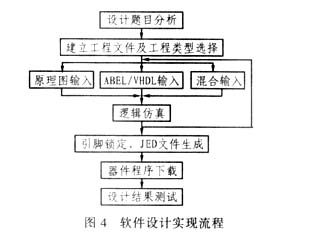

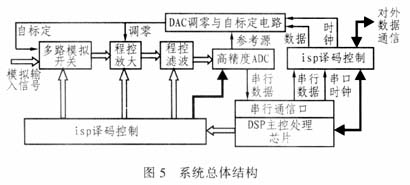

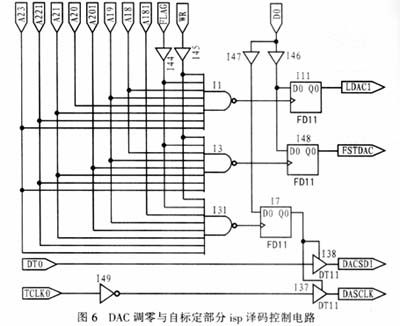

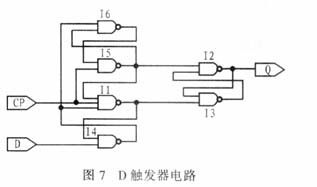

1 引言 isp在系统可编程技术是相对于以往可编程器件(PLD)实现逻辑设计时必须有专用的烧录器而言的,它不需要将isp器件拆上拆下即可实现对所需电路逻辑设计的反复设计和编程。这样就给系统设计研发、电路板调试和升级维护带来了极大的方便,从而缩短了系统的研发周期,实现了硬件电路的软件化设计。 相对于常用的PLD器件,isp器件具有体积小、容量大、编程方便、便于在线调试等优点,可实现较大规模的电路设计,且可实现编程加密。尤其在输入输出管脚众多的情况下,可以大大优化系统设计、节省系统空间。而相对于FPGA器件而言,isp器件的容量要小些,但其片内的逻辑一经加载就不会因掉电而再丢失。若要改变逻辑,只需通过下载电缆重新加载即可,而无需片外扩展EPROM存储电路的结构数据,因而电路实现更为方便简单。其实,这对于一般没有过于复杂的逻辑计算的电路设计,其容量一般已经足够。下面以Lattice公司的isp1032E为例,介绍isp器件在高精度数据采集系统中的应用技术。 2 isp1032E器件介绍 2.1 isp1032E的内部结构和时序模型 isp1032E的内部结构如图1所示。该器件有6000个门单元逻辑,192个寄存器单元,64个通用I/O,8个专用输入管脚,4个专用时钟输入,一个可提供上述各部分内部互连的集中连接池GRP。isp1032E的基本逻辑单元是万能逻辑块GLB,共32个,分别标定为A0~D7。每个GLB单元对应于18个输入单元、1个与或非逻辑阵列、4个输出单元。GLB的输入单元来自于GRP和专用输入;所有的输出单元都需进入GRP,以便于连接到其他的输入单元。 isp1032E的内部时序模型如图2所示。其中GOE0、GOE1为所有I/O单元的输出使能管脚。该管脚也可作为专用输入管脚来用。外部专用时钟输入管脚Y0与所有GLB单元的一个时钟输入脚相连;Y1进入时钟分配网络后可选择控制任何一个GLB单元的时钟输入;Y2进入时钟分配网络后可选择与任何一个GLB单元或I/O单元相连;Y3进入时钟分配网络后可选择与任何一个I/O单元相连。  可用于将所有的GLB单元或I/O寄存器单元复位。   2.2系统逻辑加载的硬件实现 在通过硬件加载系统逻辑时,首先用Lattice公司的专用编译软件ispDesignExpert生成所需的JED熔丝图文件,再通过专用下载软件ispVMSystem中的is-pDCD(ispDaisyChainDownload)将该JED熔丝图文件转换成isp流的形式,以便于利用PC机并口将所要生成的逻辑通过下载电缆烧录到相应的isp器件中。  isp设备下载电缆的编程接口协议采用的是Lattice ISP协议或ispJTAG协议标准。ispLSI1000/E和2000系列、以及ispGDS和ispGAL系列都只能通过Lattice ISP接口来进行编程;而ispLSI2000V系列只能采用ispJTAG标准进行编程;其余的ispGDX、ispLSI3000和6000系列均可采用上述两种协议。 通过下载电缆实现上述过程的原理图如图3所示。需要特别注意的是:图中ispEN信号与地之间必须加入0.01μF的滤波电容,而且该电容与  脚的距离越近越好。这是因为在下载程序期间,is-pEN信号为低电平有效,这样就很容易受干扰而淹没本身很弱的有效信号。 3 软件流程 该数据采集系统的软件设计流程如图4所示。通常在设计软件时,图形输入方法与硬件语言描述方法有各自的优点。图形输入法比较简单明了,便于调试;而硬件描述语言在书写复杂电路设计中具有较大的优势。实际上,混合输入法兼有上面两种方法的优点,因而具有广泛的应用。  4 在数据采集中的应用 4.1工程背景 现代测试系统的一个共同特点是高速、高精度和多参数综合测试。在背板式发动机参数综合测试系统中,应变、压阻、热电阻传感器以及热电耦信号的调理输出都需要做高精度的采集与处理。为实现高精度的性能指标,充分发挥DSP速度快,运算功能强大的优势,笔者设计了以DSP为核心的处理器、以isp译码控制电路为核心的控制单元和多路模拟开关选择电路、程控放大电路以及程控模拟滤波电路、高精度ADC模数转换电路、DAC调零与自标定电路等组成的高精度数据采集板。该测试系统对内可以实现高精度的数据采集,对外可以通过isp译码控制经仪器总线与其它仪器板卡或互联设备进行数据通信。 4.2 系统的总体结构 图5是该高精度数据采集系统的总体结构。 系统中的ADC选用CRYSTAL公司的24位串行双通道输出模数转换器CS5397来实现高精度的数据采集。为了检测模拟通道的功能,通道输入信号可切换至内部的DAC调零与自标定电路,以便用DAC调零与自标定电路产生特定的直流与交流信号来作为标定信号此标定信号可用于标定通道的增益与零偏,并提高系统精度。为了实现理想的幅频特性,系统采用了前端模拟滤波和后端DSP数字滤波相结合的工作方式。 4.3 应用结果 DAC调零与自标定电路部分的isp译码控制电路(原理图方式)如图6所示。在该程序成功烧录到isp芯片后,可以通过isp地址译码来控制DAC(DAC7614)串行输入数据和输入时钟的开或关,并根据该DAC的工作特性输出所需的、用于调零与自标定的模拟电压值。   在电路设计中,由于用到的锁存器数目繁多,而有可能造成系统资源的不足(锁存器数目不足),所以,系统专门设计有D触发器电路以解决D触发器资源不足的问题。其原理图如图7所示。 5 小结 isp在系统可编程技术及其相应的器件ispLSI是Lattice公司1992年首创的。其先进的思想和灵活的在系统可编程方式极大的冲击了传统的数字电路设计,从而为数字电路设计带来了一场技术革命。 1999年11月,Lattice公司又推出了在系统可编程模拟电路ispPAC(In-System Programmability Pro-grammable Analog Circuits),从此揭开了模拟电路开发及研究的新篇章。虽然与ALTERA公司和XILINX公司相比,Lattice公司的开发工具要略逊一筹,但该公司在中小规模PLD的开发上非常有特色。特别是在99年收购了Vantis(原AMD子公司)后,Lattice公司已成为世界第三大可编程逻辑器件供应商。  |

网友评论