基于SoPC的通用在线调试器设计

发布时间:2010-8-20 14:31

发布者:lavida

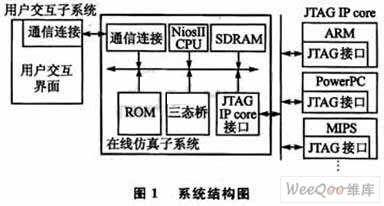

|

目前,国内生产的部分在线仿真调试器可以对部分嵌入式芯片进行仿真调试。但从本质上,这些仿真调试器无法对所有带在线调试功能的嵌入式芯片进行仿真调试。BDI2000和TRACE32等仿真器可以在不改变硬件条件下,通过下载针对特定嵌入式芯片的调试“核”来实现对不同嵌入式芯片的仿真调试,但是非常昂贵,难以适应国内绝大多数中小企业的实际需求。 本文基于SOPC软硬件协调设计验证技术设计了一款通用在线调试器。SOPC技术将传统的在线调试器以芯片形式呈现,采用知识产权核(IP core)复用技术,抽象各种不同架构的嵌入式处理器接口,给出支持统一调试接口的IP core架构,提出了基于通用在线调试器的嵌入式软件调试方法。 本文介绍了系统架构,以及关键子系统的工作原理及其与所处硬件环境之间的交互,最后对JTAG IP core子系统进行了仿真验证。 1 整体设计 系统由用户交互、在线仿真和JTAG IP core三个子系统构成,如图1所示。  用户交互子系统包括TCP/IP通信端口与用户交互界面。它主要负责访问和处理源文件;接收调试命令,根据TCP/IP协议封装成调试命令请求包,发送给通用调试器;同时,解析目标机的响应。其中,通信端口负责与通用在线调试器通信。 在线仿真子系统是一个针对不同类型嵌入式处理芯片的高扩展性嵌入式系统。它包括硬件部分和软件部分。硬件部分采用SOPC技术加载Altera公司的IP core形成一个以NiosII CPU为核心的,TCP/IP和JTAG IP core端口为通信模块的硬件平台。软件部分包括网络传输处理和JTAG IP core接口程序部分。 JTAG IP core是业务信号处理逻辑模块,可以是ARM、PowerPC、MIPS等不同架构的嵌入式处理器。 1.1 核心子系统设计 JTAG IP core是系统的核心部分。它负责目标机调试命令的格式转换、传送逻辑控制,以及JTAG状态机状态转换的控制。JTAG IP core子系统划分为5个模块,每个模块又由子模块所构成。模块的执行次序不同,或并发,或顺序执行。JTAG IP core子系统结构图如图2所示。  总线读写模块负责接收参数和指令,同时将处理后的数据输出到总线。接收总线数据子模块接收Avalon总线的数据并更新标志位;读信号触发向总线发送数据子模块进行数据传输。总线读写模块逻辑流程如图3所示。  参数指令传递模块用于合并总线读写模块接收的参数和指令。当写有效且主控模块没有工作时,将从Avalon总线接收的前128位数据拼接起来存放在参数寄存器中,后32位数据由指令寄存器接收;当写无效时停止输入,并且启动状态机模块。参数寄存器和指令寄存器均在在本模块中定义。 状态机模块负责仿真JTAG状态机中的16个状态,凭借主控模块中TMS序列驱动实现状态间的转移,同时向JTAG的TMS端口送出TMS序列,以控制目标机中JTAG状态机的运行。在SHIFT_IR和SHIFT_DR状态下,相应的目标机指令(如ARM指令)和数据通过JTAG的TDI端口送入目标机。 目标机TDO序列接收模块负责接收目标机传来的数据,并将其存放在相应的寄存器中。 主控模块在JTAG状态机运行之前,根据参数指令传递模块中指令寄存器的值更新状态机的TMS和TDI序列数据;然后初始化TMS寄存器、TDI寄存器、标志寄存器,通过标志寄存器的值判断JTAG状态机的运行;在其运行结束后,在状态机结束处理子模块中把目标机传来的数据送到输出寄存器,并设置读有效以启动总线读写模块。 1.2 JTAG IP core接口程序 在线仿真子系统中,JTAG IP core接口为JTAG IPcore子系统与NiosII CPU硬件环境之间提供数据交互服务。接口程序分成宏定义、写数据、读数据3个部分。 宏定义部分,JTAG IP core中的操作指令包括:进入调试状态、获取CPU IDCODE、读/写寄存器、读/写内存、设置断点、设置观察点、跳出调试状态等。 写数据部分,目标机的内存地址和寄存器号作为参数数据传递到JTAG IP core子系统中,调试指令(即宏定义中的指令)与参数一起被写入JTAG IP core子系统中。部分程序代码如下:  其中,pi表示参数数据(i=0,…,3),ir表示指令。IOWR_32DIRECT(JTAGTEST_0_BASE,ADDR(i),pi)表示将pi或ir的值写入JTAG IP core。 读数据部分的功能是从JTAG IP core子系统中读取目标机传回的数据。当在线仿真子系统的Nios II CPU准备从JTAG IP core子系统中读取数据时,JTAG IP core子系统中的寄存器数据不一定是有效数据,因而需设置一个寄存器(命名为read_ready)来循环检测数据是否有效。如果寄存器的值不为0,则允许读取数据。  2 JTAG IP core子系统仿真验证 JTAG IP core子系统设计完成后,为了验证逻辑的正确性,在QuartusII环境下对该IP core模块进行了仿真验证。在仿真中,将NiosII CPU给出的触发信号cLK修改为2分频,以便能较直观地看清触发子系统允许的TCK信号的产生。当JTAG IP core接口程序被启动时,总线读写模块开始从Avalon总线上读取参数和指令(如图4所示,writedata、address、inst∣reg_in[0,1,4]及ir寄存器中出现数据)。当参数指令传递模块中的palm和ir寄存器中出现数据后,主控模块开始工作;同时,主控模块的busy_flag信号触发状态机模块工作。从图中可看到,TMS序列出现数据,TDI端口开始送出数据。JTAG IP core模块能按照预定设计输出TMS和TDI调试序列,说明该IPcore在逻辑上是正确的。 结 语 本文提出了以知识产权核(即IP core)复用技术为主的通用性调试器设计思路以及实现方法。下一步,可以基于ARM、MIPS系列芯片,结合本文的解决方案实现具体的IP core,同时增加多线程调试等优化工作。 |

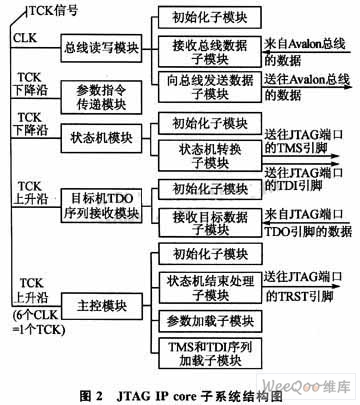

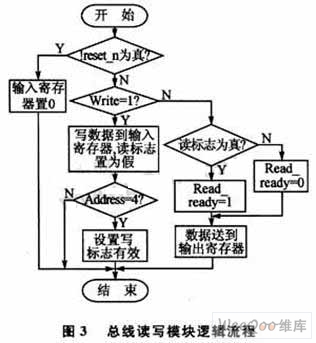

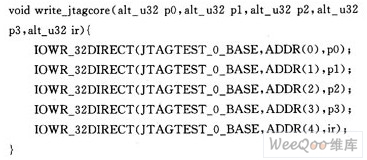

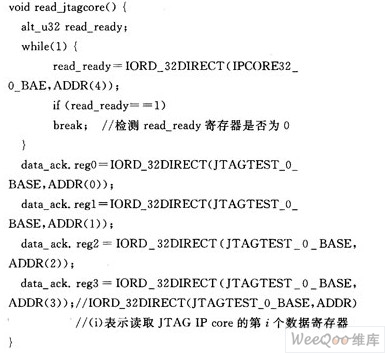

网友评论