基于CPLD的数据采集与显示接口电路仿真设计

发布时间:2010-8-20 14:27

发布者:lavida

|

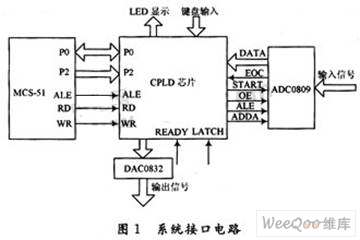

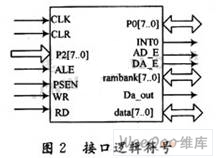

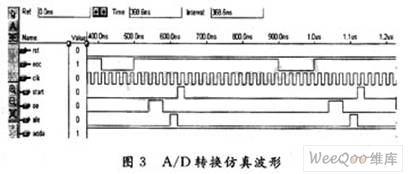

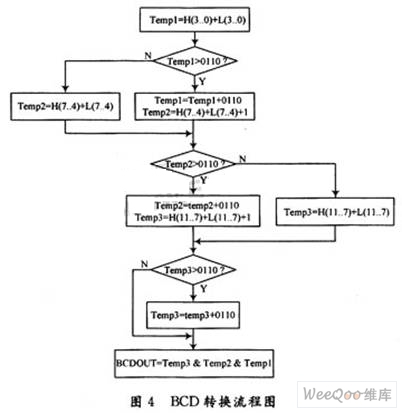

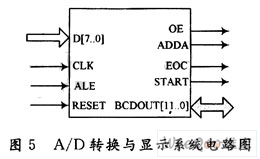

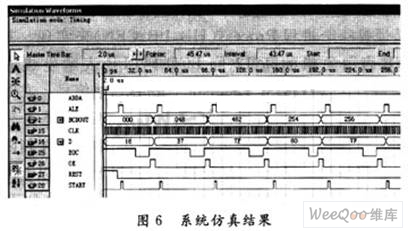

1 引言 CPLD称为复杂可编程逻辑设计芯片,它是大规模可编程器件,具有高集成度、高可靠性、高速度的特点。CPLD是利用EDA技术进行电子系统设计的载体。硬件描述语言是EDA技术进行电子系统设计的主要表达手段,VHDL语言是常用的硬件描述语言之一;软件开发工具是利用EDA技术进行电子系统设计的智能化的自动化设计工具,常用开发工具有QuartusⅡ,Ispexpert,Foundation等。CPLD以高速、高可靠性、串并行工作方式等特点在电子设计中广泛应用。它打破了软硬件之间的界限,加速了产品的开发过程。同样单片机具有性价比高、功能灵活、良好的数据处理能力等特点。CPLD芯片与单片机结合在高性能仪器仪表中应用广泛。 1 电路的仿真设计 1.1 硬件电路功能 用一片MCS-51芯片、一片CPLD/FPGA芯片、模/数转换器ADC0809和数/模转换器DAC0832构成一个数据采集系统,并用CPLD/FPGA实现数据采样、D/A转换输出、有关数据显示的控制,单片机完成对A/D转换数据运算。电路如图1所示。  系统功能如下:系统按一定速率采集输入电压U1,经AD0809转换为8位数字量data;输入数据与通过CPLD/FPGA采样后输入单片机进行相关运算,最后通过CPLD/FPGA送至DAC0832转换为△U;数据采集和处理均在数据采集系统控制器的管理下有序进行。工作速率由时钟信号CLK的速率决定。 1.2 单片机与CPLD/FPGA接口设计 单片机采用以总线方式与可编程芯片进行数据与控制信息通信,此方式有许多优点: (1)速度快。其通信工作时序是纯硬件行为,对于MCS-51单片机只需一条单字节指令就能完成所需的读/写时序如MOV@DPTR A和MOV A@DPTR。 (2)节省CPLD芯片的I/O口线。如果将图中的译码器设置足够的译码输出以及安排足够的锁存器就能仅通过19根I/O口线在FPGA/CPLD与单片机之间进行各种类型的数据与控制信息交换。 (3)相对于非总线方式单片机的编程简捷控制可靠。 (4)在FPGA/CPLD中通过逻辑切换单片机易于与SRAM或ROM接口。这种方式首先由FPGA/CPLD与接口的高速A/D等器件进行高速数据采样并将数据暂存于SRAM中。采样结束后通过切换使单片机与SRAM以总线方式进行数据通信以便发挥单片机强大的数据处理能力。 系统工作过程如下:ALE为地址锁存使能信号,当下降沿来时,将P0口将低8位地址送人可编程芯片CPLD/FPGA中的地址锁存器,然后在P2口和P0口形成的16位地址及WR信号共同作用下,将P0口的数据送入可编程芯片。单片机通过两条指令MOVXDPTR#ADDR和MOVX@DPTR A将数据写入芯片。在P2口和P0口形成的16位地址及RD信号共同作用下,将AD0809转换后数据data送入单片机的P0口。单片机通过两条指令MOVX DPTR#ADDR和MOVXA@DPTR将数据读入P0口。设置A/D转换器件片选信号ad_e和DA转换器件片选信号da_e,设置数据输入/输出口data[7..0]。单片机与FPGA通信接口程序(名为MCS51)通过编译后,生成的逻辑符号如图2所示。  CPLD使用EPM7128时钟为16 MHz有源晶振,首先使用CLK对复位信号采样,8051的复位信号要求是高电平维持2个机器周期,2个机器周期就是2×12=24个振荡周期,对复位信号连续采样10次,若是一直为高电平,就产生片内复位使能信号。其他片内寄存器以这个复位信号做同步复位,对WR,RD,ALE都做了采样,避免毛刺干扰。 1.3 AD0809与CPLD/FPGA状态机接口设计 1.3.1 AD0809状态机功能设计 状态机的最简结构一般由两个进程构成,即主控时序进程和主控组合进程。一个进程描述时序逻辑输出,另一个进程描述组合逻辑包括进程间状态值的传递逻辑以及状态转换值的输出。将AD0809与CPLD/FPGA的接口设计系统划分为两部分,即数据单元和控制单元。数据单元包括保存运算数据和运算结果的数据寄存器,也包括完成数据运算的组合逻辑电路。控制单元用来产生信号序列,以决定何时进行何种数据运算,控制单元要从数据单元得到条件信号,以决定继续进行那些数据运算。数据单元要产生输出信号、数据运算状态等有用信号。数据单元和控制单元中,有两个非常重要的信号,即复位信号和时钟信号。复位信号保证了系统初始状态的确定性,时钟信号则是时序系统工作的必要条件。状态机通常在复位信号到来的时候恢复到初始状态,每个时钟到来的时候内部状态发生变化。从AD0809的初始状态开始,也就是状态机复位以后开始的状态。在建立每个状态时都写出关于这个状态的文字功能描述,AD0809状态机功能描述与相应引脚的取值如下: S0态:初始状态,选择通道1的模拟信号输入,ADDC=‘1’,ALE=START=OE=LOCK=‘0’; S1态:通道锁存状态。ALE=‘1’,START=OE=LOCK=‘0’: S2态:启动A/D转换状态。ALE=‘1’,START=‘1’,OE=LOCK=‘0’; S3态:A/D转换等待状态,ALE=START=‘0’,OE=LOCK=‘0’; IF EOC=‘0’保持当前状态不变,继续等待A/D转换,ELSE转换结束,进入下一状态; S4态:数据输出允许状态,A/D转换完毕,开启数据输出允许信号,ALE=‘0’,START’0’,OE=‘1’,LOCK=‘0’; S5态:数据锁存状态,开启数据锁存信号,将转换结果送锁存器锁存,ALE=‘0’,START=‘0’,OE=‘1’,LOCK=‘0’; S6态:延时状态,为了保证数据可靠锁存,延时一个时钟状态周期;ALE=‘0’,START=‘0’,OE=‘1’,LOCK=‘1’; 其他状态:返回到初始状态,ALE=START=OE=LOCK=‘0’。 1.3.2 ADC0809状态机程序设计 ADC0809为单极性输入,8位转换精度逐次逼进式A/D转换器。其采样速度为每次转换约100μs。在转换开始前由地址锁存允许信号ALE将3位地址锁入锁存器中以确定转换信号通道。EOC为转换结束状态信号,由低电平转为高电平时指示转换结束,此时可读入转换好的8位数据。EOC在低电平时指示正在进行转换。START为转换启动信号,上升沿启动。OE为数据输出允许高电平有效。CLK为ADC转换时钟输入端口500 kHz左右。为了达到A/D器件的最高转换速度,A/D转换控制器必须包含监测EOC信号的逻辑,一旦EOC从低电平变为高电平即可将OE置为高电平,然后传送或显示已转换好的数据[D0..D7]。状态机由三个进程组成ADC,AD_STATE和DATA_LOCK。ADC是此状态机的主控组合逻辑进程,确定状态的转换方式和反馈控制信号的输出工作过程中首先监测系统复位信号RST,当其为高电平时使此进程复位至初始态ST0。启动A/D转换信号START在状态ST3搜索转换状态信号EOC由0变1时即在状态ST4开启输出。使能信号OE在下一状态使LOCK产生一个上跳沿从而在此时启动进程DATA_LOCK将由0809转换好的8位数据锁进锁存器ADC_DATA。根据时序电路图通过状态机设计程序完成与CPLD/FPGA芯片的连接。图3为状态机程序仿真结果。  1.4 BCD码转换与显示电路设计 当ADC0809的基准电压(Vref)为5.12 V时,最小电压准位是5.12/28=0.2 V。分析模拟输入电压与输出电压的对应关系可知,当ADC0809的D[7..0]收到的数据信号为10000110(即86H)时,则高4位1000为2.56 V,而低4位0110为0.12 V,所以最后的电压输出结果是2.68 V。为了方便后续的电压数据显示,在此将输出电压表示成12位的BCD码形式。将高4位数据D(7..4)转换为对应的高12位BCD码H(11..0);将低4位数据D(3..0)转换为对应的低12位BCD码L(11..0)。在程序中首先用VHDL语言描述一个新的进程Process(regl),然后采用case…when…语句,生成并行结构的电路。 将生成的高12位BCD码与低12位的BCD码相加,得到12位的BCD码,该结果即为所求的BCD码结果。如上述的256 V的BCD码是0010 0101 0110,0.12 V的BCD码是0000 0001 0010,所以相加的结果是0010 0110 1000,即为2.68 V。因此在电路中必须设计一个12位的BCD码加法程序,实现由8位二进制转换为12位BCD码硬件电路。在程序设计中应当注意的是BCD码相加时,由最低4位加起,且每4位相加的结果超过1001时,应加0110调整。该段程序的描述是通过一个进程Process(HB,LB,CEN)来实现。其中HB表示生成的高12位BCD码,LB表示生成的低12位BCD码,CEN表示系统提供的时钟信号。在时钟上升沿时刻进行BCD码相加,并判断结果是否超过1001,判断程序采用if…then…语句,实现条件判断电路。按照图4完成BCD码程序转换设计。将以上两段程序进行组合,最终获得由VHDL语言描述的BCD码转换程序。  1.5 A/D转换与BCD码合成系统电路 将A/D转换电路与BCD码转换电路组成统一系统,通过硬件编程语言VHDL中的进程语句将编制成功的A/D转换电路描述语句和BCD码转换电路描述语句组合成一个整体程序,通过QuartusⅡ软件生成系统图,如图5所示。  A/D转换结果由3位十进制数表示,每位十进制数由4位BCD码表示,总共有12位BCD码输出。将电路输出BCDOUT(11..0)分成BCDOUT(11..8),BCDOUT(7..4)和BCDOUT(3..0)三部分,通过三个进程Process()分别用VHDL语言编程描述LED显示驱动。对整个系统进行波形仿真,得到仿真波形如图6所示,最后在Gw48-CK实训开发系统完成功能验证。  2 结 语 将CPLD和微机控制技术相结合,在智能仪表设计和控制系统设计领域提高了系统设计的灵活性,缩短了产品开发周期,同时使系统易于升级和扩展。因为采用了CPLD(复杂可编程逻辑器件),极大提高了系统I/O口利用率,缩小了印刷电路板面积,提高了系统集成度,在多输入/多输出的数据采集和控制系统领域有十分广阔应用前景。 |

网友评论