基于USB的高精度多通道数据采集卡设计

发布时间:2010-8-19 17:27

发布者:lavida

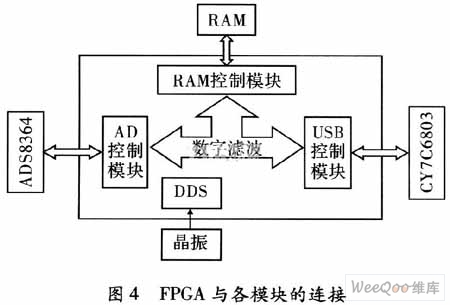

|

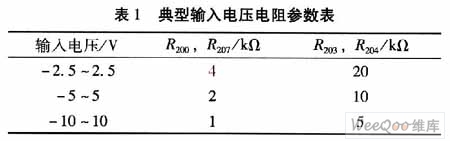

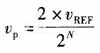

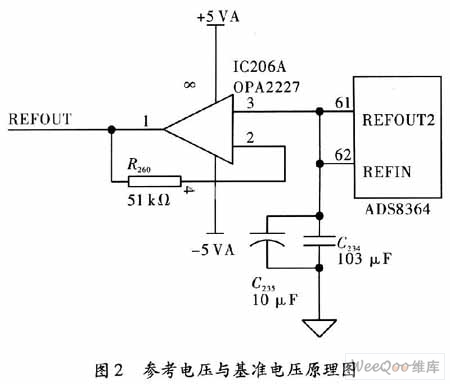

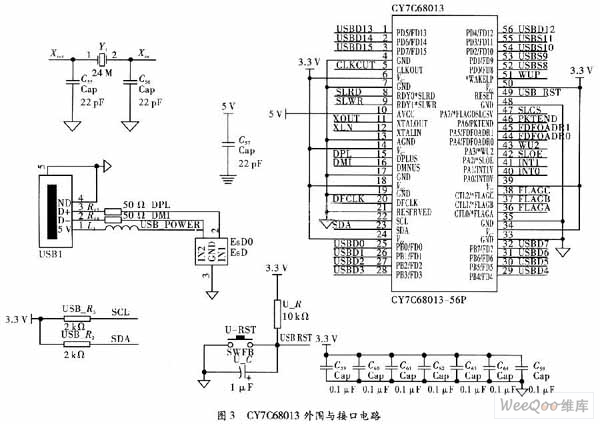

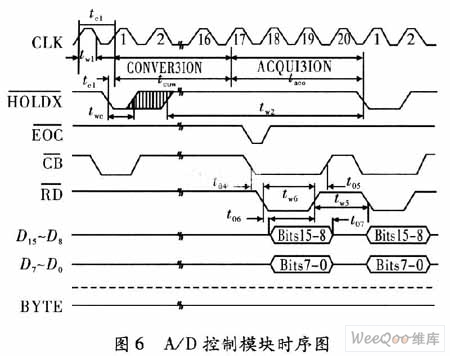

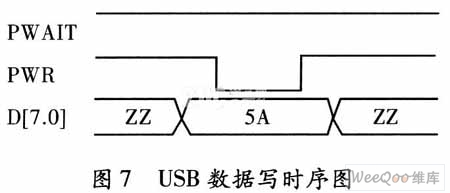

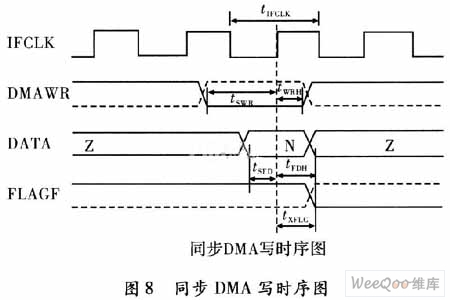

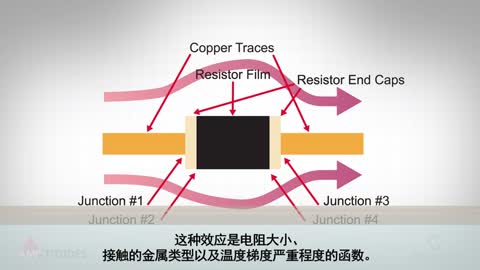

在电子测量中,不仅需要对多路信号进行高精度的采集和预处理,而且要将其快速地传送到计算机,以便于对测量的监测。文中选用ADS8364来进行多通道信号采集,通过CY7C68013芯片采用USB2.O协议进行数据的快速传输。 1 多通道,高精度的A/D转换 ADS8364是美国TI公司生产的高速、低功耗,6通道同步采样16位模数转换器。ADS8364采用+5 V工作电压,并带有80 dB共模抑制的全差分输入通道以及*μs连续近似的模数转换器、6个差分采样放大器。 当ADS8364采用5 MHz的外部时钟来控制转换时,它的取样率是250 kHz,同时对应于4μs的最大吞吐率,这样,采样和转换共需花费20个时钟周期。另外,当外部时钟采用5 MHz时,ADS8364的转换时间是3.2μs,对应的采集时间是0.8μs。因此,为了得到最大的输出数据率,读取数据可以在下一个转换期间进行。 ADS8364中的采样/保持模块以最大吞吐率250 kB工作,它的输入带宽大于ADC的奈奎斯特频率。而典型的小信号带宽是300 MHz。孔径延迟时间为5 ns,每次的平均增量为5 ops。这些特性反映了ADS8364接收输人信号的能力。 1.1 A/D前端信号调理电路 鉴于多通道信号采集的时序的重要性,这里选用差分放大电路对信号进行调理。 采用TI公司的运算放大器OPA2227组成一个电压放大器,将输入电压转换到ADS8364的差分输入电压范围。根据需要,可以通过调整放大电路中电阻的大小,改变输入电压的范围,其对应的参数表如表1所示。  ADS8364在参考电压为2.5 V的情况下,其测量范围为±1.25 V。而实际中的测试信号一般为±2.5 V,±5 V或±lO V,所以,在ADS8364的前端,要经过线性衰减、限幅和滤波。其调理电路原理图,如图1所示。  1.2 A/D电源电路 数据采集电路需要完成高精度的数据采集,因此电源部分的设计是相对比较重要的。 在作进一步的分析之前,需要说明采样精度和有效位都是对采样质量高低的描述。设采样精度为vp,有效位为N,基准电压为vREF,基准电压噪声电平为VN,则有  2 USB接口模块设计 Cypress Semiconductor公司的EZ-USB FX2是世界上的第一款集成USB2.0的微处理器,它集成了USB2.0收发器、SIE(串行接口引擎)、增强型8051微控制器和可编程的外围接口。FX2这种独创性结构可使数据传输率达到56 MB·s-1,即USB2.0允许的最大带宽。EZ-USB FX2 CY7C68013的微处理器是一个增强型的805l内核,性能可达标准8051的5~10倍,并与标准805l的指令完全兼容。增强型的8051内核使用RAM芯片作程序指令和数据存储器,从而使得EZ-USB FX2 CY7C68013具有“软”特性,也就是说,可以通过自行编写程序指令来实现所需的功能。  由于USB通信是本系统设计主要的任务目标,所以在设计时也充分考虑到系统的可扩展性,所有的信号引脚都有排线引出,方便了测试和扩展。  3 FPGA逻辑电路 图4为采集传输系统中FPGA与各模块的连接。  整个电路选用Altera公司推出的新一代低成本的Cyclone系列FPGA器件EPlC6Q240作为控制和信号处理芯片。EPlC6Q240型FPGA芯片具有强大的硬件逻辑功能,总逻辑单元达5 980个,有I/O引脚181个,92 160位的内部存储单元,20个RAM单元,2个锁相环。利用这些强大的功能,可以很容易进行模块控制和数据动态滤波。如图4所示,通过FPGA对A/D进行采样控制,将A/D采样的数据进行数字滤波后传送到RAM中进行,或是直接通过USB模块将数据床送到电脑中进行处理。 采用VerilogHDL硬件语言编程来对A/D采集,RAM传输,USB传输等进行控制信号输出,并对采样的数据进行数字滤波。 A/D数据接口模块实现对ADS8364数据的采样,采样后的数据进行滤波处理。本模块对ADS8364的控制引脚有: (1)模拟采样通道控制信号为/HOLDA,/HOLDB,/HOLDC; (2)数据输出模式以及通道选择信号为A0,A1和A2; (3)读控制信号为/RD。 首先将5 MHz时钟和使能信号相与产生新时钟,使用该时钟驱动一个20个状态的状态机。在计数器值为15时将HOLDa,HOLDb,HOLDc置0,启动一次数据采样。在计数值为2~3,4~5,6~7,8~9,10~ll,12~13且相应的通道得到使能时,分别发出通道l至通道6的通道地址。在计数值为3,5,7,9,ll,13时发出读信号读取相应通道的数据。在计数值为15时发出采样完毕信号,指示6通道数据已经采集完毕。  USB控制电路分两个模块完成。模块1实现主机向FPGA寄存器单元的配置,模块2实现FPGA向主机的数据包输出。  模块1实现在地址IO模式下向寄存器写数据。写时序如图7所示。可以根据地址线和PWR信号实现对某寄存器的写控制。  模块2实现在DMA模式下FPGA向主机的批量数据传输。同步DMA的时序图如图8所示(时钟由FPGA提供)。  本系统使用一个状态机实现该功能,状态机在“查找”和“传输”两个状态之间切换。系统启动以后首先进入查询FIFO的状态,在查询到FIFO中的数据量大于一个USB数据包(2 040 bit)时,状态机进入到“传输”状态。在“传输”状态下,按照上述同步。DMA写时序,首先传输6 bit包头,然后传输2 040 bit数据,最后传输2 bit数据校验。在数据传输的过程中,电路要一直查询DMAING的状态,检测到:DMAING为低时要暂停数据传输。在传输完2 kB数据后,状态机再转入到“查询”状态,进行下一轮数据传输状态。 系统当前的工作时钟为20 MHz,在USB接口处可以达到的最大带宽约为10 MB,系统分频给A/D的时钟为5 MHz,这样可以保证A/D接口的最大带宽达到3 MB。在Flash接口处的带宽约为5 MB。将时钟速度提升l倍,则USB口的传输能力可以达到约20 MB。 数据处理与储存模块主要是FPGA将高速A/D采集到的数据进行打包、暂存。本套电路中使用了一片由,TI公司生产的高速静态RAM IS61-LV51216作为数据暂存器件;由FPGA对这片RAM存储器进行监控。 4 结束语 采用USB协议的数据采集卡可以满足对数据进行多通道的高精度采集、处理和传输,在数据有效采集的情况下,摆脱了对端口的依赖。 |

网友评论