ЛљгкFPGAЕФЫЋПкRAMЪЕЯжМАгІгУ

ЗЂВМЪБМфЃК2010-8-19 17:26

ЗЂВМепЃКlavida

|

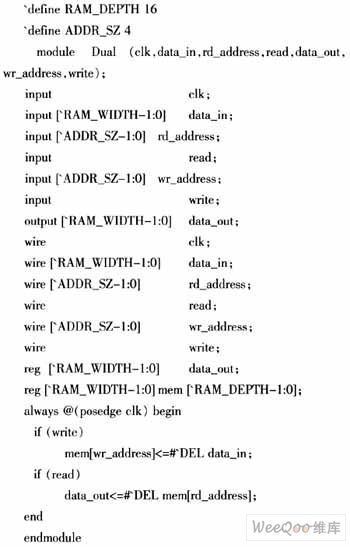

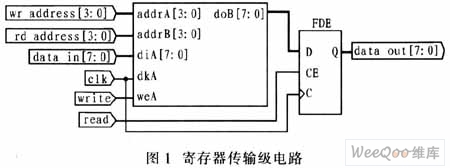

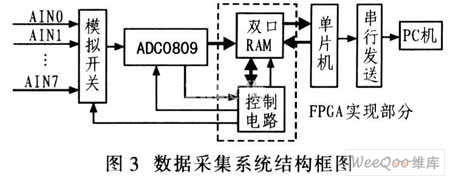

ЫцзХЕчзгММЪѕЕФЗЩЫйЗЂеЙЃЌДѓСПЕФИпЫйЪ§ОнВЩМЏКЭдкЯпВтЪдЖдЯжДњЙЄвЕВтПиЯЕЭГКЭвЧЦївЧБэЕФЙІФмКЭадФмЬсИќИпвЊЧѓЁЃCPUВЂааЙЄзї(ЫЋЕЅЦЌЛњЯЕЭГ)ЗНЪНЕУЕНЙуЗКгІгУЁЃЮЊСЫЪЙ2ИіЕЅЦЌЛњФмЙЛПьЫйгааЇНЛЛЛаХЯЂЃЌГфЗжРћгУЯЕЭГзЪдДЃЌВЩгУЫЋПкRAMЪЕЯжДцДЂЦїЙВЯэЪЧФПЧАНЯЮЊСїааЕФЗНЗЈЁЃ ДѓШнСПЁЂИпЫйFPGAЦїМўОпгаМЏГЩЖШИпЁЂЬхЛ§аЁЁЂСщЛюПЩжиХфжУЁЂЪЕбщЗчЯеаЁЕШгХЕуЃЌдкИДдгЪ§зжЯЕЭГжаЕУЕНдНРДдНЙуЗКЕФгІгУЁЃЪ§зжЕчТЗЩшМЦВЩгУlЦЌFPGAЦїМўЁЂДцДЂЩшБИКЭвЛаЉЕчЦјНгПкЦЅХфЕчТЗЕФНтОіЗНАИвбГЩЮЊжїСїбЁдёЗНАИЁЃгУFPGAРДЪЕЯжЫЋПкRAMЕФЙІФмПЩвдКмКУЕиНтОіВЂааадКЭЫйЖШЮЪЬтЃЌЖјЧвЦфСщЛюЕФПЩХфжУЬиадЪЙЕУЛљгкFPGAЕФЫЋПкRAMвзгкНјаааоИФЁЂВтЪдМАЯЕЭГЩ§МЖЃЌПЩНЕЕЭЩшМЦГЩБОЃЌЫѕЖЬПЊЗЂжмЦкЁЃ 1 ЫЋПкRAMМђНщ ЫЋПкRAMЪЧдк1ИіSRAMДцДЂЦїЩЯОпгаСНЬзЭъШЋЖРСЂЕФЪ§ОнЯпЁЂЕижЗЯпКЭЖСаДПижЦЯпЃЌВЂдЪаэСНИіЖРСЂЕФЯЕЭГЭЌЪБЖдЦфНјааЫцЛњадЗУЮЪЕФДцДЂЦїЃЌМДЙВЯэЪНЖрЖЫПкДцДЂЦїЁЃЫЋПкRAMзюДѓЕФЬиЕуЪЧДцДЂЪ§ОнЙВЯэЁЃ1ИіДцДЂЦїХфБИСНЬзЖРСЂЕФЕижЗЁЂЪ§ОнКЭПижЦЯпЃЌдЪаэСНИіЖРСЂЕФCPUЛђПижЦЦїЭЌЪБвьВНЕиЗУЮЪДцДЂЕЅдЊЁЃвђЮЊЪ§ОнЙВЯэЁЃдђБиаыОпгаЗУЮЪжйВУПижЦЁЃФкВПжйВУТпМПижЦЬсЙЉвдЯТЙІФмЃКЖдЭЌвЛЕижЗЕЅдЊЗУЮЪЕФЪБађПижЦЃЛДцДЂЕЅдЊЪ§ОнПщЕФЗУЮЪШЈЯоЗжХфЃКаХСюНЛЛЛТпМ(Р§ШчжаЖЯаХКХ)ЕШЁЃЫЋПкRAMПЩгУгкЬсИпRAMЕФЭЬЭТТЪЃЌЪЪгУгкЪЕЪБЪ§ОнЛКДцЁЃ CY7C006AЪЧCypressЙЋЫОЩњВњЕФ16 kbЁС8ИпЫйЫЋПкОВЬЌRAMЃЌДцШЁЫйЖШаЁгк20 nsЁЃИУЦїМўОпгаеце§ЕФЫЋЖЫПкЃЌПЩвдЭЌЪБНјааЪ§ОнДцШЁЃЌСНИіЖЫПкОпгаЖРСЂЕФПижЦаХКХЯпЁЂЕижЗЯпКЭЪ§ОнЯпЃЌСэЭтЭЈЙ§жїЃЏДгбЁдёПЩвдЗНБуЕиРЉДцДЂШнСПКЭЪ§ОнПэЖШЁЃЭЈЙ§ЦїМўЕФаХКХСПБъжОЦїЃЌзѓЁЂгвСНЖЫПкПЩвдЪЕЯжЦїМўзЪдДЙВЯэЁЃ 2 ЫЋПкRAMдкFPGAжаЕФЪЕЯж БОЩшМЦВЩгУздЖЅЖјЯТЕФЩшМЦЫМЯыЁЃбЁгУXilinxЙЋЫОЕФSpartan-6 FPGAЦїМўЃЌЛљгкЕЭЙІКФ45 nmЁЂ9-Н№ЪєЭВуЁЂЫЋеЄМЋбѕЛЏВуЙЄвеММЪѕЃЌЬсЙЉИпМЖЙІКФЙмРэММЪѕЃЌ150 000ИіТпМЕЅдЊЃЌМЏГЩЪНPCI ExpressФЃПщЃЌИпМЖДцДЂЦїжЇГжЁЃ250 MHz DSPsliceКЭ3ЃЎ125 GbЃЏsЕЭЙІКФЪеЗЂЦїЁЃЭЈЙ§Verilog HDLгябдЖдЫЋПкRAMЙІФмЕФУшЪіОЭФмдквЛЦЌFPGAЦїМўФкЪЕЯж8ЮЛ16зжНкЕФЫЋПкRAMЃЌВЂНјааЖСаДВйзїПижЦЁЃЫЋПкRAMЖСаДВйзїПижЦVerilog HDLДњТыШчЯТЃК   ЭМ1ЪЧЫЋПкRAMЕФVerilog HDLДњТыдкXilinx ISEжазлКЯКѓЕФМФДцЦїДЋЪфМЖЕчТЗЭМЁЃ  ЙІФмЗТецЕФЪЧXilinxЙЋЫОвбОНЈСЂздМКЕФБрвыПтЕФModelsim XEЂѓ6ЃЎ2cШэМўЃЌЗТецНсЙћШчЭМ2ЫљЪОЃЌТњзуЩшМЦвЊЧѓЁЃ  ОXilinx ISEШэМўзлКЯЪЕЯжЩшМЦЃЌЩњГЩПЩЯТдиЕФБШЬиСїЃЌНЋЦфЯТдиЕНFPGAжаЃЌЪЕЯжЫЋПкRAMЕФЙІФмЁЃFPGAЦїМўФкВПОпгаЗсИЛЕФзЪдДЃЌПЩвддкЪЕЯжЫЋПкRAMЛљБОЙІФмЕФЛљДЁЩЯЁЃТњзуЯЕЭГЩшМЦЕФЦфЫћашЧѓЃЌЧвСщЛюПЩХфжУЁЃ 3 ЛљгкFPGAЕФЫЋПкRAMгІгУ ЫЋПкRAMдкЪ§зжЯЕЭГжагІгУЙуЗКЁЃИпЫйЪ§ОнВЩМЏЯЕЭГжаЃЌвЛАуЕФЪ§ОнДЋЪфЯЕЭГдкДѓЪ§ОнСПЧщПіЯТЛсдьГЩЪ§ОнЖТШћЯжЯѓЁЃдквЛаЉЪЕЪБПижЦГЁКЯЃЌЪЕЪБЫуЗЈОГЃашвЊгЩМИИіDSPДЎааЛђВЂааЙЄзївдЬсИпЯЕЭГЕФдЫааЫйЖШКЭЪЕЪБадЁЃвдЫЋПкRAMЙЙГЩЕФЪ§ОнНгПкПЩвддкСНИіДІРэЦїжЎМфНјааИпЫйПЩППЕФаХЯЂДЋЪфЁЃДЫЭтЃЌЫЋПкRAMПЩвдгІгУдкжЧФмзмЯпЪЪХфПЈЁЂЭјТчЪЪХфПЈжазїЮЊИпЫйЪ§ОнДЋЪфЕФНгПкЁЃдкаэЖрПэДјаХКХДІРэСьгђ(ШчЮоЯпЭЈаХЁЂЖрУНЬхЯЕЭГЁЂЮРаЧЭЈаХЁЂРзДяЯЕЭГЕШ)ЃЌFPGAММЪѕвбДњЬцDSPЪЕЯжаэЖрЧАЖЫЕФЪ§зжаХКХДІРэЫуЗЈЁЃгУFPGAРДЪЕЯжЪ§зжаХКХДІРэФмКмКУЕиНтОіВЂааадКЭЫйЖШЮЪЬтЃЌЖјЧвЦфСщЛюЕФПЩХфжУЬиадЃЌЪЙЕУFPGAЙЙГЩЕФЪ§зжаХКХДІРэЯЕЭГвзгкаоИФЁЂВтЪдМАЯЕЭГЩ§МЖЃЌНЕЕЭЩшМЦГЩБОЃЌЫѕЖЬПЊЗЂжмЦкЁЃШЮКЮвЛжжздЖЏПижЦЯЕЭГЖМРыВЛПЊЪ§ОнВЩМЏЯЕЭГЃЌЪ§ОнВЩМЏЯЕЭГЕФжЪСПжБНггАЯьећЬхЯЕЭГЕФЙЄзїадФмЁЃЪ§ОнВЩМЏЯЕЭГИпЫйЁЂЪЕЪБЗЂеЙЧїЪЦЃЌЖдЪ§ОнЕФДЋЪфКЭПижЦЫйЖШЬсГіНЯИпвЊЧѓЁЃЖјВЩгУЫЋПкRAMПЩгааЇЬсИпЫйЖШЃЌНтОіЫйЖШЦЅХфЮЪЬтЁЃ ЩшМЦlПщЪ§ОнВЩМЏЯЕЭГАхЃЌгУFPGAЪЕЯжЫЋПкRAMЙІФмЃЌВЂЧвПижЦAЃЏDВЩбљгызЊЛЛЃЌвдМАЪ§ОнаДШыЫЋПкRAMЁЃРћгУЕЅЦЌЛњПижЦЫЋПкRAMЕФДцШЁЃЌЙЙГЩвЛИіЖРСЂЕФЪ§ОнВЩМЏЯЕЭГЃЌВЂПЩвдЭЈЙ§ДЎааНгПкАбЪ§ОнЗЂЫЭИјPCЛњЁЃЭМ3ЮЊЦфЯЕЭГНсЙЙПђЭМЁЃ  ЪзЯШЃЌЪБжгВњЩњЦєЖЏаХКХЃЌFPGAЯђВЩбљПЊЙиЗЂГібЁЭЈаХКХЃЌбЁЖЈФЃФтПЊЙиВЩбљЃЌЕк0ТЗФЃФтСПНјШыЃЌОAЃЏDзЊЛЛКѓБфЮЊ8ЮЛЪ§зжСПВЂДцДЂгкЫЋПкRAMжаЃЌADC0809ЗДРЁИјFPGAФкПижЦЕчТЗВЂИцжЊзЊЛЛЭъБЯЃЌFPGAФкПижЦЕчТЗдйбЁЭЈЕк1ТЗФЃФтСПНјШыЃЌжиИДЩЯЪіЙ§ГЬЁЃОЙ§0ЃЎ1 msКѓЃЌЪБжггжВњЩњвЛИіТіГхЦєЖЏаХКХЁЃFPGAгжжиаТДгЕкOТЗФЃФтСПбЁЭЈЁЃ дкЪБжгТіГхаХКХ0ЃЎ1 msЙ§ГЬжаЃЌFPGAЫГађЭЈЙ§0ЁЋ7ТЗФЃФтПЊЙиЃЌдкУПДЮбЁЭЈЪБаыХаЖЯЪЧЗёЮЊЕк7ТЗФЃФтСПЃЌШєЪЧдђFPGAВЛдйЯьгІAЃЏDЗДРЁаХКХЃЌЖјЪЧЕШД§0ЃЎ1msЕФЪБжгТіГхаХКХЕНДядйжиаТПЊЪМЙЄзїЁЃЕЅЦЌЛњгУгкгыЭтВПPCЛњЭЈаХЃЌPCЛњВщбЏЪЧЗёдкЫЋЖЫПкRAMжагааТЪ§ОнЃЌВЂОНгПкЕчТЗЖСШЫЪ§ОнЁЃЦфжаЫЋПкRAMОпга2зщЖРСЂЕФЪ§ОнЁЂЕижЗКЭПижЦзмЯпЃЌПЩЖдШЮКЮвЛИіЖЫПкНјааЖРСЂЕФВйзїЁЃШєЮДВЩгУЫЋПкRAMЃЌFPGAВЩШЁжаЖЯЗНЪНЖдCPUДЋЪфЪ§ОнЪБЃЌCPUОЭЛсЭЃжЙЕБЧАЙЄзїЖјШЅДІРэЭтВПЧыЧѓЃЌЕБДІРэЭъЭтВПЪТМўКѓдйЛиЕНдРДБЛжажЙДІЃЌМЬајдРДЕФЙЄзїЃЌетбљЛсгАЯьCPUЕФЫйЖШЁЃвђДЫв§ШыЫЋПкRAMДцДЂFPGAДЋЫЭРДЕФЪ§ОнЃЌШЛКѓCPUдйДгЫЋПкRAMжаЖСЪ§ЃЌДгЖјЬсИпаЇТЪЁЃБОЪ§ОнВЩМЏЯЕЭГВЩгУЛљгкFPGAЫЋПкRAMЁЂЕЅЦЌЛњЕШЪЕЯжЪ§ОндЫааДІРэКЭПижЦЙІФмЃЌЪЙЯЕЭГЕФЭЈаХКЭДІРэФмСІДѓДѓМгЧПЃЌБЃжЄСЫЯЕЭГЕФЪЕЪБадЃЌПЩвдСщЛюЕиЭЈЙ§ЖржжЗНЪНПижЦЪ§ОнЖСаДЁЃ 4 НсЪјгя БОЮФГфЗжРћгУFPGAФкВПЗсИЛЕФгВМўзЪдДКЭVerilog HDLгябдЕФСщЛюадЃЌдкFPGAФкЪЕЯжСЫЫЋПкRAMЕФЛљБОЙІФмЃЌВЂЭЈЙ§ЩшМЦвЛПщЪ§ОнВЩМЏАхНщЩмЛљгкFPGAММЪѕЕФЫЋПкRAMЕФгІгУЃЌИУЯЕЭГМѕаЁСЫЩшМЦЕчТЗЕФИДдгадЃЌдіЧПСЫЩшМЦЕФСщЛюадКЭзЪдДЕФПЩХфжУадЁЃећИіЯЕЭГЗжЙЄУїШЗЃЌЙЙГЩКЯРэЃЌОпгавЛЖЈЕФгІгУМлжЕЁЃ |

ЭјгбЦРТл