时钟分配芯片在调整并行数据采集中的作用

发布时间:2010-8-18 16:35

发布者:lavida

|

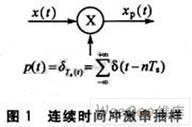

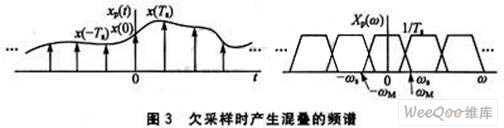

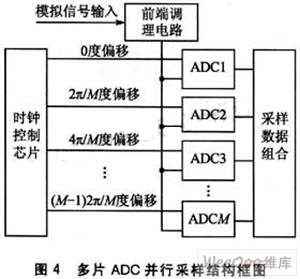

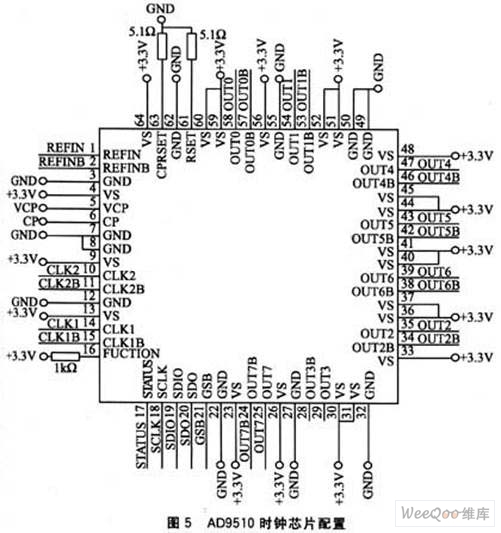

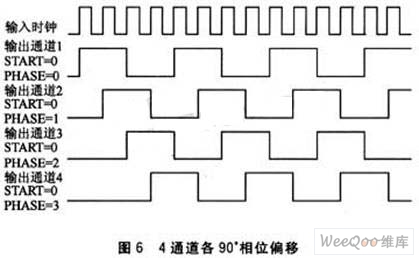

1 经典采样理论 模拟世界与数字世界相互转换的理论基础是抽样定理。抽样定理告诉我们,如果是带限的连续信号,且样本取得足够密(采样率ωs≥2ωM),那么该信号就能唯一地由其样本值来表征,且能从这些样本值完全恢复出原信号。连续时间冲激串抽样如图1所示,其时域波形和相应的频谱如图2所示。   根据采样定理,如果样本点取得不足(ωs  2 多片ADC采样方式 单片ADC采样是最常见的。调理过的信号通过单片ADC芯片转换成数字信号,供给后续电路进行数字处理。这种采样方式对于一般应用的场合是可以满足要求的,而且器件连接简单,成本低。而在高速采样的场合,只有提高单片ADC芯片的采样率才能满足要求。然而,通常高速ADC芯片都是很昂贵的;而且由于设计制造工艺,以及存储器读写速度的限制,不可能无限制地提高单片ADC的采样率。这就严重限制了单片ADC在高速采样系统中的应用。本文采用多片ADC并行采样的方式来提高系统的实时采样率。 多片ADC芯片并行采样的方式可以弥补单片ADC芯片采样率低的不足。通过对ADC芯片时钟的精确控制,可使采样系统在单位时间内获得更多的样本信息。理论上,如果单片ADC芯片的采样速率是f,那么通过M片ADC芯片的并行采样,可以实现M·f的采样率。多片ADC并行采样的结构框图如图4所示。  3 系统实现及时钟芯片配置 如上所述,利用M片ADC芯片理论上可以把采样率提高到单片ADC的M倍。那么利用4片采样率为250 Msps的ADC芯片AD9481,可以把采样率提高到1 Msps水平。其中时钟芯片的配置是设计的重要环节。 AD9510是有美国模拟半导体公司推出的一款精确时钟分配芯片。它具有2路1.6 GHz的差分时钟输入、8路时钟输出以及片上PLL核。其中,包括4路独立的1.2 GHz LVPECL时钟输出。另外4路独立的时钟输出可设置成LVDS或CMOS:设置成LVDS输出时,频率可以达到800 MHz;设置成CMOS输出时,频率可以达到250 MHz。同时,该款芯片还能通过SPI串行编程来控制输出时钟间的相位延迟,且抖动和相位噪声极低。  AD9510时钟芯片的配置如图5所示。其中,1、2引脚为PLL时钟参考输人。16脚内部接30 kΩ的下拉电阻,可以通过编程实现复位、同步和下拉。如果该脚悬空,默认作复位用,所以通常接1 kΩ电阻接地。18~21脚为与MCU的串行通信口。通过串行方式,可以对芯片进行设置。其中,通过49H到57H中奇数寄存器的配置,可以实现对每个通道相位的控制。每个分频通道有4位的相位偏移控制和1位起始控制。在同步脉冲来临后,相位延时字决定分频输出等待多少个输入时钟周期。相位延时的起始位决定输出是从低电平开始,还是从高电平开始。这样,通过对不同输出通道参数的控制,可以很容易实现通道间相位的90°偏移。4通道各90°相位偏移如图6所示。  将每个通道的输出设置为4分频和50%占空比。把通道1设置为低电平起始,0输入时钟延时;把输出通道2设置为低电平起始,1个输入时钟延时;把输出通道3设置为低电平起始,2个输入时钟延时;把输出通道4设置为低电平起始,3个输入时钟延时。这样就实现了图6中相位相差90°的4通道输出。通过时钟芯片配置产生相差90°的采样时钟提供给4片采样芯片AD9481,可以使总的采样率达到1 Gsps的水平。 结 语 本文通过对时钟分配芯片AD9510的正确配置,采用ADC芯片AD9481实现了4个通道90°相位偏移的高速时钟输出,从而大大提高了系统采集速度。 需要注意的是,多片ADC并行采样的方式势必引入通道适配误差,在后续的处理上必须引起足够的重视。 |

网友评论