基于SPI方式DSP外部E2PROM接口设计

发布时间:2010-8-18 16:28

发布者:lavida

|

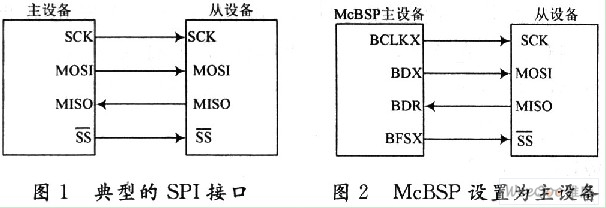

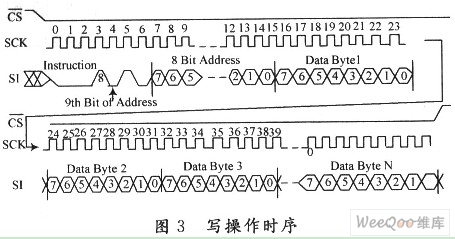

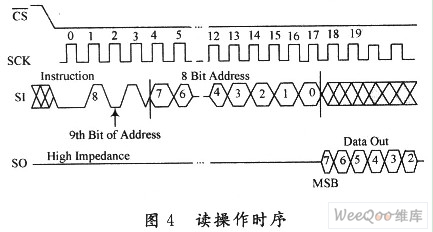

近年来,随着DSP技术的普及、高性能DSP芯片的出现,DSP已越来越多地被广大的工程师所接受,并越来越广泛地被应用于各个领域,例如:语音处理、图像处理、模式识别及工业控制等,并且已日益显示出其巨大的优越性。DSP是利用专门或通用的数字信号处理芯片,以数字计算的方法对信号进行处理,具有处理速度快、灵活、精确、抗干扰能力强、体积小及可靠性高等优点,满足了对信号快速、精确、实时处理及控制的要求。 在语音处理、图像处理、模式识别及工业控制中,少不了对必要的数据进行存储保护。如果存储在内外RAM之中,掉电数据就丢失,起不到保护数据的作用;存储在FLASH中,由于对FLASH进行数据写入时,要先进行擦除操作,然后才能整页的写入,如果每次写入的数据比较少,这样就要占据很大的CPU时间,操作比较麻烦。 针对这些缺点,根据多年的研发经验,结合实际,提出一种基于SPI方式的外部数据扩展方式。本文所用到的数据存储器是Xicor公司生产的带有块锁保护的4 Kb CMOS串行E2PROM X5043(接口符合SPI协议)。该器件利用Xicor专有的直接写入晶片,提供最小为10万次擦写和最少100年的数据保存期。数据写入之前不需要外部进行擦除操作,芯片本身自动完成。同时X5043还具有上电复位、看门狗定时器、电源电压监控四种常用的功能。这种组合不但降低了系统成本、减少了电路板空间,还增加了系统可靠性。 1 SPI协议 图1是典型的SPI协议。SPI协议采用主从设置,相互连接的设备中一个作为主设备,其他的设备作为从设备。接口连线主要包括4条信号线:串行数据输入信号线,(Master In Slave Out,MIS());串行数据输出信号线(Master Out Slave In,MOSI);移位时钟信号线(SCK);从设备片选信号线(SS)。  2 VC5402的多通道缓存串行口(McBSP) 2.1 McBSP的功能特点 TMS320V5402是TI生产的第二代低功耗定点数字信号处理器,提供了两个高速、全双工、多通道缓存串行口,每个串行口可以支持128通道,速度达100 Mb/s。McBSP是在标准串行接口的基础之上对功能进行扩展,因此,具有与标准串行接口相同的基本功能: (1)全双工通信; (2)拥有两级缓冲发送和三级缓冲接收数据寄存器,允许连续数据流传输; (3)为数据发送和接收提供独立的帧同步脉冲和时钟信号; (4)能够与工业标准的解码器、模拟接口芯片(AICs)和其他串行A/D和D/A设备直接连接; (5)支持外部移位时钟或内部频率可编程移位时钟。 此外,McBSP还具有的其他特殊功能,本文所用到的有: (1)串行字长度可选,包括8,12,16,20,24和32位可选。 (2)进行8位数据传输时,可以选择LSB或MSB为起始位; (3)帧同步脉冲和时钟信号的极性可编程; (4)内部时钟和帧同步脉冲的产生可编程,具有相当大的灵活性。 2.2 McBSP与X5043的接口设计 X5043的外部接口符号SPI协议规范。DIP封装的X5043有8个管脚组成,各个管脚功能如下所示: CS:片选端,当CS为低时,X5043选中。在任何操作之前,需要先在CS上有一次由高至低的跳变; SO:串行数据输出端,当读周期时,数据从该引脚移出; SI:串行数据输入引脚,所要写入存储器的操作码,字节地址和数据都从该引脚输入; WP:当WP为低时,向X5043的非易失性写被禁止,但器件其他功能正常,为高时,所用功能都正常; SCK:串行时钟端。串行时钟控制串行总线数据输入和输出的时序。 McBSP的时钟停止模式与SPI协议兼容。当McBSP处于时钟停止模式时,发送器和接收器是内部同步的,因此可以将McBSP作为SPI主设备或从设备。当设置McBSP为主设备时,发送端输出信号DXR就作为SPI协议的MOSI信号,接收端输入信号DRR就作为SPI协议的MISO信号。发送帧同步脉冲信号FSX作为从设备片选信号SS,而发送时钟信号CLKX就与SPI协议的串行时钟信号SCK相对应。由于接收时钟信号CLKR和接收帧同步脉冲信号FSR与发送端的相应部分CLKX和FSX在内部相互连接,因此这些信号不用于时钟停止模式。该设计中McBSP作为主设备使用。X5043与McBSP的接口电路如图2所示。 3 软件设计 软件设计主要包括DSP相关寄存器的配置,X5043状态寄存器的配置,以及X5043的读写操作。 3.1 寄存器的配置 DSP端需要配置的寄存器主要包括CLKMD,SPCR[1,2],XCR[1,2],RCR[1,2],SRGR[1,2],PCR等。 其中CLKMD主要配置DSP的时钟;XCR[1,2],RCR[1,2]主要配置接收和发送数据的帧的个数、帧长以及字长。根据对X5043操作的不同,发送和接收的字长也不同,但是针对某一种操作,接收和发送字长是一样的;SRGR[1,2]主要是对CLKGDV,CLKSM,FSGM三个位域的配置;SPCR[1,2]主要是对CLKSTP位域的配置,因为它决定了McBSP是采用时钟停止模式(SPI模式)还是正常模式;引脚控制寄存器(PCR)配置了各个引脚的工作状态。 值得注意的是在配置McBSP的寄存器之前,首先要使发送、接收和分频器复位,配置完SPCR[1,2],XCR[1,2],RCR[1,2],PCR后,使分频器置位,等待两个时钟周期,在配置SRGR[1,2],然后使发送和接收置位在等待两个时钟周期,这时才可以进行其他操作。 3.2 X5043的读写操作 X5043的读操作包括读状态寄存器、读存储器阵列(即读数据)。写操作包括写使能/写禁止、写状态寄存器、写存储器阵列(写数据)。X5043的指令组如表1所示。 下面主要讲一下对单个数据的读写操作。 3.2.1 写一个字节操作 写操作之前必须写使能,即向X5043先发送数据(06H)。首先将CS拉低,然后向器件输入WREN指令,在将CS拉高。再次将CS拉低并输入WRITE指令,后面跟随8位地址,在后面需要写入的数据。WRITE指令的位3是地址位A8,它选择是阵列的高半部分还是低半部分。如果CS在WREN和WRITE之间没变为高,则WRITE指令被忽略。写操作时序如图3所示。  在字节的最后一个位0写入后,CS必须被拉高。如果它在其他时间拉高,写操作不完全。在存储器写操作之后跟随一次非易失性写操作。可以通过读状态寄存器的WIP位来判断非易失性写是否结束。只有非易失性写结束之后才可以进行下次写操作。 值得注意的是McBSP在SPI模式下,只有数据发送的时候CLKX端才有时钟输出,FSX端才输出低电平的帧同步信号。因为在发送写使能和写数据指令之间要求CS(即FSX)变高,所以DSP要分两次把数据送给X5043。且这两次发送的字长不同(写使能一个字节,写数据三个字节),所以在发送之前需要重新配置McBSP。 3.2.2 读一个字节操作 当从E2PROM存储器阵列读数据时,首先CS通过FSX引脚拉低为低电平,然后送READ指令到器件,后面跟随8位地址,在后面就是发送8位无意义的数据(目的是为了继续产生时钟信号)。发送结束后,所选地址中的数据从SO端移出到McBSP的数据接收引脚。读操作时序如图4所示。  读操作和写操作一样,都是发送三个字节的数据,所以McBSP的串口字长要配置为24位。读操作发出以后,通过查看SPCR1寄存器的RRDY位来判断接收数据是否完成,若RRDY为1,则读DRR寄存器获取数据。 3.3 值得注意的地方 无论是写使能/写禁止、写状态寄存器还是写数据,当McBSP相应数据发送结束后,McBSP的时钟和帧同步信号都将变为无效状态,这种无效状态要保持至少10μs之上(否则数据将无法正确写入),然后在读取X5043的状态寄存器,判断非易失性写是否结束,结束了才可以进行其他操作。 4 结 语 通过SPI接口外接E2PROM,简化了硬件电路,提高了系统的可靠性和开发难度,具有很实际的应用价值。 |

网友评论