10~37GHz CMOS四分频器的设计

发布时间:2010-8-18 11:01

发布者:lavida

|

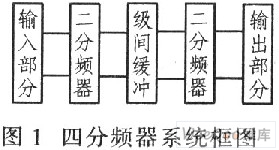

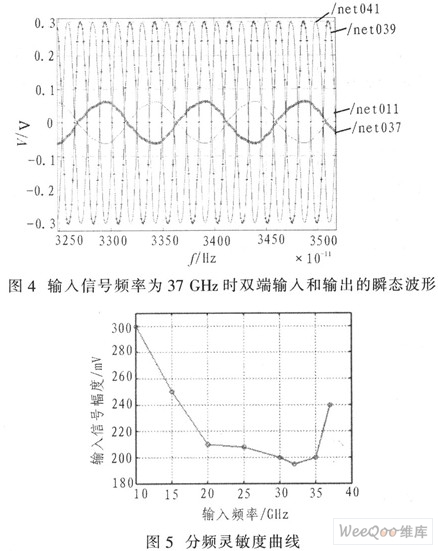

1 引言 随着通信技术的迅猛发展,人们对通信系统中单元电路的研究也越来越多。而分频器广泛应用于光纤通信和射频通信系统中,因此,高速分频器的研究也日益受到关注。分频器按实现方式可分为模拟和数字两种。模拟分频器可由注入锁定等结构实现,一般具有工作频率高、功耗低等优点,但是分频范围较小,芯片面积较大。数字分频器基于触发器结构,一般分频范围较宽,芯片面积较小,但相对于模拟分频器其工作频率较低,功耗较大。这里采用UMC 0.13 um的CMOS工艺(其特征频率fT约100 GHz),在电源电压为1.2 V时,实现一个高速、宽分频范围的数字四分频器。 2 电路设计 图1为四分频器的系统框图。它由两个二分频器级联而成。为了实现级间隔离和电平匹配,在两个二分频器之间加入级间缓冲电路。为便于区分这两个分频器,将前一个二分频器称为高速二分频器,后一个二分频器称为低速二分频器。因为要测试电路,需考虑输入和输出端口的阻抗匹配。为解决这些问题,电路中设计输人和输出部分。输入部分除实现输入阻抗匹配外,还要提供直流偏置。输出部分用以保证测试时的阻抗匹配以及得到一定的输出信号幅度。  2.1 二分频器 这里采用的二分频器为全差分的共栅动态负载结构,其框图和电路图如图2a和图2b所示。  该二分频器由两个相同的相互交叉耦合的D触发器构成,其中CLK和CLKn为一对差分输入信号。由于两个触发器完全相同,下面仅以图2b中左边的触发器为例进行分析。当CLK为低电平时,电路工作在采样模式,开关管VMa5导通,输入对管VMn3、VMn4用于采样输入信号,PMOS负载管VMp1、VMp2工作在线性区,其导通电阻很小,相应的时间常数RC就较小,从而使得输出结点Q,Qn的状态转换时间较短; 当CLK为高电平时,电路工作在保持模式,开关管VMn5截止,PMOS负载管VMp1、VMp2工作在截止区,相应的时间常数很大,而NMOS的交叉耦合对管VMn1、VMn2形成正反馈,在保持模式下用于维持触发器的输出状态,在采样模式下加快输出节点的状态转换速度。因此该主从结构的触发器形成一个二分频器。动态负载技术极大地提高了分频器的工作速度。 本文目的是设计高速分频器,因此其工作速度是考虑的首要问题。触发器中决定工作速度的主要因素是输出节点的总电容。同样以图2b中左边的触发器为例说明,考虑其中一个输出节点Qn相应的总电容,包括与该输出节点相连的所有器件的电容以及它们两者之间连线上的寄生电容。因此在进行电路参数设计和版图设计时,应减少这些电容。在设计两个二分频器电路参数时,虽然两者拓扑结构一样,但由于侧重点不同,所以参数设计并不相同。高速二分频器着重提高其工作速度,因此应尽可能地减少输出节点的电容。而低速二分频器的工作速度为高速二分频器的一半,故速度不是考虑的主要问题。因此在对低速二分频器电路参数设计时,在满足二分频的条件下应着重降低其功耗。另外分频器的输出电压摆幅应从两方面考虑:首先输出电压摆幅过大,则充、放电过程持续时间会增加,输出电压摆幅过小,则无法驱动后续电路。而决定输出电压幅度的主要因素为在保持模式下动态负载管的电阻,因此在设计电路时应进行折衷考虑,仔细调整各管子的参数。在版图设计时,对于管子宽度比较大的应尽量使用叉指结构,同时应特别注意图2中的4条交叉耦合线应尽可能短,尤其是高速二分频器中的4条交叉耦合线对分频器的工作速度有很大的影响。 2.2 级间缓冲电路 级间连接要解决的主要问题是相邻两级之间的电平匹配和隔离。因为高速二分频器的输出直流电平约为800 mV,而低速二分频器的输入直流电平为300 mV,因此需要在两级之间加入缓冲器进行电平匹配。同时由于低速二分频器为共栅级输入,其输入阻抗很小,直接接在高速二分频器后会对其产生过重的负载,所以需要在两级之间加入缓冲器进行隔离。在设计过程中,为能使低速二分频器正常工作,级间缓冲输出后的信号幅度要大。 这里级间缓冲电路采用一个差分放大器级联一个源级跟随器。传统的缓冲电路只采用源级跟随器解决前后级的电平匹配和阻抗匹配等问题。而该设计中,缓冲电路输入端信号的工作速度很高,必须达到足够的摆率才能使电路正常工作,因此源级跟随器的尾电流源和输入管的栅宽设计的较大。如果直接接在高速二分频器后面会对其速度影响很大,所以在源级跟随器前加一级差分放大器,并将其输入管的栅宽设计的较小。差分放大器可以减小缓冲器对高速二分频器的影响,另外也可以提高高速二分频器的输出信号的幅度。 3 后仿真结果 该四分频器采用UMC 0.13μm 1层多晶硅和8层金属的CMOS混合信号工艺技术。首先利用UMC公司提供的库文件在HSPICE软件下对电路进行前仿真,然后在Cadence环境下进行版图设计并提取寄生参数后,对电路后仿真。图3为四分频器的版图。其芯片面积为(0.33x0.28)mm2。  分频器在最高工作频率37 GHz下的差分双端输入和输出的后仿真波形如图4所示。图5为该分频器的分频灵敏度曲线。从图5可看出,该分频器工作在32 GHz附近时,所需单端输入信号幅度为180 mV。分频器在10"37 GHz的频率范围内都可以正常工作。  4 结论 介绍一种超高速,宽分频范围的四分频器的设计。后仿真结果表明该四分频器的最高工作频率为37 GHz,当输入信号的幅度为300 mV时,分频范围为27 GHz。在电源电压为1.2 V,工作在37 GHz时,该电路的功耗小于30 mW。该四分频器可应用于光纤通信和其他超高速电路。 |

网友评论