基于DP标准发射端扩频时钟发生器电路设计

发布时间:2010-8-18 10:55

发布者:lavida

|

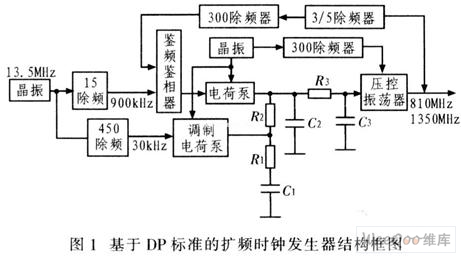

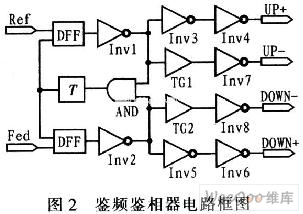

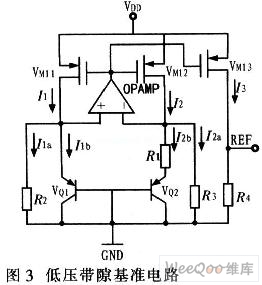

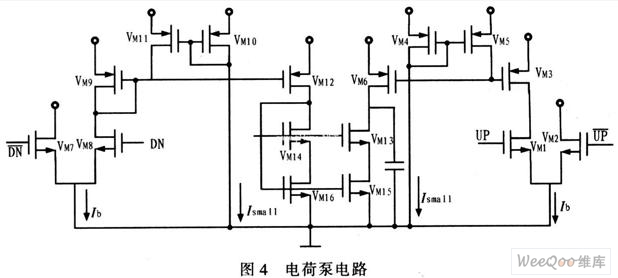

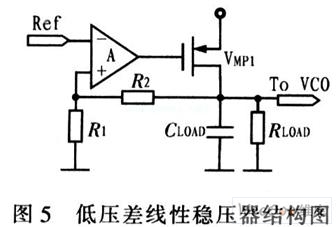

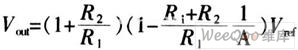

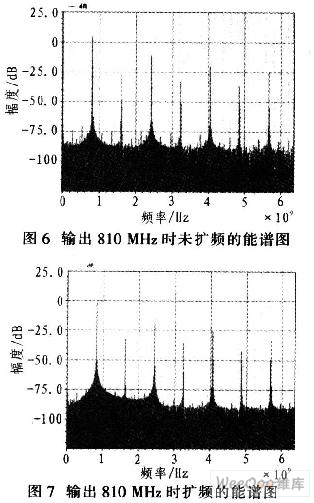

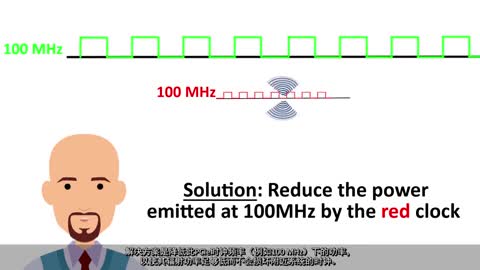

1 引言 DP(DisplayPort)接口标准旨在寻求代替计算机的数字视频接口DVI、LCD显示器的低压差分信号LVDS(Low Voltage Differential Signal),作为设备间和设备内的工业标准,并在若干领域跃过DVI和高清晰多媒体接口HDMI这两种接口技术。DP利用目前交流耦合电压差分的PCI Express电气层,有1"戽个工作速率为217 Gb/s的数据对(Lanes),最高可获得4通道多达10.8 Gb/s的带宽。时钟不是分离的,而是内置于Lanes。传输命令和控制的辅助数据通道是双向的,最高传输比特率可达1 Mb/s。DP支持的最大传输距离为15 m,而其工作电平比DVI更低。 伴随电子产品性能的不断提高,其微处理器的频率也在不断增加,由此产生的电磁干扰会影响电子产品的正常。为了抑制电磁干扰,人们先后研究出屏蔽、脉冲整形、滤波、低电压差分时钟、特殊版图布局、扩频时钟发生器等方法,其中扩频时钟发生器可有效减小峰值和谐波的功率,且可通过电路设计的广阔空间实现,因而得到广泛应用。这里设计一种基于DP标准采用μ工艺的发射端扩频时钟发生器。合理设计锁相环路,采用外加滤波器对压控振荡器的控制电压进行三角波调制,得到所需的扩频时钟。 2 扩频时钟发生器总体结构 降低电磁干扰(EMI)是电子系统设计人员需要考虑的重要因素,扩频时钟(CLK)为降低EMI提供一个有效途径。这里采用tsmc0.18μm 工艺设计一款符合DisplayPort标准发射端的扩频时钟发生器。在合理设计锁相环路的基础上,运用外加电荷泵对压控振荡器的控制电压进行三角波调制,得到所需要的扩频时钟。图1为该设计结构框图。  3 各模块电路设计 3.1 鉴频鉴相器电路 图2为鉴频鉴相器电路框图。鉴频鉴相器的输出由输入信号的频率和相位决定,它比较两个输入信号的上升沿,当输入参考时钟信号Ref的上升沿超前反馈信号Fed的上升沿到达鉴频鉴相器时,鉴频鉴相器的输出UP为高,而此时DOWN保持为低电平,当Fed的上升沿也到来时,输出被复位;当信号Fed的上升沿超前参考信号Ref到来时,输出DOWN为高,当Ref的上升沿也到来时,鉴频鉴相器被复位。因此,鉴频鉴相器根据输入信号相位差来驱动后级电路。比较两个输入信号的相位差,然后将其转变成两个数字信号来控制电荷泵的工作状态。在本设计中,由于参考输入频率仅为900 kHz,因而对鉴频鉴相器的工作速度要求并不高。因此,在满足低功耗要求的前提下,采用最简单的无死区鉴频鉴相器的结构。  为了避免死区,在复位路径中引入延时T。在设计延时时长时,首先应考虑鉴频鉴相器的工作频率。因为鉴频鉴相器的最高丁作频率为1/2Tdelay,Tdelay包括插入延时和鉴频鉴相器的内部延时。要求插入延时的引入不影响鉴频鉴相器的正常工作;另外需考虑当插入延时相对较长时,电荷泵的充、放电电流同时开启的时间就会变长,而电荷泵存在的失调就会在滤波器电容上引入抖动,即增加锁相环输出的杂散成分。因此,在鉴频鉴相器内部延时可忽略及充分开启电荷泵的前提下,应尽量减小失调。这里插入延时取8 ns。由于后级电荷泵电路为差分输入,因此采用传输门减少反相器的延时。 3.2 带隙基准电路 为满足带隙基准电路的低压应用,这里采用一种电流模式结构的低压带隙基准电路,如图3所示。该电路可以输出低于1 V的电压,有效降低了电路的电源电压;同时,电路中采用与电压无关的偏置及带负反馈网络的二级运放,降低了电路的电源敏感性。  基于0.35μm CMOS工艺的HSPICE仿真结果表明,该电路可工作在1.1"1.5 V的低电源电压下,并具有14 ppm/℃的低温度系数,能够输出200 mV~1.25 V的宽范围电压,并使用与电源无关偏置以及带负反馈网络的二级运放,提高输出电压的精度,该电路中,各MOS管都工作于饱和状态。电路中运算放大器采用二级结构,具有较高的低频增益。 3.3 电荷泵电路 电荷泵锁相环具有低功耗、高速、低抖动和低成本等特点,广泛应用于无线电通信、频率综合器、时钟恢复电路中。电荷泵电路在锁相环路(PLL)中起着非常重要的作用,其主要功能是把鉴频鉴相器(PFD)的数字信号UP和DOWN转换为模拟信号,从而控制压控振荡器(VCO)的频率。当PFD给出高精度的相位误差时,电荷泵对整个环路的性能起决定性作用。当PLL锁定在某个频率时,电荷泵电路的输出必须保持在一个常数。因此,在设计电荷泵电路时,产生一个稳定步长的电压是很重要的。实际的电荷泵不可避免的存在电荷泄漏、充放电流失配、泵开关时间延时不同等不利因素,这些因素都不同程度地造成输出频率的相位偏差,进而降低输出时钟的抗噪声性能。该系统设计采用差分电路结构,此结构具有以下优点:消除了跳跃现象;可以丁作在较高频率,满足整个PLL的设计要求;由于对称性,不易产生偏差;减小电源、地及衬底噪声的影响;NMOS与PMOS开关特性不匹配对整个性质将不再起决定性作用,原来要求NMOS与PMOS相匹配的地方,现在只需NMOS或PMOS自身相匹配即可。该电荷泵电路如图4所示,它由大摆幅电流镜及由上拉泵和下拉泵电路所构成的对称电荷泵所组成,属于全差分型电荷泵电路。上拉泵和下拉泵均由差分输入对V M1和VM2,电流镜VM3,偏置电流源Ib和ISMALL,以及弱上拉电流镜VM4和VM5所组成。该电路是一种新的全差分电荷泵结构,与传统电荷泵电路相比,该电路具有输出范围宽和无跳跃现象等优点,同时还可以有效地解决电荷泄漏和充放电失配等问题。 3.4 调制电荷泵电路 采用调制电荷泵三角波调制压控振荡器的控制电压以达到扩频的效果。文献中给出了调制电荷泵的参数:调制电流为2.33μA,调制频率为30 kHz。电荷泵的输出都是采用单管,而不是更有利于抑制失配度的级联管,原因在于级联管限制了电荷泵的电压输出范围,压控振荡器在1.15~2.43 V线性范围内不是所有情况下都能处于饱和区工作。该设计通过增加管子的栅长L,即增加从管子漏端看进去的电阻来减小失配度,而管子增大所引起的时钟馈通及电流泄露等问题比电流失配对系统的影响小。  3.5 滤波器电路 环路滤波器(LPF)连接在电荷泵和压控振荡器之间,它决定锁相环的基本频率特性。实际上,正是由于环路滤波器的存在,锁相环才可以选择工作在任意中心频率和带宽内。环路滤波器可以采用无源滤波器或有源滤波器。该设计采用无源低通滤波器,用基于锁相环交流频域特性分析的方法。在该滤波器的设计中,如果锁相环带宽、相位裕度和零极点选择合理,只需经过1~2次试算,就可以得到正确结果。这种设计方法的优点是直接以锁相环的交流特性为出发点,利用使系统稳定的简单条件,就可以设计出环路滤波器。这为低相位抖动、快速锁定锁相环的行为级设计提供了一种快速准确的途径。 3.6 压控调节器电路 考虑到压控振荡器易受到电源噪声的影响,而压控振荡器的性能是整个锁相环系统的关键,所以为压控振荡器提供1个稳定的电源电压是非常必要的。本文采用折叠式共源共栅结构,如图5所示。  图5中,补偿电容为4.7 μF,基准点电压Ref来自带隙基准,输出电压由反馈电阻和运放增益决定:  为了减小输出电压的误差,需要设计增益较大的运放,考虑到环路的稳定性及环路建立时间,把补偿电容的极点作为整个环路的主极点,这就要求运放具有较高的带宽。 用负载电阻模拟压控振荡器,取Rload为150~500 Ω,输出5.2~18.8 mA电流来提供压控振荡器的电流,这一输出范围对运放的电压输出范嗣提出严峻要求。为了提高输出电压的电源抑制,可以设计输出管VMP1工作在饱和区,但这就降低了低压差线性稳压器的效率(近似为输出电压与电源电压的比值);另外也可通过增加VMP1,管的栅长来提高电源抑制,但这样就使得运放的主极点减小,整个环路稳定性变差。低压差线性稳压器的设计还需综合考虑电荷泵输出电压,压控振荡器线性工作范围等因素。 3.7 压控振荡器电路 电源噪声是造成PLL输出时钟抖动最主要的原因,而锁相环内部最易受噪声影响的模块为压控振荡器(VCO),本文采用一种高电源噪声抑制、高线性范围的压控振荡器,它通过高电源抑制比的电压调节器对受噪声干扰的外部电源进行预处理,产生稳定的内部电源,从而减小外部电源噪声对VCO核心电路的影响,同时,也改进电压一电流转换(V-IConverter)电路,提高VCO电压频率转换特性的线性范围,减小VCO非线性增益对PLL输出抖动的影响。 4 扩频时钟发生器整体电路仿真 图6、图7分别为输出810 MHz的扩频前后的能谱图,而图8、图9分别是输出1 350 MHz时扩频前后的能谱图。   由图6和图7、图8和图9对比可以看出,扩频后,基频和谐波的能量有一定下降,该设计得到了比较满意的效果。 5 结束语 降低电磁干扰(EMI)是电子系统设计人员需要考虑的一个重要因素,扩频时钟(CLK)为降低EMI提供了一个有效途径。该设计是一款用于发射端时钟产生的锁相环,其创新点在于:在综合考虑数模混合电路的功耗。性能等方面因素的基础上,对各模块电路进行优化,为电荷泵和压控振荡器提供稳定的电流和电压,且采用三角波调制压控振荡器控制电压的方法对时钟扩频,减小电磁干扰。整体的电路级仿真验证表明,该设计符合DP标准的性能要求。 |

网友评论