Т»ёцёДҪшРНCMOSөзәЙұГЛшПа»·өДЙијЖ

·ўІјКұјдЈә2010-8-17 16:35

·ўІјХЯЈәlavida

|

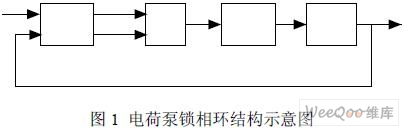

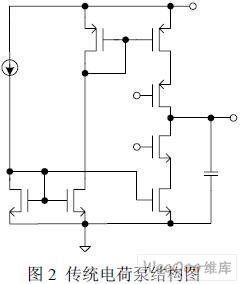

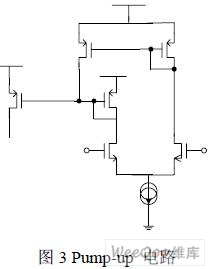

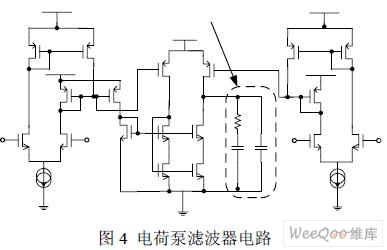

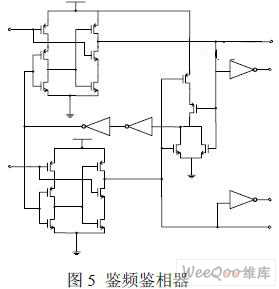

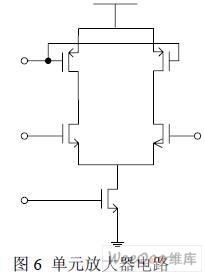

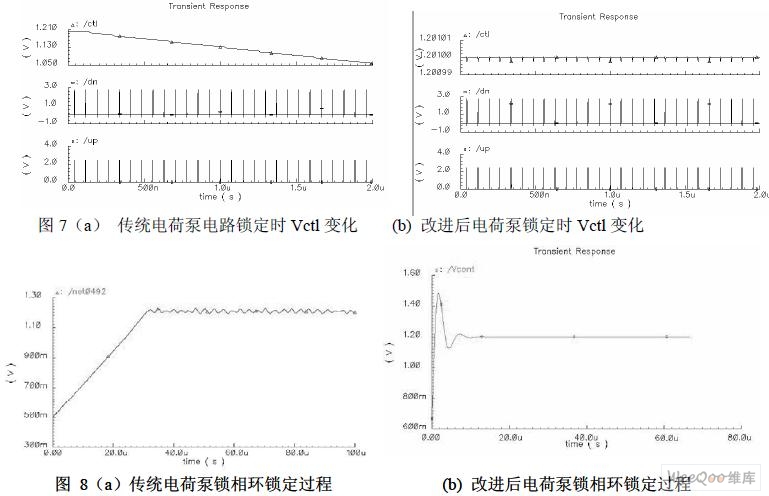

1 ТэСФ ЛшПа»·КЗДЈДвј°КэДЈ»мәПөзВ·ЦРөДТ»ёцЦШТӘДЈҝйЈ¬ФЪёчЦЦЛшПа»·Ҫб№№ЦРЈ¬өзәЙұГЛшПа»· ЈЁCPPLLЈ©ТтЖдОИ¶ЁРФёЯЈ¬І¶ЧҪ·¶О§ҙуЈ¬ЗТјшЖөјшПаЖчЈЁPFDЈ©ІЙУГКэЧЦөзВ·Ј¬ұгУЪјҜіЙөДМШ өг¶шұ»№г·әУҰУГУЪОЮПЯөзНЁРЕЎўЖөВКЧЫәПЖчЎўКұЦУ»ЦёҙөзВ·ЎЈөзәЙұГЈЁCharge PumpЈ©КЗЛш Па»·өзВ·ЦР№ШјьДЈҝйЈ¬¶ФХыёцЛшПа»·өДРФДЬЖрЧЕҫц¶ЁРФөДЧчУГЈ¬ө«КЗҙ«НіөДөзәЙұГІ»ҝЙұЬГв өШҙжФЪөзБчФҙК§ЕдЈ¬өзәЙ№ІПнөИ·ЗАнПлОКМвЎЈ ұҫОДХл¶Фҙ«НіРНөзәЙұГөзВ·ҙжФЪ·ЗАнПлРФөДОКМвЈ¬¶Фҙ«НіCPPLL ҪшРРБЛёДҪшЈ¬ФЪ chartered 0.35um №ӨТХПВЈ¬НЁ№эCadence Spectre №ӨҫЯ·ВХжСйЦӨЈ¬Ҫб№ыПФКҫЈ¬ХвЦЦёДҪшМб ёЯУРР§өДПыіэБЛ·ЗПЯРФОКМвөјЦВөД¶¶¶ҜЈ¬ІўјхЙЩБЛІ¶ЧҪКұјдЎЈ 2 CPPLL ФӯАнј°өзәЙұГ өзәЙұГЛшПа»·өД»щұҫЧйіЙИзНј 1 ЛщКҫЈ¬°ьАЁјшЖөјшПаЖчЈЁPDFЈ©ЎўөзәЙұГЈЁCPЈ©Ўў»·В·ВЛ ІЁЖчЈЁLPFЈ©әНС№ҝШХсөҙЖчЈЁVCOЈ©ЎЈјшЖөјшПаЖчұИҪПКдИлРЕәЕәНКдіцРЕәЕөДПаО»УлЖөВКІоЈ¬ ІъЙъҝШЦЖРЕәЕёшөзәЙұГЈ¬өзәЙұГПаУҰөШёшөННЁВЛІЁЖчід·ЕөзЈ¬өННЁВЛІЁЖчКдіцөДҝШЦЖөзС№ҝШ ЦЖС№ҝШХсөҙЖчөДКдіцЖөВКЈ¬ёГҝШЦЖөзС№УлјшПаОуІоіЙХэұИЈ¬К№С№ҝШХсөҙЖчөДЖөВКПтјшПаОуІо јхРЎөД·ҪПтұд»ҜЈ¬ЦұЦБјшПаОуІоОӘБг,ҙЛКұЛшПа»·ҪшИлЛш¶ЁЧҙМ¬ЎЈ  өзәЙұГКЗХыёцЛшПа»·В·ЦР·ЗіЈ№ШјьөДТ»ёцөзВ·Ј¬іэБЛФЪХыёц»·В·ЦР№ұПЧФцТжЦ®НвЈ¬Ль»№ ЖрөҪБЛТ»ёц»э·ЦөДЧчУГЈ¬НЁ№эәН»·В·ВЛІЁЖчЧйәПФЪТ»ЖрЈ¬ҝЙТФҪ«PDF КдіцөДПаО»ЖөВКОуІоЧӘ »»ОӘТ»ёцөзС№ЎЈҙ«НіөДөзәЙұГИзНј2 ЛщКҫЈ¬PDF өДКдіцUP әНDN ОӘКэЧЦРЕәЕЈ¬өұUP ОӘ0Ј¬DN ОӘ0 КұЈ¬ҫөПсөзБчНЁ№эM3 ПтөзИЭC ідөзЈ¬өұUP ОӘ1Ј¬DN ОӘ1 КұЈ¬өзИЭC НЁ№эM2 ·ЕөзЈ¬өұ UP ОӘ1Ј¬DN ОӘ0 КұЈ¬өзИЭЙПөДөзС№Vctl ұЈіЦІ»ұдЎЈ  И»¶шЈ¬ХвЦЦҙ«НіөДөзәЙұГөзВ·УРәЬ¶аөДҫЦПЮРФЈ¬өұM2 әНM3 ¶ј№Ш¶ПКұЈ¬өзИЭC РьёЎЈ¬ УЙУЪM1 әНM4 ¶јҙҰФЪПЯРФЧҙМ¬Ј¬ЖдВ©¶ЛөзС№·ЦұрұдОӘGND әНVDDЈ¬ФЪПВТ»ёцПаО»ұИҪПЛІ јдЈ¬M2Ј¬M3 Н¬КұҝӘЖфЈ¬ФӯАҙҙжҙўФЪөзИЭC ЙПөДөзәЙҪ«·Цұрұ»A өгәНB өгөДјДЙъөзИЭЦШРВ ·ЦЕдЈ¬өјЦВVctl ІъЙъМшФҫЎЈ БнНвЈ¬ФЪАнПлЛш¶ЁЗйҝцПВЈ¬Vctl өзС№УҰёГұЈіЦәг¶ЁЎЈө«КөјКЗйҝцКЗЈ¬өұPLL ҙҰУЪЛш¶Ё ЧҙМ¬КұЈ¬PDF КдіцөДUP әНDN РЕәЕ»бН¬КұІъЙъТ»ёц·ЗіЈХӯөДёҙО»ВціеЈ¬К№өГөзәЙұГөДБҪёц ҝӘ№ШН¬КұөјНЁЈ¬ХвКұЈ¬Из№ыөзәЙұГөДід·ЕөзөзБчЖҘЕдІ»әГЈ¬ҝШЦЖөзС№»бУРОўРЎөДІЁ¶ҜЈ¬ҙУ¶ш өјЦВVctl ¶¶¶ҜәНПаО»ФлЙщЎЈ ФЪCMOS №ӨТХПВЈ¬өзәЙ№ІПнР§УҰҝЙТФНЁ№эјУ·ҙАЎ·ЕҙуЖчОИ¶ЁAЈ¬B өгөзС№АҙПыіэЈ¬ө« ХвН¬КұФцҙуБЛГж»эЈ¬№ҰәДЎЈК§ЕдөзБчөДУ°ПмҝЙТФНЁ№эЧоРЎ»ҜјшЖөјшПаЖчҝӘНЁКұјдАҙјхРЎЈ¬ө« ХвҝЙДЬТэЖрЛАЗшЎЈ 3 ёДҪшөДөзәЙұГөзВ· ұҫОДЙијЖБЛТ»ёцЙПАӯөзВ·Ҫб№№өДөзәЙұГөзВ·Ј¬ИзНј3 ЛщКҫЈ¬ЛьУЙөзБчҝӘ№ШЈЁM1 әНM2Ј©Ўў ҫөПсөзБчёәФШЈЁM3 әН M6Ј©ТФј°ЙПАӯҫөПсөзБчёәФШЈЁM4 әНM5Ј©ЧйіЙЎЈөұ +up ОӘёЯКұЈ¬ өзБчIref И«ІҝБч№э M1Ј¬M3 әН M6Ј¬ІъЙъідөзөзБчЈ»өұ -up ОӘёЯКұЈ¬өзБчIref И«ІҝБч№э M2Ј¬ЙПАӯҫөПсөзВ·ҝмЛЩҪ«M4 В©¶ЛідөзЦБVDDЈ¬ЦВК№M6 №Ш¶ПЎЈИз№ыІ»УГЙПАӯҫөПсөзВ·Ј¬өұ M2 ҝШЦЖөзБчКұЈ¬M3 ЙПИФИ»»бУР¶МФЭөДөзБчНЁ№эЈ¬өзБчіЙЦёКэ№ШПөЛҘјхЈ¬ҙУ¶шТэЖрБЛVCO Па О»ФлЙщЎЈёГөзВ·Т»ёцН»іцөДУЕөгҫНКЗЈ¬ЗЙГоөДФЛУГБЛТ»ёцјтөҘөДХэ·ҙАЎ·ЕҙуЖчЈ¬ТФјУҝмҝӘ№Ш ЛЩ¶ИЎЈөұ M1 ҝШЦЖөзБчКұЈ¬ЛьАыУГөзБчФҙIref ¶ФҪЪөг A ідөзЈ¬УЙУЪФШБчЧУЧўИлЛЩ¶ИҝмЈ¬ M6 әЬҝмҫНҪШЦ№БЛЎЈИз№ыТ»ёцҝӘ№Ш MOS №ЬФЪұҘәНМ¬КұҪшИлҪШЦ№ЗшЈ¬ФтЛщУРөД№өөАөзәЙҪ«Бч ИлMOS №ЬөДФҙ¶ЛЈ¬В©¶ЛІ»КЬУ°Пм ,УРР§өШПыіэБЛөзәЙ№ІПнПЦПуЎЈ  Нј 4 ЛщКҫөДКЗНкХыөДөзәЙұГЈ¬»·В·ВЛІЁөзВ·Ј¬ФЪЙијЖКұЈ¬ёщҫЭPMOS әНNMOS өД№өөА ЗЁТЖВКПаУҰөчХыMOS №ЬҝніӨұИЈ¬К№PMOS №ЬәНNMOS №ЬСУКұПаН¬Ј¬Н¬КұЈ¬ФцҙуөзБчҫөMOS №ЬөДҝн¶ИЈ¬К№ід·ЕөзөзБчНкИ«ЖҘЕдЈ¬ПыіэБЛөзБчК§ЕдөДУ°ПмЎЈ  4 ЖдЛыДЈҝйЙијЖ 4.1 јшЖөјшПаЖч ұҫЙијЖІЙУГ TSPC Ҫб№№өД¶ҜМ¬ГЕҙҘ·ўЖчАҙКөПЦPDFЈ¬ИзНј5 ЛщКҫЈ¬Reset ·ҙАЎРЕәЕЦРНЁ №эФцјУ·ҙПаЖчСУКұЈ¬ПыіэБЛЛАЗшЈ¬өұКдИлF1 әНF2 өДЖөВКПаО»ұд»ҜКұЈ¬UPЈ¬DN ·ЦұрКдіц Ў°1ЎұәНЎ°0ЎұөДКэЧЦРЕәЕЈ¬ОӘҪУәуРшөДІо·ЦөзәЙұГөзВ·Ј¬»№УҰНЁ№э·ҙПаЖчөГөҪ-UPЈ¬-DN РЕ әЕЎЈ  4.2 С№ҝШХсөҙЖч ұҫЙијЖІЙУГБЛІо¶ҜКдИлЈ¬Иэј¶Б¬ҪУөД»·РОХсөҙЖчҪб№№Ј¬ГҝТ»ј¶өДСУіЩөҘФӘЙијЖІЙУГ¶ФіЖ ёәФШҪб№№Ј¬ТФФцҙуСУіЩөҘФӘёәФШөДПЯРФ·¶О§Ј¬ҪПЦ®өҘ¶ЛКдИлөДө№ПаЖчСУіЩөҘФӘЈ¬ХвЦЦҪб№№ҫЯ УРәЬәГөДТЦЦЖ№ІДЈРЕәЕөДДЬБҰЈ¬ҙУ¶шҝЙТФУРР§өШТЦЦЖөзФҙәНіДөЧФлЙщЎЈ  5 ·ВХжҪб№ы ФЪChartered 0.35um CMOS ұкЧј№ӨТХПВЈ¬ІЙУГCadence Spectre ·ВХжИнјю·Цұр¶Фҙ«НіРН өзәЙұГЛшПа»·өзВ·әНёДҪшРНөзәЙұГЛшПа»·өзВ·ҪшРРБЛ·ВХжЎЈҙУНј7(a)ҝЙТФҝҙіцЈ¬ҙ«НіРНөзәЙ ұГЛшПа»·ФЪПаО»Лш¶ЁөДЗйҝцПВЈ¬Vctl УЙУЪөзәЙ№ІПнәНөзБчК§Ед»бІъЙъ¶¶¶ҜЎЈёДҪшөзәЙұГөзВ· әуЈ¬ИзНј7(b)ЛщКҫЈ¬Лш¶ЁЗйҝцПВVctl »щұҫұЈіЦОИ¶ЁЈ¬ПыіэБЛ¶¶¶ҜПЦПуЈ»Нј8(a)ОӘҙ«НіөзәЙұГ өзВ·ЛшПа»·ФЪПаО»ҙУК§ЛшөҪЛш¶Ё№эіМЦРVctl ұд»ҜЈ¬ҝЙТФҝҙіцЈ¬Vctl КұЦУОЮ·ЁНкИ«Лш¶ЁЈ¬ФЪ Т»ёцЦРРДЦөёҪҪьХсөҙЈ»Нј8(b)ПФКҫЈ¬ёДҪшәуөДөзәЙұГЛшПа»·өДVctl өзС№ФЪТ»¶ОКұјдәуҝЙТФ ОИ¶ЁФЪДіёц№М¶ЁЦөЙПЈ¬Лш¶ЁКұјдОӘ11.12usЎЈ  6 ҪбВЫ ұҫОДМбіцБЛТ»ёцёДҪшРНpump-up Ҫб№№өДИ«Іо·ЦөзәЙұГөзВ·Ј¬ФЪChartered 0.35um CMOSұкЧј№ӨТХПВЈ¬НЁ№эCadence Spectre ·ВХжСйЦӨЈ¬УРР§ТЦЦЖБЛөзәЙ№ІПнЈ¬өзБчК§ЕдЈ¬ЛАЗшөИ·З АнПлМШРФөДУ°ПмЈ¬ФЪ2V-3.5V өзФҙөзС№ПВЈ¬ДЬОИ¶ЁКдіц13.56 MHz КұЦУРЕәЕЈ¬№ҰәДОӘ17.1 mWЈ¬ Лш¶ЁКұјдОӘ11.12 usЎЈ ұҫОДҙҙРВөгЈәІЙУГ pump-up Ҫб№№ЛшПа»·Ј¬НЁ№эјУТ»ёцХэ·ҙАЎ·ЕҙуЖчЈ¬јУҝмБЛөзәЙұГҝӘ ЖфЛЩ¶ИЈ»өзәЙұГҝӘ№Ш MOS №ЬФЪұҘәНМ¬КұҪшИлҪШЦ№ЗшЈ¬ЛщУРөД№өөАөзәЙҪ«БчИлMOS №ЬөДФҙ ¶ЛЈ¬В©¶ЛІ»КЬУ°ПмЈ¬УРР§өШПыіэБЛөзәЙ№ІПнПЦПуЎЈ |

НшУСЖАВЫ