PCI-ExpressЗЧЭИУїЧХдкжЧФмЯЕЭГжаЕФгІгУЩшМЦ

ЗЂВМЪБМфЃК2010-8-17 16:31

ЗЂВМепЃКlavida

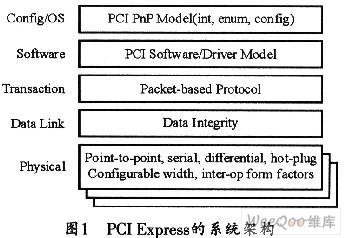

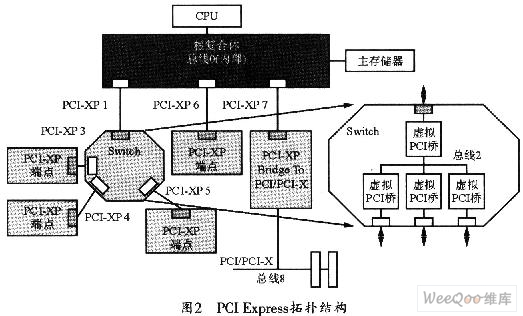

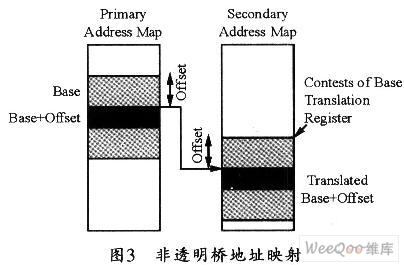

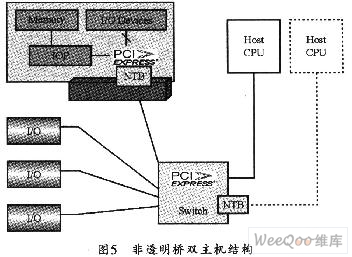

|

дкЯЕЭГЩшМЦжаЃЌЩшМЦЪІУЧУцСйЕФживЊЬєеНЪЧМШвЊжЇГжИпПЩППад(HAЃЌHigh Availability)ЃЌгжвЊЪЙЯЕЭГОЁПЩФмМђЕЅЁЂгааЇЁЃЖјPCI ExpressЁЂЛљгкPCI ExpressЕФИпМЖНЛЛЛМмЙЙ(Advanced switchingArchitecture)ЁЂЛљгкPCI ExpressЕФQOS(Quality-Of-Service)ЬиадвдМАPCI-ExpressЗЧЭИУїЧХЕФГіЯжЃЌЙВЭЌЮЊетбљЕФЯЕЭГЩшМЦЬсЙЉСЫвЛИіЗЧГЃгаЗЂеЙЧБСІЕФНтОіЗНАИЁЃ 1 PCI ExpressММЪѕМђНщ PCI ExpressММЪѕЪЧвЛИіБШНЯаТЕФЛЅСЌБъзМЁЃИУММЪѕЪЪгУгкИпадФмЕФаОЦЌЕНаОЦЌЁЂАхзгЕНАхзгЁЂБГАхКЭЛњЯфжЎМфЕФЛЅСЌЁЃЫќЪЧPCIБъзМЕФвЛИібнНјАцБОЃЌвђДЫЃЌдкШэМўНсЙЙЩЯШдБЃГжзХЖдPCIЕФМцШнадЁЃ PCI ExpressЪЧЛљгкВуДЮЛЏЕФЁЂИпЫйЕФДЎааЭЈаХММЪѕЁЃЦфавщеЛПЩЗжЮЊЮяРэВуЁЂЪ§ОнСДТЗВуКЭДЋЪфВуЁЃ ЦфжаЃЌЮяРэВуАќРЈЕЭЕчбЙВюЗжаХКХЕФИпЫйДЎааНгПкЁЂ8BЃЏ10BБрТывдМАACёюКЯВюЗжаХКХЁЃЭЈГЃАбвЛзщLVDSЫЋНЪЯпГЦЮЊвЛИіЭЈЕР(lane)ЃЌЖјЧвPCI ExpressдЪаэНЋЖрИіЭЈЕРКЯВЂГЩвЛИіИќДѓИќПэЕФЖЫПкЃЌШчx1ЃЌx2ЁжБЕНx32ЁЃЮяРэВуНгПкПЩжЇГжШШВхАЮ(hot-plugging)ЁЃ Ъ§ОнСДТЗВуПЩжЇГжгыСйНќPCI ExpressЪЕЬхНЛЛЛЪ§ОнАќЃЌЭЌЪБжЇГжЪ§ОнЭъећад(data integrity)КЭЫГађадМьВщЃЌвдМАЪ§ОнАќЕФШЗШЯКЭСїСППижЦЕФФмСІЁЃ PCI ExpressММЪѕЯЕЭГжаЕФДЋЪфВуПЩдкжїЛњКЭжеЖЫЩшБИМфДЋЫЭЖСЃЏаДЧыЧѓЃЌВЂПЩбЁдёадЕФЬсЙЉДЋЪфВуЕФЖЫЕНЖЫ(end-to-end)Ъ§ОнАќЕФЭъећадМьВщ(CRC-32)ЁЃ вЛжБвдРДЃЌPCI ExpressДЋЪфЯЕЭГжаЕФЮяРэВуЕФЫйЖШвЛжБдкВЛЖЯЕФЬсИпЃЌЕЋЪЧЃЌЗжВуНсЙЙЪЙЮяРэВуЕФБфЛЏВЛЛсгАЯьЕНЫќЕФЩЯВуЁЃШчPCI Express1ЃЎxБъзМЕФЪБжгЦЕТЪЪЧ1ЃЎ25 GHzЃЌ2ЃЎ0БъзМЕФдђЮЊ2ЃЎ5 GHzЃЌ3ЃЎ0БъзМЕФЪЧ4 GHzЁЃЭМ1ЫљЪОЪЧPCI Ex-pressавщеЛНсЙЙЁЃ  PCI ExpressЕФQOSПЩЭЈЙ§ЖЈвх8ИідЫЪфЕШМЖ(TC-Traffic Classes)ЁЂАЫИіащФтЭЈЕР(VC-VirtualChannel)ЁЂTCЕНVCЕФгГЩфвдМАVCЕФжйВУЛњжЦРДЪЕЯжЁЃ PCI-SIGзщжЏдђЖЈвхСЫДгPCI ExpressДЎааНгПкЕНPCIЃЏPCI-XЕФЧХНгЙцЗЖЁЃИУЙцЗЖПЩвдЪЙЕУЕБЧАЪЙгУPCIЃЏPCI-XЕФгІгУЯЕЭГФмЙЛЦНЛЌЕФзЊвЦЕНPCI ExpressЁЃЭМ2ЫљЪОЪЧвЛИіЕфаЭЕФPCI ExpressЯЕЭГЃЌЦфжаАќКЌгаИљИДКЯЬх(root complex)ЁЂPCIExpressНЛЛЛПЊЙи(switch)ЁЂЧХ(bridgeЃЌPCI Expressto PCI-XЃЌPCI Express to PCI)вдМАЖЫЕу(end-point)ЕШЩшБИЁЃ  2 PCI ExpressЗЧЭИУїЧХ гыPCIЃЏPCI-XвЛбљЃЌPCI ExpressБОЩэвВЪЧПЊЗЂЮЌЛЄвЛИівдЕЅвЛжїЛњЮЊжааФЕФЯЕЭГМмЙЙЃЌЕЋЪЧШЫУЧвЛжБЪЙгУЗЧЭИУїЧХАбЫћУЧгУдкЖржїЛњЕФЛЗОГжаЁЃ ЗЧЭИУїЧХЕФЙІФмКЭЭИУїЧХКмЯрЫЦЃЌЦфжївЊВюБ№жЛгавЛЕуЃЌМДдкЗЧЭИУїЧХЕФСНБпЖМгажЧФмЩшБИЛђДІРэЦїЃЌВЂЧвЫћУЧгЕгаЖРСЂЕФЕижЗПеМфЁЃЖјЧвЃЌЗЧЭИУїЧХвЛБпЕФжїЛњВЛФмПДЕНЧХСэвЛБпЕФЭъећЕижЗЛђIЃЏOПеМфЁЃУПИіДІРэЦїАбЗЧЭИУїЧХЕФСэвЛБпПДзівЛИіЖЫЕу(endpoint)ЃЌВЂАбЫќгГЩфЕНздМКЕФЕижЗПеМфЁЃ 2ЃЎ1 ЕижЗЗвы дкЗЧЭИУїЧХЛЗОГжаЃЌPCI ExpressЯЕЭГашвЊдкДгвЛИіФкДцЕижЗПеМфДЉдНЕНСэвЛИіЕижЗПеМфЪБНјааЕижЗЗвыЁЃУПвЛИіЗЧЭИУїЧХ(NTB)ЖЫПкЖМгаСНЬзЛљЕижЗМФДцЦї(BAR)ЃЌвЛЬзЪЧИјжїЩшБИЖЫгУЕФЃЌСэвЛЬзЪЧИјДгЩшБИЖЫгУЕФЁЃЛљЕижЗМФДцЦїПЩгУРДЖЈвхдкЗЧЭИУїЧХСэвЛЖЫЕФФкДцЕижЗПеМфЕФЕижЗЗвыДАПкЃЌВЂдЪаэетИіЗвыБЛгГЩфЕНБОЕиЕФФкДцЛђIЃЏOПеМфЁЃУПИіBARЖЈвхСЫвЛИіЩшжУМФДцЦї(setup register)ЃЌПЩгУРДЖЈвхДАПкЕФДѓаЁЁЂРраЭвдМАвЛИіЕижЗЗвыМФДцЦїЁЃгыЭИУїЧХЛљгкзмЯпКХзЊЗЂЫљгаCSRsВЛЭЌЃЌЗЧЭИУїЧХЩшБИжЛНгЪмеыЖдБОЩшБИЕФCSRЪТЮёЁЃЦфЕижЗЗвыММЪѕгажБНгЕижЗЗвыКЭВщБэЕижЗЗвыСНжжЁЃ дкжБНгЕижЗЗвыФЃЪНЯТЃЌЕижЗЗвыЕФЙ§ГЬЪЧЛљгкЪТЮёжеНсЕФBARЛљжЗМгЩЯвЛИіЦЋвЦСПЁЃBARsжаЕФЛљжЗЗвыМФДцЦїПЩБЛгУРДЩшжУетбљЕФЗвыЁЃЭМ3ЫљЪОИјГіСЫДгжїЩшБИЖЫЕижЗгГЩфЕНДгЩшБИЖЫЕижЗЕФЦЋвЦЙ§ГЬЁЃ  BARsдђгУвЛжжЬиБ№ЕФВщевБэРДЮЊТфдкЫќДАПкжаЕФЪТЮёНјааЕижЗЗвыЁЃвђЮЊЕижЗжаЕФЫїв§гђПЩЭЈЙ§БрГЬРДЕїНкДАПкДѓаЁЃЌвђДЫЃЌетжжЗНЗЈдкБОЕиЕижЗЕНжїЛњЕижЗЕФгГЩфжаОпгаИќИпЕФСщЛюадЁЃЭЈГЃЫїв§БЛгУРДЬсЙЉаТФкДцЕижЗЕФИпЮЛБШЬи(bits)ЁЃ 2ЃЎ2 ДІРэЦїМфЕФЭЈаХ ЗЧЭИУїЧХдЪаэЧХСНБпЕФжїЛњЭЈЙ§БуМуМФДцЦїЁЂУХСхМФДцЦїКЭаФЬјЯћЯЂРДНЛЛЛвЛаЉзДЬЌаХЯЂЁЃ БуМуМФДцЦїдкЗЧЭИУїЧХЕФСНЖЫЖМЪЧПЩЖСаДЕФЃЌЕЋЪЧЃЌБуМуМФДцЦїЕФЪ§СПдкОпЬхЕФЪЕЯжжаЪЧПЩвдВЛЭЌЕФЁЃЫћУЧПЩвдБЛЧХСНБпЕФЩшБИгУРДДЋЫЭвЛаЉзДЬЌаХЯЂЃЌвВПЩзїЮЊЭЈгУЕФПЩЖСПЩаДМФДцЦїЪЙгУЁЃ УХСхМФДцЦїБЛгУРДДгЗЧЭИУїЧХЕФвЛБпЯђСэвЛБпЗЂЫЭжаЖЯЁЃЗЧЭИУїЧХЕФСНБпвЛАуЖМгаШэМўПЩвдПижЦЕФжаЖЯЧыЧѓМФДцЦїКЭЯргІЕФжаЖЯЦСБЮМФДцЦїЁЃетаЉМФДцЦїдкЗЧЭИУїЧХЕФСНБпЖМЪЧПЩвдБЛЗУЮЪЕФЁЃ аФЬјЯћЯЂвЛАуРДзджїЩшБИЖЫЭљДгЩшБИЖЫЕФжїЛњЃЌПЩгУРДжИЪОЫќЛЙЛюзХЁЃДгЩшБИжїЛњПЩМрПижїЩшБИжїЛњЕФзДЬЌЃЌШчЙћЗЂЯжГіДэЃЌЫќОЭПЩвдВЩШЁвЛаЉБивЊЕФДыЪЉЁЃЭЈЙ§УХСхМФДцЦїПЩвдДЋЫЭаФЬјЯћЯЂЁЃЕБДгЩшБИжїЛњУЛгаЪеЕНвЛЖЈЪ§СПдЄЯШЙцЖЈКУЕФаФЬјЯћЯЂЪБЃЌОЭПЩвдШЯЮЊжїЩшБИЕФжїЛњГіДэСЫЁЃ 3 ЛљгкPCI ExpressЗЧЭИУїЧХЕФЖржїЛњЯЕЭГ 3ЃЎ1 жЧФмВхПЈ дкжЧФмПЈФЃЪНЯТЃЌжЧФмВхПЈЩЯЕФPCI ExpressЗЧЭИУїЧХПЩвдНЋIOPКЭHost CPUИєРыПЊРДЃЌЕЋШддЪаэетСНИіCPUЭЈЙ§вЛаЉЬиЪтЕФМФДцЦїНјааЭЈаХЁЃЭМ4ЫљЪОЪЧжЧФмВхПЈФЃЪНЯТЕФЗЧЭИУїЧХЕФЭЈаХНсЙЙЁЃ  3ЃЎ2 ЫЋжїЛњФЃЪН ЗЧЭИУїЧХвВПЩгУдкЫЋжїЛњ(Dual Host)ЁЂжїЛњЙЪеЯзЊвЦ(Host Failover)КЭИКдиЗжЕЃ(Load-shar-ing)ЕШгІгУжаЁЃЭМ5ЫљЪОЪЧНЋСНИіHost CPUБЛЗЧЭИУїЧХИєРыПЊЕФНсЙЙЪОвтЭМЁЃ  3ЃЎ3 ЖржїЛњФЃЪН дкЖржїЛњЯЕЭГжаЃЌУПвЛИіжїЛњЖМПЩвдЭЈЙ§ЗЧЭИУїЧХНгШыЕНЯЕЭГжЎжаЃЌВЂЧвПЩвдЗУЮЪЫљгаЕФЖЫЕуЁЃдкPCIЕФУЖОйЙ§ГЬжаЃЌУПИіЖЫЕуЖМвЊКЭФГИіЬиЖЈЕФCPUЙиСЊЃЌЕЋдке§ГЃЕФВйзїЙ§ГЬжаЃЌвРРЕгкЗЧЭИУїЧХЕФЕижЗЗвыФмСІЁЃЫљгаЕФCPUЖМПЩвдЗУЮЪЫљгаЕФЖЫЕуЁЃЭМ6ЫљЪОЪЧжїЛњЯЕЭГЕФЗЧЭИУїЧХНсЙЙЁЃ  4 НсЪјгя ЗЧЭИУїЧХММЪѕдкPCIЪБДњОЭвбБЛгІгУЁЃЯждкЃЌдкPCI ExpressЯЕЭГжавВгаРрЫЦЕФЪЕЯжЁЃЯраХдкВЛдЖЕФНЋРДЃЌДгМђЕЅЕФжЧФмВхПЈЕНИДдгЕФЁЂДјащФтЪфШыЪфГіММЪѕЕФЖржїЛњЯЕЭГЃЌШЫУЧЖМНЋПДЕНPCIExpressЗЧЭИУїЧХЕФЙуЗКгІгУЁЃ |

ЭјгбЦРТл