MT-ZigBee硬件平台的设计

发布时间:2010-8-17 13:26

发布者:lavida

|

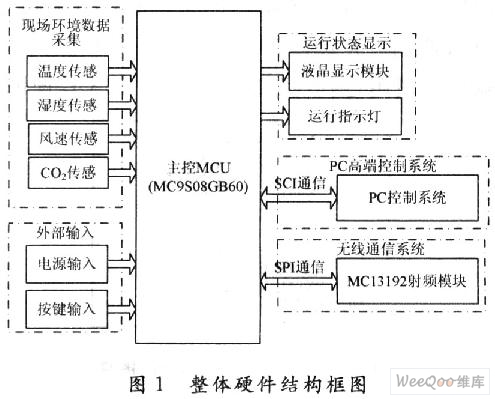

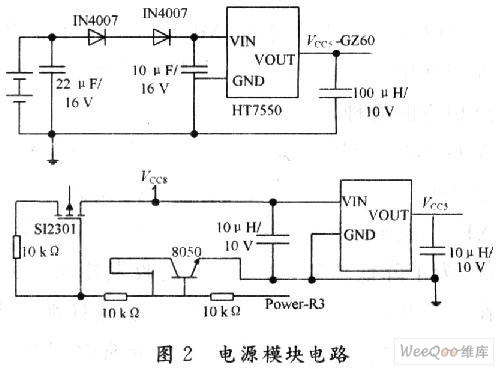

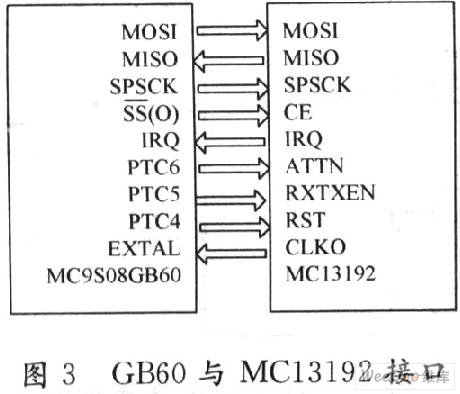

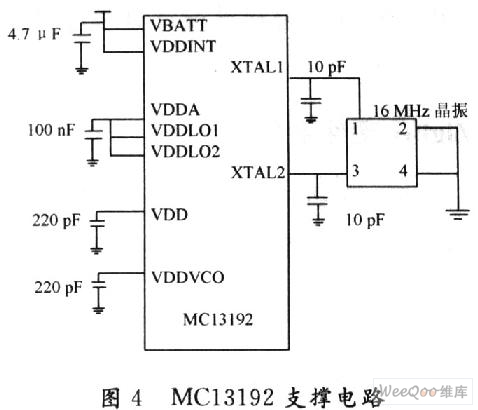

ZigBee技术是一种具有统一技术标准的短距离、低速率的无线通信技术,其物理层和媒体访问控制层协议为IEEE 802.15.4协议标准,网络层由ZigBee技术联盟制定,应用层的开发根据用户的实际应用需求,对其进行开发设计。 在设计开发ZigBee协议之前必须要有相应硬件平台的支撑,这里为ZigBee协议栈的实现提供了相应的硬件平台设计。在此主要介绍了MT-ZigBee硬件平台的设计与各硬件模块的测试。硬件平台的设计主要包括硬件平台的选型、ZigBee控制电路的硬件设计和ZigBee射频电路部分的硬件设计;硬件平台的测试主要包括各个硬件模块的测试。 1 ZigBee硬件方案 在ZigBee技术联盟中,Freescale,TI,Chipeon,Philips等公司都是ZigBee标准制订的先驱。在射频收发芯片方面,主要有Freeseale公司的MC13192,MC13193和Chipeon公司的CC2420,CC2430所提供的两大解决方案。下面简单比对这两种可选的硬件开发方案。 Freescale公司面向ZigBee技术推出了完整的硬件解决方案,其中主要包括MC13192,MC13193射频(Radio Frequenee,RF)收发芯片;与RF端相配套的低功耗HCS08核MCU;相关的传感器等。MC13192,MC13193是符合IEEE 802.15.4标准的射频数据调制解调器,它工作在2.4 GHz频段下,与MCU通过标准的4线SPI接口通信,采用16个射频通道,数据速率为250 Kb/s。与HCS08核MCU配套使用,可提供低成本、低功耗、经济高效的ZigBee硬件平台方案。挪威半导体公司Chipcon推出的CC2430射频芯片是全球首颗符合ZigBee技术标准的2.4 GHz射频芯片,它沿用了CC2420的架构。CC2430兼容IEEE802.15.4标准,具有8051核的无线单片机。其在单芯片上集成了ZigBee RF前端、存储器和微控制器。另外,CC2430内部还包含了模/数转换器(ADC)、定时器、AES-128协处理器、看门狗、32 kHz晶振时钟、上电复位电路、掉电检测电路以及21个可编程I/O接口。由于Freescale公司提供了详细的芯片手册、参考设计、布线设计等文档说明,为硬件平台的搭建提供了良好的开发环境。这里在现有的ZigBee硬件方案中选择了Freescale公司提供的解决方案:MC9S08GB60和MC13192;并以此方案为背景设计开发了MT-ZigBee硬件平台。 2 MT-ZigBee硬件平台设计 MT-ZigBee硬件平台的设计,主要包括硬件平台的选型,ZigBee控制电路的硬件设计和ZigBee射频电路部分的硬件设计。 2.1 硬件选型 (1)主控MCU的选取。从芯片内部集成功能模块、RAM和FLASH的存储容量、芯片和开发环境的熟悉程度等方面考虑,本文选择了Freescale公司生产的S08系列的8位MC9S08GB60(以下简称GB60)作为平台的主控芯片。HCS08核,最高总线频率可达40 MHz;它内部具有64 KB的FLASH和4 KB的RAM存储空间;内部集成了1个SPI模块,适合与MC13192的通信;2个SCI模块,方便与PC通信;具有背景调试模块.能利用单线对HCS08核的系列MCU进行方便地写入和调试,加快开发的速度并大大降低了调试的难度。 (2)物理层芯片的选取。为了设计出低成本、低功耗、经济高效的ZigBee硬件平台.这里选择了与HCS08核MCU配套使用的MC13192芯片作为Zig-Bee物理层芯片。MC13192是Freescale公司于2005年推出的工作在2.4 GHz频率下短距离,低功率,工业、科学和医疗(ISM)的无线数据收发器。MC13192与MCU的接口简单,只需四线的SPI,1个IRQ中断请求线和3个控制线。 2.2 MT-ZigBee硬件平台设计 MT-ZigBee硬件平台主要包括主控MCU支撑模块;外部输入部分有电源输入模块和按键输入;MC13192无线射频通信模块;SCI串行通信模块;运行状态显示模块和现场数据采集模块,整体的硬件框图如图1所示。其中按键输入、SCI串行通信模块、液晶及运行指示灯模块设计比较简单,由于篇幅问题,不再叙述。下面重点介绍电源输入模块、MCU支撑模块、GB60与MC13192接口电路和MC13192无线射频通信模块的硬件设计。  2.2.1 电源输入模块 无线传感器网络主要用于采集现场数据,再进行相应控制。设备均安放在采集现场,考虑到便于携带、安装,供电电源采用1节9 V的干电池。在硬件电路上电源分为两路:一路是单独供给主控芯片GB60的电源;另一路是供给LCD、MC13192、SCI、按键和测试小灯等所有外围模块的电源。具体电源电路如图2所示。  在电源电路中,主控芯片电源在任何情况下都是存在的.这样保证任何情况下GB60都是工作的;外围模块电源受到主控芯片控制,GB60通过MOS管来控制外围模块电源:当系统正常工作时,GB60允许外围模块电源上电;当系统进入低功耗状态时,GB60切断外围模块电源.这样整个系统只有主控芯片有供电,主控芯片再进入低功耗模式(Stop Mode),这样就更好地实现了整个系统的低功耗。注意,在切断外围模块电源时,不能直接使用一般的三极管,这样进入低功耗状态后外围模块仍然有较大的电流消耗,应该使用电流截止性能好的MOS管(如:SI2301)来实现。 2.2.2 GB60与MC13192接口电路设计 GB60与MC13192的接口电路如图3所示。GB60与MC13192主要有9个连接接口:4根SPI通信接口、IRQ中断接口、3根MC13192的控制口和MC13192时钟输出引脚。其中对于4线SPI,根据参考手册指出,当作为SPI主机方式,同时SPI状态与控制寄存器的模式错误标志(MODF)有效并置为1时,引脚可单独作为I/O口使用。在该设计中GB60为SPI主机方,直接作为输出口使用,用以控制MC13192的CE使能信号。  G1360对MC13192上的寄存器、片上RAM读取和写入时都是通过标准的4线SPI接口来实现的。通信时,MC13192只能作为从机,因此对于MCU而言,MOSI线是发送数据线,而MISO线是接收数据线,SPI的同步时钟由GB60在SPSCK管脚上给出,连接到MC13192的SPICLK上。 MC13192的IRQ管脚连接到GB60的IRQ管脚上,MC13192上产生的所有中断事件直接反映给GB60。当GB60接收到来自MC13192的外部中断时,还要查询其中断标志寄存器,来判断产生的中断事件,并作出相应的处理。 在GB60对MC13192的3个控制口中,ATTN管脚用于MCU、将MC13192从低功耗模式下唤醒,而RXTXEN管脚则用来使能MC13192的收发器。在通常情况,为了降低功耗,射频芯片的收发器都是关闭的,只有在发送和接收数据时才使能有效,这样能大大降低射频芯片的功耗。当射频芯片工作异常时,MCU也可以通过RST管脚来硬件复位MC13192。 MC13192的时钟输出引脚CLKO直接与GB60的EXTAL引脚相连接,从而GB60不再需要外部晶振电路的支持,直接采用来自MC13192的时钟源即可。该时钟源是可编程的,能够提供8种不同的时钟频率:16 MHz,8 MHz,4 MHz,2 MHz,1 MHz,62.5kHz,32.768 kHz和16.393 kHz。 2.2.3 MC13192无线射频通信模块设计 射频电路的设计是硬件设计中最为复杂的部分。这一部分对PCB的材质、电阻电容的精度、电路的走线等都有很高的要求,其参数选择的好坏直接影响到射频电路的质量。 射频电路的设计是参考Freescale,Microchip等公司给出的参考样例进行设计开发的。 (1)MC13192支撑电路的设计。MC13192的支撑电路包括电源电路,滤波电路和晶振电路,其逻辑连接如图4所示。VBATT和VDDINT是电源输入引脚,MC13192的正常工作电压为2.0~3.6 V,必须接一个4.7μF的稳压电容。VDDA,VDDL01和VDDL02为经过整流的模拟电压,必须旁接一个100 nF的滤波电容。VDD为经过内部整流的数字电压,旁接一个220 pF的滤波电容。VDDVCO为VCO电路供电,同样必须旁接一个220 pF的电容。XTAL1和XTAL2外接16 MHz的专用于2.4 GHz射频电路的晶振,其旁路电容为1O pF。  (2)天线电路的设计。用于2.4 GHz射频电路的天线有3种类型:外接直立天线、PCB天线和片式天线。外接直立天线的性能最好,但体积过大,只能用于对体积无要求的场合;片式天线采用集成电路来实现,性能一般,而且很难根据实际调整性能;PCB天线具有体积优势,但是对设计和PCB布线要求高,在无线传感器网络的硬件平台上应用最多。  图5为天线电路的原理图。RFIN-和RFIN+为接收通道,2个18 pF的电容过滤掉高频干扰信号,而0.5 pF的电容能防止共扼干扰。PAO-和PAO+为发送通道,这两个管脚和VDDA连在一起,给发送通道提供必要的能量。 3 MIT-ZigBee硬件平台的模块测试 在完成硬件电路设计后,必须对各模块的硬件电路进行测试,以保证硬件电路的可靠性。对于整块的硬件电路,应该按模块分别焊接、调试,并逐模块调试通过后再联合起来一起调试。在硬件PCB设计时需要预留出一定的测试节点,以便以后测量使用。 MT-ZigBee主要模块的基本测试流程如下: (1)电源模块测试。在空的PCB电路板上首先将电源模块的相关元器件焊接好,上电后直接利用万用表测量电源的输出点,看是否得到要求的电压值,以保证其他模块能正常工作。 (2)微控制器部分测试。当电源模块工作正常后,就需要测试GB60是否正常工作。对于MCU的测试主要就是通过BDM烧写器与GB60通信,看是否能进行正常的擦除与写入操作。若无法正常工作,则首先就应该仔细核对MCU支撑电路及电阻、电容的值是否正确,特别是晶振电路部分。GB60含有4 MHz的内部时钟源,且外围电路很少,所以比较容易调试通过。 (3)MC13192模块测试。对于MC13192射频模块的测试,主要是通过读写其内部的寄存器和缓冲区来进行测试的。 (4)其他外围模块测试。串行通信(SCI)是通过PC实现基本的收发;测试小灯模块,主要通过MCU将相应的I/O口置不同的值,看是否能点亮对应的小灯;测试液晶LCD模块,看是否在液晶上显示指定的字符。 4 结 语 这里主要为ZigBee协议栈的实现提供了相应的硬件平台设计。在MT-ZigBee平台硬件芯片选型的基础上,给出硬件平台的整体框架,阐述了硬件平台电源电路、GB60与MC13192接口电路和MC13192射频模块的详细设计。最后,还对MT-ZigBee硬件平台进行了各个模块的测试。由于篇幅有限,实现ZigBee技术相关的底层协议栈设计和具体验证协议栈可用性的应用实例在此中没有介绍。 |

网友评论