低相位噪声和宽调谐范围的5-GHz压控振荡器设计

发布时间:2010-8-17 13:20

发布者:lavida

|

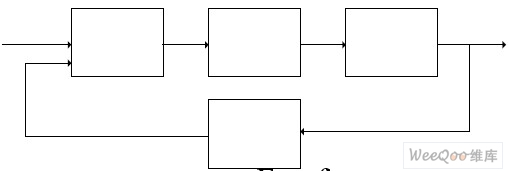

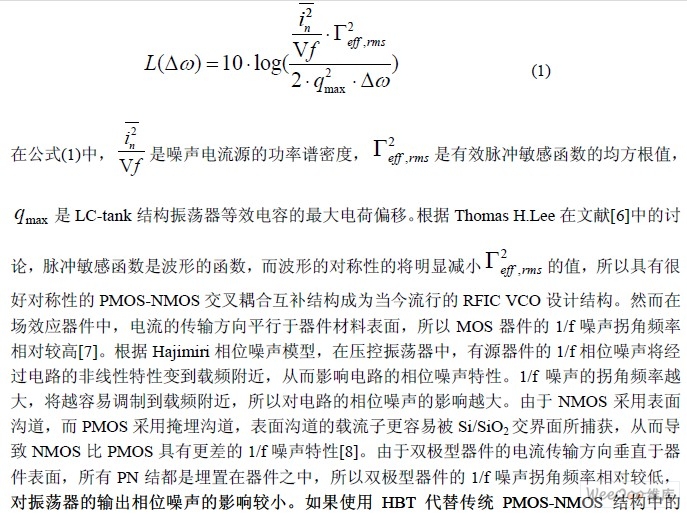

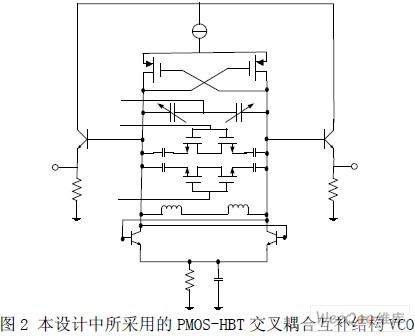

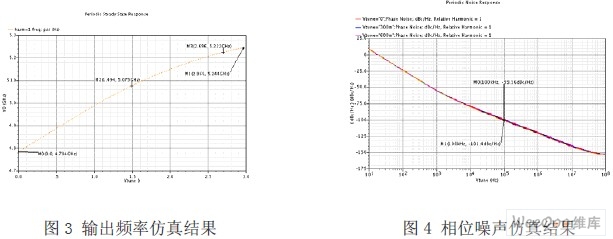

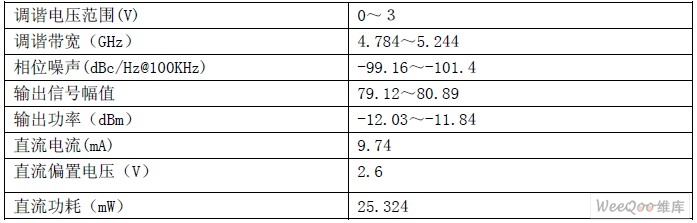

1 引言 虽然近年来通信技术得到了前所未有的发展,但是人们在通信技术不断发展的同时,对各个通信系统的性能要求也日益提高,以至于现存的通信系统仍然需要发展,需要科技工作者不断解决更加苛刻的技术难题。在众多技术难题中,如何实现高性能的单片全集成射频压 控振荡器仍然是最具挑战性的技术难题。 随着无线通信的不断发展,频率资源越来越成为稀缺而珍贵的资源。为了使得无线通信 系统能够充分地利用频率资源,并且能够在信号微弱以及临近信道信号干扰强的恶劣条件实 现高性能的通信,各种无线通信系统在射频前端普遍地采用频率合成器技术。 高性能的频率合成器通常采用锁相环技术实现。锁相环通用方框图如图1所示:  图1 基于锁相环的频综系统方框图 在上述频率合成系统中,反馈环路将使输出频频为参考频率的N/N+1 倍,如果这个参考频 率采用稳定的低频石英晶体振荡器实现,那么该频率合成器系统输出频率的稳定性将取决于 环路中压控振荡器的相位噪声特性。为了确保压控振荡器具有低的相位噪声,通常采用 LC-tank 结构构成高性能的压控振荡器。虽然在新的世纪里,对低相位噪声VCO 的研究 取得令人瞩目的成就,但是高性能单片集成的射频VCO 芯片的设计仍然是一项十分艰巨的 任务。本文将基于一种新的VCO 结构,采用有效的方法该降低该VCO 的相位噪声,从而得到 高性能的VCO。 2 VCO 电路的设计 根据众所周知的Lee 相位噪声模型,为了得到尽可能低的相位噪声,谐振电路的品 质因数必须尽可能的大。由于基于当前的工艺技术实现高品质因数的电感很困难,从而导致 基于当前的工艺技术实现高品质因数的谐振电路也很困难。所以,为了得到尽可能的低的相 位噪声,在给定工艺条件下,必须采用工艺允许的品质因数最高的电感来实现高品质因数的 谐振电路,同时,还必须考虑其它相位噪声降低技术。 根据Hajimiri 提出的线性时变相位噪声理论模型,由周期性准稳态噪声电流所引起 的相位噪声可以表示为:  NMOS 器件,将使得VCO 的性能得到显著的改善。采用该结构的VCO 便是PMOS-HBT 交叉耦合互补结构的VCO。由于降低1/f 噪声对相位噪声的影响,所以该结构能得到较好的 相位噪声特性。因此,本文将采用如图2 所示的PMOS-HBT 交叉耦合互补振荡器结构。  在上述结构中,变容二极管(G0,G1),开关对(NM0 和NM1,NM3 和NM4),电感(L0,L1) 以及有源器件的寄生电容,共同构成压控振荡器的谐振电路,而PMOS(PM0,PM1) HBT(Q0,Q1)交叉耦合互补结构产生负阻,为电路补充因谐振电路的损耗而消耗掉的能量, 从而维持电路持续振荡。为了实现电路的全集成,并能够得到尽可能高的品质因数,电感 (L0,L1)采用片上螺旋电感。因为电路要实现宽调谐范围,所以采用调谐范围比较宽,品质 因数很高的MOS 变容二极管作为调谐电容。开关对(NM0 和NM1,NM3 和NM4)通过控制位 (B0,B1)来控制开关的关和开,从而实现数字调谐,这样不仅能够展宽调谐范围,同时还能 够保证调谐增益具有相对较好的线性度。调谐增益的线性度越好,控制电压链路的噪声 对输出相位噪声的干扰也就越小。 3 验证结果 基于TSMC 0.35μm SiGe BiCMOS 工艺,并采用高性能电路仿真软件Cadence SpectreRF 实现设计。对电路进行设计时,首先设计谐振电路,考虑到有源器件的寄生电容效应,以及 工艺的偏差和温度补偿,所设计的谐振电路的谐振频率应该高于调谐带宽的最高频率。在设 计电路时,直流偏置电流应使该VCO 工作在流控区域,这样可以降低电路的输出相位噪声 。为了进一步降低相位噪声,PMOS 和HBT 的器件参数进行优化调整,使VCO 电路输 出信号保持良好的对称性。通过Cadence SpectreRF 仿真器仿真的输出频率结果如图3 所示。  在0 到3V 的调谐电压范围内,该VCO 电路的输出频率范围为4.78GHz 到5.244GHz, 调谐带宽为444MHz。在4.78GHz 到5.244GHz 的频率范围内对相位噪声的仿真结果如图 4 所示。在4.78GHz 到5.244GHz 的调谐范围内,在频偏100KHz 时,输出相位噪声的范 围为-99.16dBc/Hz 到-101.4dBc/Hz。该VCO 电路的性能总结如表1 所示。  4 总结 现代SiGe BiCMOS 工艺不仅提供了用于实现高集成度的CMOS 工艺,而且也提供了 噪声特性优异的HBT 工艺,使制作高兴能射频集成电路成为可能。本论文基于TSMC 0.35μm SiGe BiCMOS 工艺,采用PMOS-HBT 交叉耦合互补结构实现了调谐带宽为444MHz, 频偏100KHz 时,最好相位噪声-100dBc/Hz 的VCO。 本文创新点:当前流行的RFIC VCO 设计结构是PMOS-NMOS 交叉耦合互补结构,虽然该 结构具有较好相位噪声特性,但是NMOS 器件的闪烁噪声特性非常差,限制了相位噪声 进一步降低。本文充分利用BiCMOS 工艺的优势,采用PMOS-HBT 交叉耦合互补结构,同 时采用电容阵列调谐技术,在保证VCO 具有较低相位噪声的同时,尽可能的展宽调谐频 率的范围,实现地相位噪声和宽调谐范围的VCO 设计。 |

网友评论