基于SOPC的1553B总线接口逻辑设计

发布时间:2010-8-16 15:56

发布者:lavida

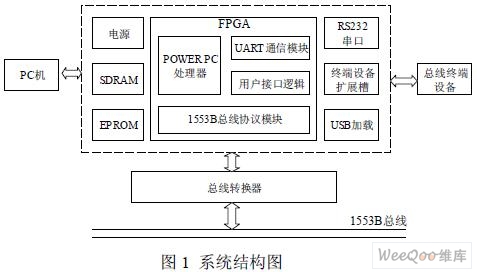

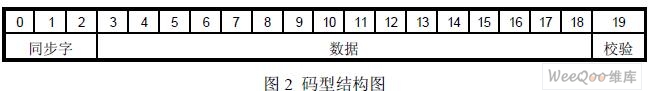

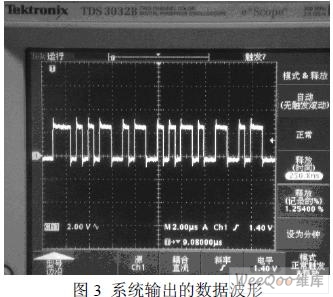

|

1 引言 数据总线是飞机航电系统中首先运用的数字电子设备之一,MIL-STD-1553B 就是其典型代表,它利用一条屏蔽的双绞线进行带有时钟信息的数据传输。1553B 具有高可靠性的特点,它已经成为我国航空航天领域广泛采用的军用总线标准。由于1553B 总线协议控制器基本依赖于进口的专用芯片,价格昂贵,还受到限制,并且这些芯片需要很多外围的硬件电路配合工作,如果完成整个总线接口板的设计,还需要单独的MCU,集成度不高,这样就在某种程度上限制了设计能力。随着嵌入式技术的发展,可编程片上系统设计(System on aProgrammable Chip,SOPC)技术已经在很多领域得到实际应用。本文采用SOPC 技术,以Xilinx 公司的Virtex-II Pro FPGA 为核心,实现1553B 总线传输协议的接口逻辑设计。 2 1553B 数据总线传输协议简介 现在广泛采用的 1553B 标准是根据1973 年军标1553 原版基础上发展而来的。1553B是一种集中控制式、飞机内部时分指令/响应型多路串行数据总线标准,具有高可靠性和灵活性,已经成为现代航空机载系统设备互联的关键技术,广泛应用于飞机、舰船等武器平台上。1553B 数据总线的传输速率为1Mbps,协议规定3 种字:命令字、数据字和状态字。字的长度为20 个bit,且由3 部分组成:同步头(3bit),消息块(16bit)和奇偶位(1bit)。信息量最大长度为32 个字。总线系统由一个总线控制器(BC)与不多于31 个的远程终端(RT)组成,有时系统中还可以加入总线.(MT),由于终端类型的不同,可辨别出命令字和状态字,命令字由BC 发出,而状态字则由RT 发出。总线上传输的信息格式主要有BC 到RT,RT到BC,RT 到RT,广播方式和系统控制方式。 3 系统结构及功能 系统采用 Xilinx 公司的Virtex-II Pro XC2VP30 FPGA 为核心,其内部带有2 个PowerPC405 处理器核。总线接口协议实现是基于Xilinx Virtex-II Pro 开发系统平台的,Virtex-II Pro开发平台是整个系统的核心,可以快速的搭建1553B 总线实现平台。系统的硬件平台主要由Virtex-II Pro 开发板、总线转换器、总线终端设备和PC 机构成,系统结构如图1 所示。  在系统的开发中,为了提高开发效率,同时系统主要验证的就是1553B 总线协议模块,因此可以充分利用Xilinx 公司的Virtex-II Pro 开发板。开发板上具有丰富的资源,主要包括:XC2VP30 芯片、SDRAM(可以扩展到2GB)、高速SelectMAP FPGA 配置PROM、RS232 串口、嵌入平台的USB 配置端口、高速系统扩展接口(与FPGA 的I/O 管脚相连)并可选择差分或单端模式、PS2 接口、AC97 音频接口、板上10/100M 以太网设备等等。这些丰富的板上资源为1553B 总线协议逻辑的开发提供了支持。 1553B 总线协议开发主要在FPGA 芯片中开发,因此FPGA 本身性能的好坏将影响系统的开发。XC2VP30 内部具有两个PowerPC 405 处理器核、13969 个Slices、分布式RAM 为428Kb、136 个乘法器单元、块RAM 为2448Kb、8 个DCM、8 个多吉比特收发器。由此可见,系统选用的FPGA 完全可以满足1553B 总线逻辑开发的需求。基于Xilinx 公司的Virtex-IIPro 开发板搭建起来的1553B 总线开发平台共分为4 个部分。其中各部分的功能说明如下:Virtex-II Pro 开发板:主要完成与PC 机通信功能,接收或向总线终端设备发送数据并将其转换成1553B 总线协议格式。 PC 机:系统通过PC 机对整个系统运行进行控制,如开始、运行、结束等命令都是通过PC 机由串口发送给开发板。 总线终端设备:采用单片机作为总线终端设备的核心,它与 FPGA 采用8 位并行数据总线进行数据传递。由总线终端设备向开发板发送数据,通过1553B 总线协议模块转换成协议格式,同时1553B 总线协议模块也可以接收来自总线的数据,并将其转换成总线终端设备可以接收的数据格式,总线终端设备通过判断发送数据与接收数据,可以确定 1553B 总线协议转换模块的有效性。 总线转换器:由于 1553B 总线上传输的是双极性的差分信号,因此,开发板在收发数据时首先要进行电平转换以及相应的调制解调,总线转换器就是完成这部分功能的。 4 1553B 总线接口逻辑的SOPC 设计 SOPC 的开发过程与传统的嵌入式系统设计不同,可以分为硬件开发和软件开发两个流程。Xilinx 公司的嵌入式开发工具EDK(Embeded Development Kit)SOPC 开发套件,可以进行Power PC 硬核嵌入式微处理器的开发工作,使用灵活方便,带有丰富的IP 资源,是目前性能比较优异的嵌入式微处理器开发工具,系统设计中使用的为EDK8.2 版本。应用EDK开发SOPC 系统过程中可以与ISE(Integrated Software Environment)软件配合使用,ISE 是Xilinx 公司FPGA/CPLD 的集成开发环境,该软件环境集成了FPGA 的整个开发过程所用到的工具。在本文1553B 总线接口逻辑的设计过程中,对于1553B 的编码、解码等核心模块,就是在ISE 环境下利用Verilog HDL 编写并调试通过,然后通过EDK 嵌入到系统当中的。 4.1 编码/解码模块 曼彻斯*编码/解码是1553B 总线接口重要的组成部分,曼彻斯*编解码模块设计的好坏直接影响总线接口的性能。系统编码模块完成的是曼彻斯*的编码及解码,并检测错误。它能够接收具有有效同步字头的曼彻斯*,并进行译码,以及识别其类型和串并转换、奇偶校验等;编码模块能将处理器输出的并行二进制数据进行曼彻斯*编码,再加上同步字头及奇偶位,从而满足符合1553B 标准的字进行输出。 曼彻斯*是一种广泛应用于航空电子综合系统中的总线数据传输的双极性码。它在每个码位中点存在一个跳变,1 信号是一个由1 到0 的负跳沿,而0 信号是由0 到1 的正跳沿。在MIL-STD-1553B 协议中其数据格式如图2 所示。  在系统的编码/解码模块设计中采用同步设计的方法,这样,所有的触发器都由一个公共时钟信号来同步。因此,可以很好的解决毛刺和一些竞争与冒险。 编码模块主要分为三个部分,分别为检测编码周期是否开始并产生同步字头、串并转换并产生奇偶校验位、对数据和奇偶校验位进行编码。下面给出了部分编码模块的源代码: always @(posedge enc_clk or negedge rst_n)//检测编码周期开始,根据字型确定同步头 begin if (!rst_n) sync_bits else if (tx_csw) sync_bits else if (tx_dw) sync_bits else sync_bits end 解码模块也可以分为三个部分,分别为同步字头检测、数据解码、串并转换与奇偶校验。 这个过程与编码模块是类似的。 4.2 消息处理模块 消息处理模块主要是接收来自 PC 机的命令,并且将运行结果上传到PC 机。为了能够快速完成系统的开发,采用EDK 自带的串口控制器IP Core。由于在Virtex-II Pro 开发板上面已经设计了与PC 机相连的RS232 串口,并且配有标准的DB-9 接口,因此只需要通过IPCore 16450-UART 控制器接收和发送数据即可实现系统与PC 机的消息处理功能。 4.3 PC 机和终端机程序设计 系统整个运行过程是,通过PC 机上的应用程序控制FPGA 是否开始工作,如果FPGA开始工作,则接收终端设备单片机发送来的并行数据,并根据用户逻辑对数据进行解析,并将数据送往编码模块,编码后的数据经过总线转换器送到1553B 总线上,通过测试仪器接收分析。同时,FPGA 也可以接收来自总线上的数据,在解码模块的作用下,完成同步字头检测、数据解码、串并转换以及奇偶校验等处理,然后根据用户逻辑对数据进行封装并送给终端设备,终端设备接收到数据进行存储,并连同原始发送数据一起通过FPGA 上传到PC机,以便对数据的正确性进行判断与验证。对于PC 机程序在VC6.0 环境下采用C++语言开发;终端设备单片机程序在Keil 编程环境,采用c51 语言开发。由于PC 机和单片机程序只是为了验证基于SOPC 开发的1553B 接口逻辑,不是本文论述重点,这里不过多赘述。 5 测试结果及结论 本文采用基于 SOPC 的设计方法,完成了MIL-STD-1553B .接口逻辑的开发,并且通过仪器对系统进行了测试。图3 是通过Tektronix 公司的TDS3032B 型示波器测得的系统输出的数据波形。测试结果表明,系统能够正确的接收和发送符合1553B 总线接口协议的数据,工作稳定可靠。  本文作者创新点:将 SOPC 技术应用于1553B 总线接口逻辑的开发中,使系统设计简单,配置更灵活,易于扩展,从而摆脱了1553B 总线控制器依赖于国外进口芯片的束缚,具有良好的军事和经济效益。初步预测项目经济效益约为300 万元。 |

网友评论