ЛљгкNios IIЕФЪ§зжвєЦЕТМЗХЯЕЭГЕФЩшМЦ

ЗЂВМЪБМфЃК2010-8-16 11:48

ЗЂВМепЃКlavida

|

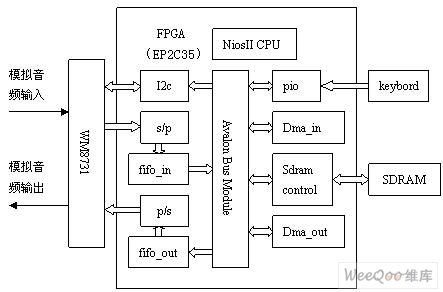

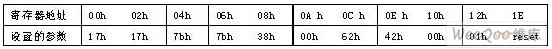

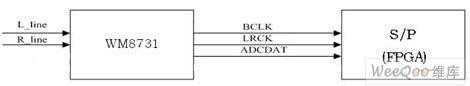

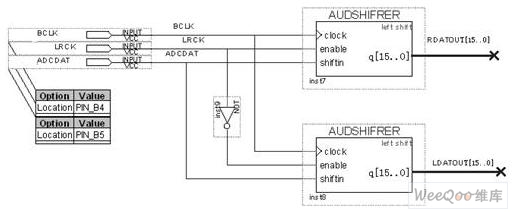

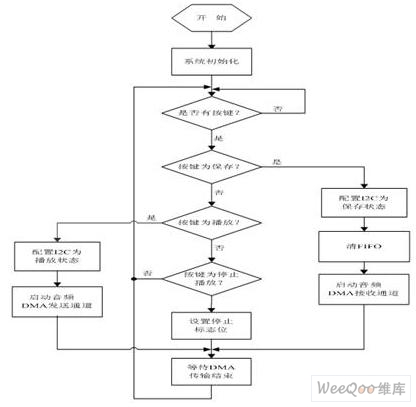

ЧАбд SOPC( System On Programmable Chip)ММЪѕЪЧSOC( System On Chip)ММЪѕКЭЕчзгЩшМЦздЖЏЛЏЃЈEDAЃЉММЪѕНсКЯЕФВњЮяЁЃЫќПЩвдНЋДІРэЦїЁЂДцДЂЦїЁЂI/OНгПкЁЂгВМўаДІРэЦїКЭЦеЭЈЕФгУЛЇТпМЕШЯЕЭГЩшМЦашвЊЕФЙІФмФЃПщЖММЏГЩЕНвЛИіFPGA аОЦЌРя, ЙЙНЈвЛИіПЩБрГЬЕФЦЌЩЯЯЕЭГ[1]ЁЃЫќЛЙОпгаСщЛюЕФЩшМЦЗНЪНЃЌПЩВУМѕЁЂПЩРЉГфЁЂПЩЩ§МЖЃЌОпБИЯЕЭГПЩБрГЬЕШЙІФмЃЌЪЧвЛжжгХауЕФЧЖШыЪНЯЕЭГЩшМЦММЪѕ[2]ЁЃБОЮФбаОПСЫвЛжжЛљгкSOPCММЪѕЕФЧЖШыЪНЪ§зжвєЦЕТМЗХЯЕЭГЕФЩшМЦЗНАИЁЃЯЕЭГЭЈЙ§дкFPGAаОЦЌЩЯХфжУNiosIIШэКЫДІРэЦїКЭЯрЙиЕФНгПкФЃПщРДЪЕЯжЧЖШыЪНЯЕЭГЕФжївЊгВМўНсЙЙ,ВЂНсКЯЧЖШыЪНЯЕЭГЫљжЇГжЕФШэМўЩшМЦРДПижЦвєЦЕБр/НтТыаОЦЌWM8731КЭSDRAM,ЪЕЯжСЫвєЦЕаХКХЕФA/DЁЂD/AзЊЛЛЁЂДцДЂЁЂЛиЗХЕШЙІФмЁЃгЩгкВЩгУСЫSOPCКЭDMAПижЦММЪѕЃЌИУЯЕЭГОпгаЩшМЦСщЛюЁЂРЉеЙадКУКЭЪ§ОнДІРэЫйЖШПьЕШгХЕу[3ЁЂ4]ЁЃ 1 ЯЕЭГдРэКЭНсЙЙ ЯЕЭГНсЙЙШчЭМ1ЫљЪОЁЃБОЯЕЭГбЁгУЕФFPGAаОЦЌЪЧAlteraЙЋЫОзюаТЭЦГіЕФCycloneII ЯЕСаЕФEP2C35ЁЃИУаОЦЌОпга35000ИіТпМЕЅдЊЁЂ672Иів§НХЁЂ475ИігУЛЇздЖЈвхI/OНгПкЁЂ35ИіЧЖШыЪНГЫЗЈЦїКЭ4ИіЫјЯрЛЗЃЌЪЧвЛИіМЏГЩЖШМЋИпКЭЙІФмЧПДѓЕФFPGAаОЦЌЁЃдкFPGAжаЩшМЦгаNiosIIШэКЫДІРэЦїКЭЙвдкИУNiosIIЯЕЭГЕФAvalonзмЯпЩЯЕФI2CХфжУНгПкФЃПщЁЂДЎ/ВЂзЊЛЛФЃПщ(S/P)ЁЂВЂ/ДЎзЊЛЛФЃПщ(P/S)ЁЂЯШШыЯШГіДцДЂЦїФЃПщЃЈfifo_inЁЂfifo_outЃЉЁЂSdramДцДЂЦїПижЦНгПкЃЈSdram controlЃЉЁЂDMAПижЦЦїНгПкЃЈDma_inЁЂDma_outЃЉКЭгУгкНгЪеАДМќаХЯЂЕФЭЈгУВЂааНгПкЃЈpioЃЉФЃПщЕШЁЃдкFPGAЭтгавєЦЕБр/НтТыаОЦЌЃЈWM8731ЃЉЁЂвєЦЕЪ§ОнДцДЂФЃПщЃЈSDRAMЃЉКЭПижЦАДМќЃЈkeybordЃЉЕШЁЃ  ЭМ1 ЯЕЭГНсЙЙЭМ ЯЕЭГЕФвєЦЕаХКХВЩМЏдРэЪЧЃКWM8731ОЙ§I2CХфжУКѓЃЌНЋЪфШыЖЫМгШыЕФФЃФтвєЦЕаХКХНјааA/DзЊЛЛКѓЃЌГЩЮЊДЎааЕФЪ§зжаХКХЁЃFPGAФкЕФДЎ/ВЂзЊЛЛФЃПщдйНЋИУаХКХзЊЛЛГЩ16ЮЛПэЕФВЂааЪ§зжаХКХЁЃДЫаХКХДгs/pЕФЪфГіЃЌВЂНЛИјЯШШыЯШГіДцДЂЦїЃЈfifoЃЉНјааЛКДцЁЃЕБfifoЕФЪ§ОнДяЕНЦфШнСПЕФвЛАыЪБЯђdma_inЧыЧѓвЛДЮDMAДЋЫЭЁЃDma_inНгЪмЧыЧѓКѓОЭжДаавЛДЮfifoЕНSdramжЎМфЕФжБНгDMAЪ§ОнБЃДцЁЃЖрДЮжиИДfifoЕНSdramжЎМфЕФDMAДЋЫЭЃЌжБЕНВЩМЏЭЃжЙМќБЛАДЯТКѓЃЌОЭЭъГЩСЫвЛЖЮвєЦЕЪ§ОнЕФВЩМЏЁЃ ЛиЗХдРэЪЧЃКдкDma_outЕФПижЦЯТЃЌЭЈЙ§SdramПижЦЦїНЋSdramжаБЃДцЕФвєЦЕЪ§ОнОfifo_outЫЭЕНВЂ/ДЎзЊЛЛФЃПщЕФЪфШыЖЫЃЌОЙ§ВЂ/ДЎзЊЛЛКѓЕФДЎааЪ§зжаХКХдйгЩWM8731НјааЪ§/ФЃзЊЛЛЃЌОЭЛЙдГЩЮЊФЃФтЕФЩљвєаХКХЁЃЖрДЮжиИДетжжDMAДЋЫЭВйзїЃЌжБЕНЛиЗХЭЃжЙМќБЛАДЯТКѓОЭЭъГЩСЫвЛЖЮвєЦЕЪ§ОнЕФЛиЗХЁЃ 2 ЯЕЭГгВМўЩшМЦ ЯЕЭГЕФгВМўжївЊгЩFPGAФкЕФNIOSIIжабыДІРэЦїМАНгПкФЃПщКЭFPGAЭтЕФвєЦЕБр/НтТыаОЦЌWM8731ЁЂДцДЂЦїКЭПижЦМќЕШВПЗжЙЙГЩЁЃ дкЯЕЭГЕФгВМўЩшМЦжаЃЌFPGAФкВПИїФЃПщЕФЩшМЦЪЧБОЯЕЭГгВМўЩшМЦЕФКЫаФММЪѕЁЃFPGAФкВПИїФЃПщЪЧРћгУAlteraЙЋЫОЬсЙЉЕФQuartusIIПЊЗЂШэМўКЭЦфжаМЏГЩЕФSOPC BuilderЯЕЭГПЊЗЂЙЄОпРДЩшМЦЕФЁЃSOPC BuilderжЇГжNiosII CPUЕФХфжУЃЌВЂжЇГжЩшМЦепдкИУЙЄОпЫљЬсЙЉЕФIPПтжаИљОнЯЕЭГЩшМЦашвЊбЁдёЯргІЕФНгПкФЃПщЃЌВЂМгШыЕНNiosIIЯЕЭГжаЁЃетбљЃЌдкМЋЖЬЕФЪБМфФкОЭПЩвдЭъГЩвЛИіSOPCЯЕЭГЕФЩшМЦЁЃНЋетаЉЩшМЦдкQuartusIIжаБрвыВЂЩњГЩsofИёЪНЮФМўКѓЃЌЯТдиЕНFPGAаОЦЌжаОЭаЮГЩСЫSOPCЕФЧЖШыЪНЯЕЭГгВМўЦНЬЈЁЃ ЯТУцжївЊЖдNIOSIIШэКЫДІРэЦїЁЂI2CзмЯпПижЦНгПкЁЂДЎ/ВЂзЊЛЛФЃПщЕШМИИіЙиМќФЃПщЕФЩшМЦНјааНщЩмЁЃ 2.1 NiosIIШэКЫДІРэЦї БОЯЕЭГЩшМЦЫљбЁдёЕФДІРэЦїЪЧAlteraЙЋЫОаТНќЭЦГіЕФЕкЖўДњЧЖШыЪНNiosIIШэКЫДІРэЦїЯЕСажаЕФвЛИіЁЃNiosIIДІРэЦїЯЕСаЪЧвЛИігУЛЇПЩХфжУЕФЭЈгУ32ЮЛRISCЧЖШыЪНШэКЫДІРэЦїМЏКЯЁЃЫќАќРЈШ§жжШэКЫCPUЃКвЛжжЪЧИпадФмШэКЫЃЌЫќЕФДІРэФмСІГЌЙ§200MIPSЃЌашвЊеМгУ1800ИіТпМЕЅдЊЃЛвЛжжЪЧОЋМђШэКЫЃЌ гУетжжШэКЫЙЙдьвЛИіЭъећЕФCPUЯЕЭГжЛашвЊеМгУ700ИіТпМЕЅдЊЃЛЕкШ§жжЪЧБъзМШэКЫЃЌетжжШэКЫдМеМгУ1400ИіТпМЕЅдЊЃЌадФмвВНщгкЩЯСНжжШэКЫжЎМфЁЃЫљгаШэКЫЖМЪЧ100%ДњТыМцШнЃЌЩшМЦепПЩИљОнашвЊЖдЩЯЪіШ§жжШэКЫНјаабЁдёРДЕїећЧЖШыЪНЯЕЭГЕФадФмМАГЩБОЁЃгЩгкБОЩшМЦВЩгУЕФCycloneIIЯЕСаЕФ2C35аОЦЌОпга35000ИіТпМЕЅдЊЃЌТпМзЪдДЪЎЗжЗсИЛЃЌМгЩЯЯЕЭГЖдCPUЕФадФмвЊЧѓНЯИпЕФдвђЃЌвђДЫбЁгУСЫИпадФмЕФNiosIIШэКЫзїЮЊБОЯЕЭГЕФCPUЁЃ 2.2 I2CзмЯпПижЦНгПк WM8731ЪЧWolfson MicroelectronicsЙЋЫОЩњВњЕФвЛПюЕЭЙІКФЕФИпЦЗжЪЫЋЩљЕРЪ§зжаХКХБрНтТыаОЦЌЁЃИУаОЦЌЕФADCКЭDACЕФВЩбљЦЕТЪЮЊ8KHZ"96KHZПЩЕїЃЌПЩзЊЛЛЕФЪ§ОнЮЛГЄЖШЮЊ16"32ЮЛПЩЕїЁЃWM8731ЕФФкВПга11ИіМФДцЦїЁЃИУаОЦЌЕФГѕЪМЛЏКЭФкВПЙІФмЩшжУЪЧвдI2CзмЯпЗНЪНЖдЦфФкВПЕФет11ИіМФДцЦїНјааЯргІЕФХфжУРДЪЕЯжЕФЁЃБОЩшМЦжаWM8731ЙЄзїгкжїФЃЪНЃЌВЩбљЦЕТЪЩшЮЊ48KHZЃЌзЊЛЛЕФЪ§ОнЮЛГЄЖШЮЊ16ЮЛЁЃ гЩгкSOPC BuilderздДјЕФIPПтжаВЂВЛАќКЌI2CХфжУНгПкФЃПщЃЌЫљвдИУФЃПщашвЊЩшМЦепИљОнвЊХфжЦЕФаОЦЌЕФМФДцЦїЬиЕуКЭЙІФмвЊЧѓНјаазЈУХЕФЩшМЦЁЃБОЯЕЭГЕФI2CНгПкЪЧзїепздааЩшМЦЃЌВЂвдIPКЫЕФаЮЪНЭЈЙ§SOPC BuilderСЌНгЕНЯЕЭГЕФAvalonзмЯпЩЯЕФЁЃWM8731ЕФЛљЕижЗЪЧ34h ,11ИіМФДцЦїЕФХфжУЪ§ОнШчБэ1ЫљЪОЁЃЦфжа1EhЮЊWM8731ЕФШэМўИДЮЛПижЦМФДцЦїЃЌИДЮЛЪБХфжУЕФжЕЮЊ00h,ЦНЪБЮЊШБЪЁжЕЁЃ Бэ1 WM8731ЕФМФДцЦїМАЦфВЮЪ§ЩшжУ  2.3 ДЎ/ВЂзЊЛЛФЃПщ гЩгкWM8731дкA/DзЊЛЛКѓКЭD/AзЊЛЛЧАЕФЪ§зжаХКХЖМЪЧвдДЎааИёЪНгыЭтНчНјааЪ§ОнНЛЛЛЕФЃЌЫљвдЃЌдкWM8731гыЯЕЭГПижЦКЫаФжЎМфашвЊМгШыДЎ/ВЂКЭВЂ/ДЎзЊЛЛФЃПщЁЃБОЮФжївЊЖдЦфжаЕФДЎ/ВЂзЊЛЛФЃПщЕФЩшМЦдРэНјааНщЩмЁЃЙЄзїгкжїФЃЪНЕФWM8731гыДЎ/ВЂзЊЛЛФЃПщЕФСЌНгШч2ЫљЪОЁЃЭМжаЃЌBCLKЁЂКЭLRCKЮЊWM8731ЗЕЛиИјПижЦФЃПщЕФЮЛЭЌВНЪБжгКЭВЩбљЪБжгЃЌADCDATAЮЊWM8731ЪфГіЕФДЎаавєЦЕЪ§ОнСїЁЃ  ЭМ2 жїФЃЪНЕФWM8731гыДЎ/ВЂзЊЛЛФЃПщЕФСЌНгЭМ БОЩшМЦжаЃЌДЎВЂзЊЛЛФЃПщгЩСНИі16ЮЛЕФвЦЮЛМФДцЦїЙЙГЩЃЌЗжБ№ЖдзѓЩљЕРКЭгвЩљЕРЕФЮЛЪ§ОнСїНјааДЎ/ВЂзЊЛЛЃЌЕчТЗЙЙГЩШчЭМ3ЫљЪОЁЃСНИівЦЮЛМФДцЦїinst7КЭinst8гЩLRCKКЭLRCKЕФЗЧаХКХЪЙФмЃЌЕБLRCKЮЊЕЭЕчЦНЪБЃЌвЦЮЛМФДцЦїinst8ЙЄзїЃЌЖдзѓЩљЕРЕФЪ§ОнСїНјааДЎВЂзЊЛЛЃЌЕБLRCKЮЊИпЕчЦНЪБЃЌвЦЮЛМФДцЦїinst7ЙЄзїЃЌЖдгвЩљЕРЕФЪ§ОнСїНјааДЎВЂзЊЛЛЁЃ  ЭМ3 вЦЮЛМФДцЦїЕчТЗЭМ 3 ЯЕЭГШэМўЩшМЦ БОЯЕЭГЕФШэМўЪЧдкAlteraЙЋЫОЬсЙЉЕФШэМўМЏГЩПЊЗЂЙЄОпIDEжаЃЌвдCгябдаЮЪНЃЌдкгВМўГщЯѓВу(HAL)КЏЪ§жЇГжЯТЩшМЦЕФЁЃЯЕЭГЕФШэМўСїГЬЭМШчЭМ4ЫљЪОЁЃЯЕЭГЦєЖЏКѓЃЌЯШНјааГѕЪМЛЏВйзїЃЌГѕЪМЛЏГЬађжївЊЭъГЩWM8731ЕФМФДцЦїХфжУЁЂГѕЪМЛЏDMAЭЈЕРМАЧхВЩМЏFIFOЛКГхЦїЁЃЫцКѓЃЌЯЕЭГНјШыжїбЛЗзДЬЌЃЌВЂМьВтАДМќЁЃЕБМьВтЕНSAVEАДМќЪБЃЌЯЕЭГЯШЭЈЙ§I2CХфжУWM8731ЮЊТМжЦЪБашвЊЕФзДЬЌЃЌШЛКѓЧхFIFOЛКГхЦїЃЌЫцКѓЦєЖЏDMAНгЪеЭЈЕРЃЌПЊЪМБЃДцЪ§ОнЃЌжБЕНвЛДЮDMAДЋЪфНсЪјЁЃЕБМьВтЕНВЅЗХАДМќБЛАДЯТЪБЃЌЯЕЭГЭЈЙ§I2CХфжУWM8731ЮЊВЅЗХЪБЫљашвЊЕФзДЬЌЃЌВЂНјШыВЅЗХГЬађЁЃЕБЯЕЭГМьВтЕНЭЃжЙАДМќБЛАДЯТЪБЃЌЩшжУВЅЗХБъжОЮЛЮЊSTOPЃЌВЂдквЛДЮDMAЭъГЩКѓЃЌздЖЏЭЃжЙВЅЗХЁЃ  ЭМ4 ЯЕЭГШэМўСїГЬЭМ 4 НсЪјгя БОЩшМЦдкAlteraЙЋЫОзюаТЭЦГіЕФCycloneIIЯЕСаЕФEP2C35аОЦЌЩЯНјааСЫШэЁЂгВМўЕїЪдЃЌЙІФмШЋВПе§ГЃЁЃгЩгкЯЕЭГЩшМЦжаВЩгУСЫDMAПижЦЯТЕФFIFOКЭSDRAMжЎМфЕФжБНгИпЫйЪ§ОнДЋЪфММЪѕЃЌгааЇЕиНтОіСЫвєЦЕаХКХЕФИпЫйA/DЁЂD/AзЊЛЛМАДІРэЙ§ГЬжаЖдCPUзЪдДГЄЪБМфеМгУКЭЯЕЭГЙІФмРЉеЙЪБЖдPCUзЪдДИќЖрашЧѓЕФУЌЖмЃЌЪЙЕУБОЩшМЦдкЯЕЭГЙІФмРЉеЙЩЯОпгаМЋДѓЕФЧБСІЁЃдйМгЩЯSOPCММЪѕдкШэЁЂгВМўЩшМЦЩЯЕФПЩВУМѕКЭКмЗНБувЦжВЕШгХЕуЃЌБОЩшМЦПЩвдзїЮЊвЛИізгЯЕЭГгІгУдкИќДѓаЭЕФЯЕЭГЩшМЦжаЃЌР§ШчЧЖШыЪНЭјТчвєЁЂЪгЦЕаХКХДІРэЕШЃЌгаКмКУЕФгІгУЧАОАКЭПЦбаМлжЕЁЃ |

ЭјгбЦРТл