ЛљгкFPGAЕФКьЭтЭМЯёДцДЂгыЛиЗХЯЕЭГЩшМЦ

ЗЂВМЪБМфЃК2010-8-16 11:48

ЗЂВМепЃКlavida

|

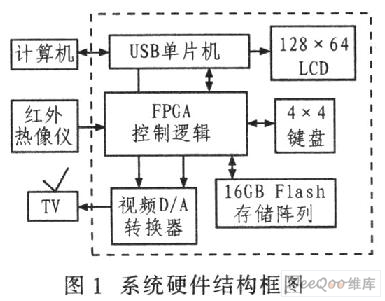

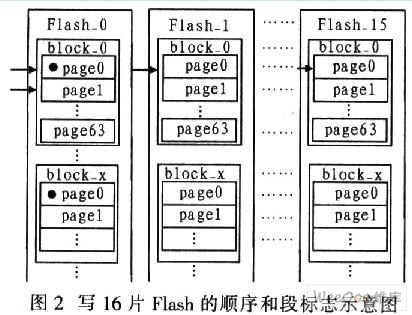

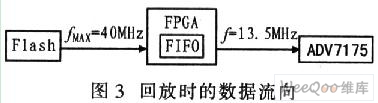

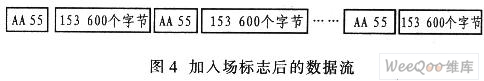

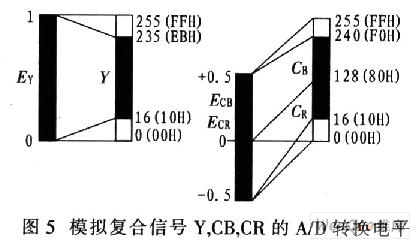

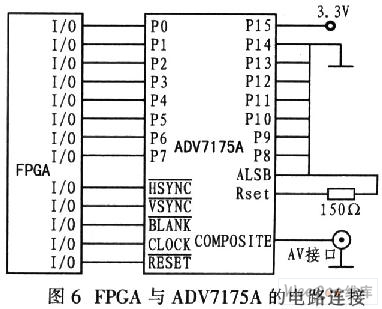

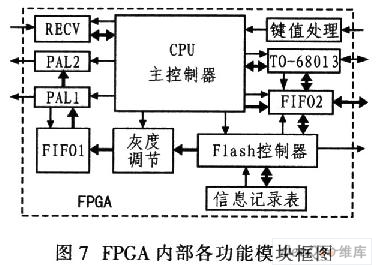

1 в§бд ФПЧАЃЌКьЭтШШЯёвЧгІгУЙуЗКЃЌЖргУгкеьВщЛђМрПиЃЌВЂЧвДѓВПЗжКьЭтШШЯёвЧВЂУЛгаХфБИДѓШнСПДцДЂЦїЃЌЕЋдквЛаЉЬиЪтГЁКЯШчЕМЕЏЗЂЩфЪдбщжаЕФИњзйЕМЕЏЕФЗЩааЙьМЃЃЌашвЊМЧТМећИіЙ§ГЬЃЌвдБИЪТКѓЗжЮіЁЃвђДЫЃЌЛљгкЯЕЭГЩшМЦЬхЛ§КЭЙІКФПМТЧЃЌетРяЬсГівЛИіЛљгкFPGAЕФЪгЦЕЭМЯёДцДЂгыЛиЗХЯЕЭГЩшМЦЗНАИЁЃИУЯЕЭГВЩгУ16ЦЌ1 GB NAND FlashЃЌКьЭтШШЯёвЧЪфГіЕФУПГЁ320x240ИіЯёЫиЕуЃЌГЁЦЕ50 HzЃЌ16 bitЕФВЛбЙЫѕЪ§зжЪгЦЕЭМЯёВЂБЃГжжСЩй30 minЁЃЮЊСЫРЉеЙЪ§ОнДцДЂСПЃЌИУЯЕЭГЛЙХфБИUSBЭЈаХНгПкЃЌБугкНЋМЧТМЪ§ОнЩЯДЋжСМЦЫуЛњЃЌЛђНЋМЦЫуЛњБЃДцЪ§ОнЯТдиЕНИУЯЕЭГВЅЗХЁЃ 2 ЯЕЭГгВМўЩшМЦ ЯЕЭГгВМўНсЙЙПђЭМШчЭМ1ЫљЪОЃЌFPGAНЋНгЪеЕФЪгЦЕЪ§ОнБржЁКѓЫЭжСFlashНјааДцДЂЃЌВЅЗХЪБЖСШЁЪ§ОнВЂАДЬиЖЈЪБађЫЭжСЪгЦЕDЃЏAзЊЛЛЦїЃЌдйОD/AзЊЛЛКѓЫЭжСЕчЪгЛњЁЃUSBЕЅЦЌЛњГ§гыМЦЫуЛњДЋЪфЪ§ОнЭтЃЌЛЙПЩЭЈЙ§I2CзмЯпХфжУЪгЦЕDЃЏAзЊЛЛЦїЕФМФДцЦївдМАЯдЪОПижЦLCDФЃПщЁЃ  ПМТЧЕНИУЯЕЭГFPGAЕФФкВПИїФЃПщТпМИДдгЃЌгШЦфЪЧдкЪгЦЕЛиЗХЪБашвЊЖржжПижЦЗНЪНЃЌШчднЭЃЁЂПьНјПьЭЫЁЂТ§ЗХТ§ЭЫЁЂж№ГЁВЅЗХЛиЗХЕШЃЌЪЕЯжетаЉПижЦашеМгУНЯЖрЕФТпМзЪдДЃЌвђДЫЃЌFPGAбЁгУXilinxЙЋЫОЕФSpartan-IIEЯЕСаЕФXC2S-150E-6P0208ЃЌИУЦїМўФкВПТпМИпДя15ЭђУХЃЌОпга48 KbitЕФBlock RAMЃЌПЩзїЮЊFIFOЁЃ ЪгЦЕDЃЏAзЊЛЛЦїбЁгУADV7175AЃЌИУЦїМўЪЧвЛПюадФмзПдНЕФЪ§зжЪгЦЕБрТыЦїЁЃПЩНЋЗћКЯCCIR601 4ЃК2ЃК2БъзМЕФЪ§зжЪгЦЕаХКХзЊЛЛЮЊБъзМЕФPAL/NTSCжЦЕФШЋЕчЪгаХКХЃЌзЊЛЛОЋЖШЮЊ10 bitЃЌВЩгУЕЅвЛ27MHzЕФЪБжгдДЃЌSNRзюИпДя80 dBЃЌЦфФкВПDЃЏAзЊЛЛЦїЕФЖРСЂПЊЙиПЩНЕЕЭЯЕЭГЙІКФЁЃ ИљОнИУЯЕЭГЪ§ОнДцДЂЫГађНјааВйзїЃЌЦфДцДЂЦїбЁгУK9K8G08IJOMаЭNAND FlashЁЃИУЦїМўЕФШнСПЮЊ8 GbitЃЌЪЧгЩ8 192ИіПщзщГЩЃЌУППщгЩ64вГзщГЩЃЌ8ЮЛIЃЏOзмЯпзїЮЊУќСюЁЂЕижЗЁЂЪ§ОнзмЯпЗжЪБИДгУЁЃ USBЭЈаХВПЗжбЁгУCY7C68013AЁЃИУЦїМўЪЧаТвЛДњИпЫйEZЁЊUSB FX2ЃЎФкВПМЏГЩСЫUSB 2ЃЎ0ЪеЗЂЦїЃЌЦфSIE(ДЎааНгПкв§Чц)ПЩЙЄзїдкИпЫй(480 MhЃЏs)ДЋЪфЫйТЪЯТЃЌОпгаUSB2ЃЎ0ЕФШЋДјПэЃЛCPUВЩгУдіЧПаЭ805lЃЌОпгаИќПьЕФдЫааЫйЖШЃЛМђЕЅвзгУЕФПЩБрГЬТпМНгПк(GPIF)ЮЊЭтВПЕФFPGAЬсЙЉЮоЗьСЌНгЫФЃЛСэЭтЛЙОпгаЦф3ЃЎ3 VЕФЙЄзїЕчбЙКЭФкВПМЏГЩЕФI2CзмЯпПижЦЦїЁЃ 2ЃЎ1 FlashЖСаДЫйЖШЕФЦЅХф гЩгк16ЦЌFlashВЂСЊЃЌДцДЂЪ§ОнЪБЃЌFPGAжЛФмЖдвЛЦЌFlashВйзїЃЌгжвђЮЊFlashЕФвГБрГЬЪБМфЙ§ГЄ(зюДѓЮЊ700ІЬs)ЃЌЫљвдДцДЂЪБгІдкаДЭъЕквЛЦЌFlashЕФЕквЛвГКѓНгзХаДЕкЖўЦЌFlashЃЌЕБТжбЏЭъЦфгр15ЦЌFlashКѓдйЛиаДЕквЛЦЌFlashЕФЕкЖўвГЃЌетбљПЩУтШЅвГБрГЬЕШД§ЪБМфЃЌШчЭМ2ЫљЪОЁЃСэЭтЛЙашПМТЧЃКаДЭъ15ЦЌFlashЕФpage0ЕФзюЖЬЪБМфЮЊ25 ns(FlashЕФзюаЁЖСЪ§жмЦк)ЁС2 048(УПвГ2 KзжНк)ЁС15(ЦЌ)=768ІЬsЃЌИУЪБМфДѓгквГБрГЬЪБМф700ІЬsЃЌМДаДЭъЦфгр15ЦЌFlashЕФpage0КѓЃЌдйЛиаДЕквЛЦЌFlashЕФpagelЃЌЖјЕквЛЦЌFlashЕФвГБрГЬвбНсЪјЃЌетбљдђВЛЛсдьГЩЪ§ОнЖЊЪЇЁЃ  ЪгЦЕЛиЗХЪБвЊПМТЧFlashгыADV7175AжЎМфЕФЖСЪ§ЫйЖШЦЅХфЮЪЬтЁЃзюЛЕЧщПіЯТЃКADV7175ЪАШЁЪ§ОнЪБжгЪЧ13ЃЎ5 MHzШчЭМ3ЫљЪОЁЃМйЩшУПИіЪБжгжмЦкЖМЪЧгааЇЪ§ОнЃЌFlashЕФЖСЪ§ЪБжгжмЦкTRзюаЁжЕЮЊ25 nsЃЌМДМЋЯоЖСЪ§ЫйЖШЮЊЃКfMAX=1ЃЏ25 ns=40 MHz>13ЃЎ5 MHzЃЌТњзуЯЕЭГвЊЧѓЁЃЕЋFlashЕФвГЖСЛКГхЪБМфtMAX=20ІЬsЃЌМДУПЖСШЁ2 KзжНкашЕШД§ЪБМф20ІЬs(зюДѓжЕ)ЁЃвЊТњзуЪ§ОнЕФСЌајадЃЌашдкFlashКЭADV7175жЎМфНЈСЂЛКГхФЃПщЃЌдђВЩгУl KBЕФЩюЖШзувдТњзуЯЕЭГвЊЧѓЁЃ  2ЃЎ2 ЖрЖЮМЧТМКЭбЁЖЮВЅЗХ ЮЊСЫЗНБуВйзїКЭЙлВьЃЌЯЕЭГОпБИбЁЖЮВЅЗХЙІФмЃЌМДдкМЧТМЪБНЋВЛЭЌЪБМфЖЮМЧТМЕФФкШнгшвдЗжЖЮКЭБъМЧЃЛЖјдкВЅЗХЪББЃжЄУПГЁЭМЯёЕФИїЯёЫиЕувЊбЯИёЖдЦыЃЌЗёдђЛсдьГЩЭМЯёДэЮЛЁЃШєвЊЗРжЙетжжЧщПіЗЂЩњЃЌПЩдкМЧТМЪБдкУПГЁЭМЯёЪ§ОнЧАМгвЛИізж0xAA55зїЮЊГЁБъжОЃЌгЩгкУПГЁЭМЯёЕФЪ§ОнСПЮЊ320x240x2=153 600(зжНк)ЃЌдкМгШыГЁБъжОКѓЕФЪ§ОнСїШчЭМ4ЫљЪОЁЃетбљЩшМЦЕФгХЕудкгкЃК  (1)дкПьНјЁЂПьЭЫВЅЗХЪБЃЌFlashЬјЕижЗКѓПЩМьВтИУБъжОжиаТЕїећЭМЯёЃЌСэЭтвВЮЊЪ§ОнЩЯДЋКѓЃЌЩЯЮЛЛњШэМўВЅЗХЬсЙЉЗНБуЁЃ (2)МгШыГЁБъжОПЩЪЕЯжЖрЖЮМЧТМЁЃгЩгкДцДЂЪБШЗБЃУПЖЮЪгЦЕЪ§ОнЕФЪззжНкЖМаДШыFlash_0ЕФblock_x(xБэЪОblockЕижЗКХ)ЕФpage0ЕФЪзЕижЗЃЌШчЭМ2жаЁЎЁЄЁЏЁЃдкЩЯЕчКѓаХЯЂЩЈУшЪБжЛашЩЈУшFlash_0ЕФИїblockжаpage0ЕФЧАИізжНкЃЌШчЙћЪЧ0xAAКЭ0x55дђБэУїаТМЧТМЖЮЃЌШчЙћВЛЪЧдђдйЖСШЁКѓ2ИізжНкЁЃШчЙћСЌај4Иіblockжаpage0ЕФЧА4ИізжНкЖМЪЧ0xFFЃЌдђБэУївбЩЈУшЫљгаЖЮЃЌДЫЪБгІНЋЖЮзмЪ§КЭДцДЂЦїЕФвбгУПеМфвдМАЯЕЭГзДЬЌаХЯЂЕШЗЂЫЭжСЕЅЦЌЛњНјЖјЫЭЕНLCDЯдЪОЁЃ 2ЃЎ3 ADV7175гыFPGAЕФНгПкЩшМЦ CCIRвЛ601БъзМЙцЖЈЃЌдкЪ§зжБрТыЪБЃЌВЛЪЙгУAЃЏDзЊЛЛЕФећИіЖЏЬЌЗЖЮЇЃЌжЛИјССЖШаХКХЗжХф220ИіСПЛЏМЖЃЌКкЕчЦНЖдгІгкСПЛЏМЖ16ЃЌАзЕчЦНЖдгІгкСПЛЏМЖ235ЃЌЮЊУПИіЩЋВюаХКХЗжХф224ИіСПЛЏМЖЃЌЩЋВюаХКХЕФСуЕчЦНЖдгІгкСПЛЏМЖ128ЃЌШчЭМ5ЫљЪОЁЃМДУПИібљБОЕуССЖШаХКХеМ220МЖЃЌЩЋЖШаХКХеМ225МЖЁЃ  гЩгкКьЭтШШЯёвЧЬсЙЉЕФЪ§ОнЪЧ16ЮЛЛвЖШжЕЖјЮоЩЋЖШжЕЃЌЫљвдгІНЋADV7175AЕФЕЭ8ЮЛ(P7"P0)ЪфШы0x80ЃЌОпЬхЕчТЗСЌНгШчЭМ6ЫљЪОЃЌИп8ЮЛЪфШыССЖШаХКХЃЌВЅЗХЪБашНЋ16ЮЛЕФССЖШаХКХзЊЛЛЮЊ8ЮЛдйЫЭШыADV7l75AЁЃ  3 FPGAТпМЩшМЦ ЭМ7ЮЊFPGAФкВПИїТпМЙІФмФЃПщПђЭМЁЃИїФЃПщжївЊЙІФмШчЯТЃКRECVФЃПщИљОнКьЭтШШЯёвЧЬсЙЉЕФЬиЖЈЪБађНгЪеЪ§ОнВЂБржЁЃЛFlashПижЦЦїПижЦ16ЦЌFlashЃЌгУгкЩЈУшЮоаЇПщКЭМЧТМЖЮЃЌМЦЫуFlashвбгУПеМфКЭЪЃгрПеМфМАЖдFlashЕФВСГ§КЭЖСаДВйзїЃЛаХЯЂМЧТМБэИКд№МЧТМFlashПижЦЦїДЋЫЭЕФЮоаЇПщКХМАвбМЧТМЕФЖЮзмЪ§КЭИїЖЮЕФЦ№ЪМЕижЗгыНсЪјЕижЗЃЛЛвЖШЕїНкФЃПщНЋ16ЮЛЕФЛвЖШЭМЯёЪ§ОнзЊЛЏЮЊ8ЮЛЃЌвђЮЊADV7175AзюЖрПЩЪфШы8ЮЛЛвЖШаХЯЂЃЛPALlФЃПщПижЦADV7175AЃЛPAL2ФЃПщЩњГЩдИёЪНЕФааГЁЪБађЃЌжївЊЕФПижЦаХКХЪЧааЭЌВНаХКХ(Hsync)КЭГЁЭЌВНаХКХ(Vsync)ЃЛFIF01КЭFIF02зїЮЊЪ§ОнЛКГхФЃПщЃЛTOвЛ68013ФЃПщПЩдкЯЕЭГгыМЦЫуЛњЭЈаХЪБЛЅЛЛTOвЛ68013AЕФЪ§ОнЃЛЛЙПЩЯђ68013AЗЂЫЭвЛаЉашвЊЯдЪОЕФЪЕЪБаХЯЂЃЛМќХЬЕФЩЈУшМААДМќЕФШЅЖЖдђгЩМќжЕДІРэФЃПщЭъГЩЃЎзюКѓгЩCPUФЃПщаЕїИїзгФЃПщЙЄзїЁЃ  4 Нсгя ИУЯЕЭГВЩгУFPGAзїЮЊжїПижЦЦїЃЌЖдгкВЛЭЌЗжБцТЪЕФКьЭтЭМЯёЪ§ОнЃЌжЛашаоИФFPGAжаЕФRECVФЃПщКЭPALФЃПщГЬађМДПЩЃЌвђДЫЃЌИУЯЕЭГЩшМЦОпгавЛЖЈЕФСщЛюадЁЃ |

ЭјгбЦРТл