DSP与PCI网卡接口设计

发布时间:2010-8-13 15:27

发布者:lavida

|

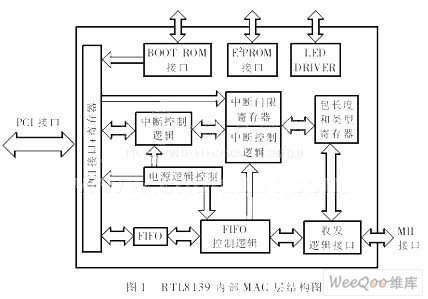

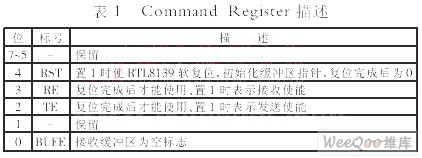

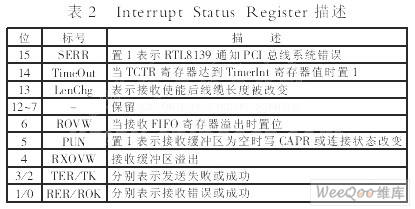

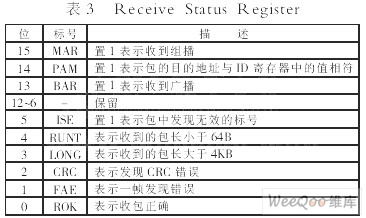

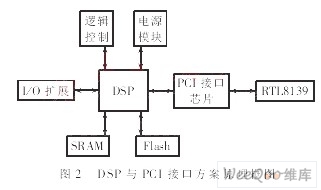

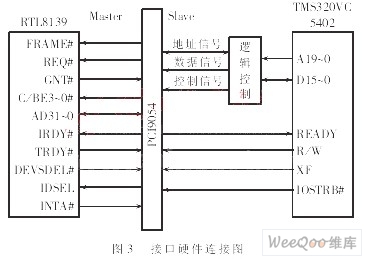

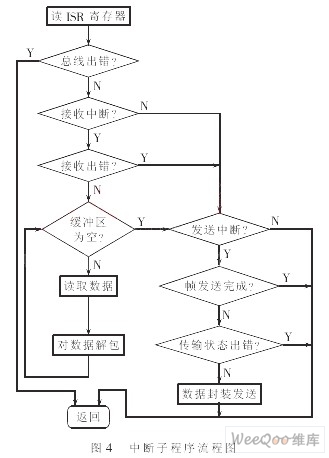

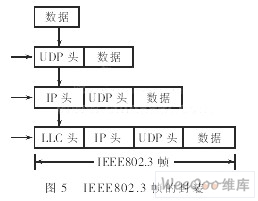

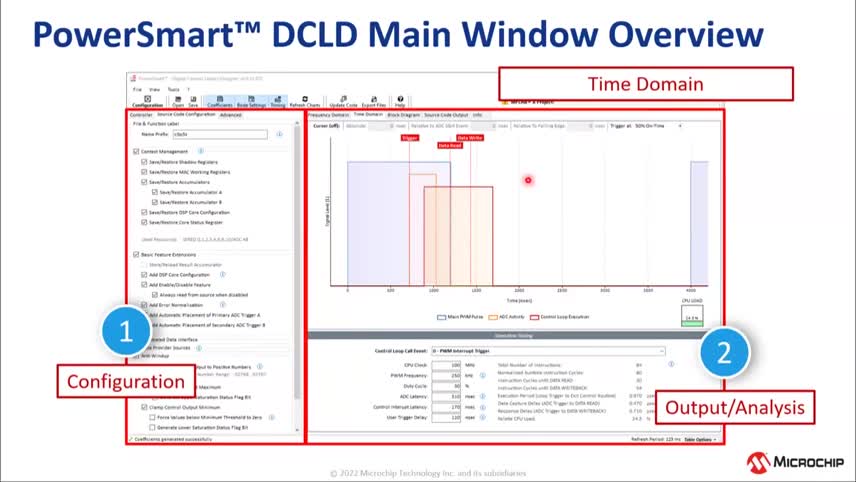

基于DSP的嵌入式系统的以太网接口设计一直是热门领域,目前利用的以太网控制器大多都是ISA接口。随着PCI总线逐渐取代ISA总线的趋势,使PCI接口的以太网控制器也成为PC机的主流,但在嵌入式领域中PCI总线的应用目前并不多见。本文将介绍利用Realtek公司生产的具有PCI接口的以太网控制芯片RTL8139实现RTL8139与DSP接口的方案。 1 RTL8139 RTL8139是带PCI接口的10M/100M自适应网卡控制芯片,它提供32位PCI总线控制,支持IEEE802.3u 100Base-T和IEEE802.3x的全双工流量控制;符合PCI 2.2标准,支持高级配置和电源接口(ACPI)和PCI对现代操作系统的电源管理(即对操作系统的直接电源管理),以提高电源管理的效率。此外,RTL8139还支持128KB的Boot ROM,提供网络唤醒和远程唤醒功能;含有2个2KB的收发FIFO;能够降低网络维护成本,消除使用障碍,而且可以很方便地使网络由10M升级到100M,且带宽可以达到200Mbps。RTL8139内部MAC层结构如图1所示。  1.1 RTL8139的PCI接口 PCI总线分为主(Master)、从(Target)二种类型,Master可以控制PCI总线,Target不能控制PCI总线。标准的主设备至少有49条线与PCI总线相连;从设备至少有47条线与PCI总线相连。RTL8139所提供的PCI接口有51条引脚,其引脚简介如下。 (1)地址/数据信号 AD31~0:地址、数据多路复用的输入/输出信号,在FRAMEB有效时,是地址期;在IRDYB和TRDYB同时有效时为数据期。 C/BE3~0:总线命令和字节使能多路复用信号,负责传输总线命令。在数据期,由传输字节使能信号来表示数据线上哪些字节是有效数据。 (2)接口控制信号 FRAMEB:帧周期信号,表示访问的开始和持续时间。 IRDYB、TRDYB:分别表示主、从设备准备好信号,二者必须配合使用,同时有效时方能进行数据传输。 STOPB:目标设备请求停止数据传输信号。 IDSEL:初始化设备选择信号,在参数配置读写传输期间,用作片选信号。 DEVSELB:设备选择信号。 (3)仲裁信号 REQB:总线占用请求信号,表示RTL8139申请总线控制权。 GNTB:总线占用允许信号,表示总线控制权已经交给RTL8139。 主设备都必须有以上2种信号。 (4)错误报告信号 PERRB:数据奇偶校验错误信号。 SERRB:系统错误信号。 (5)其他信号 CLK:时钟信号,最高可达33MHz。 CLKRUNB:时钟运行信号,这是RTL8139增设的信号,用来请求时钟开始和表示时钟状态。 RSTB:复位信号,低电平有效,至少需要120ns的宽度。 INTAB:中断请求信号,它需要与RTL8139的ISR和IMR寄存器配合使用。 在嵌入式系统中并不需要连接所有的引脚,可根据系统的实际需要进行选择。 1.2 主要寄存器 RTL8139的寄存器映射到I/O空间,I/O空间有256个地址,地址偏移量为00H~FFH。下面介绍几个比较重要的寄存器。 (1)Command Register 该寄存器地址偏移量为0037H,功能为软复位网卡,使能网卡的发送和接收。其描述如表1所示。  (2)Interrupt Status Register 该寄存器地址偏移量为3EH~3FH,在INTA引脚有效时表示中断源,与IMR寄存器配合使用,它的值影响当前所有中断。其描述如表2所示。  (3)Receive Status Register 该寄存器通常可以从数据包的包头中读出,是RTL8139芯片特有的。通过它可以知道网卡收包的状态以便进行接收处理。其描述如表3所示。  2 系统设计方案 根据RTL8139的以上特点,作者设计了RTL8139与DSP之间的接口解决方案。目前DSP与PCI的接口一般有二种方案  1)用CPLD来实现。优点是可以进行功能优化,不必实现所有PCI协议的功能,节约系统资源。占用系统资源大的用户可以做成ASIC,有利于降低成本。但由于PCI协议的复杂性,短期内还难以做到操作稳定。(2)用专门的PCI桥芯片。PCI芯片功能强大,可减少开发时间和成本并能获得较好的传输特性。目前市场上有许多PCI桥芯片产品,最为常见的是AMCC、PLX、CYPRESS等公司的产品,作者选用PLX公司的PCI9054作为本系统的PCI接口芯片。DSP与PCI接口设计方案如图2所示。 1)用CPLD来实现。优点是可以进行功能优化,不必实现所有PCI协议的功能,节约系统资源。占用系统资源大的用户可以做成ASIC,有利于降低成本。但由于PCI协议的复杂性,短期内还难以做到操作稳定。(2)用专门的PCI桥芯片。PCI芯片功能强大,可减少开发时间和成本并能获得较好的传输特性。目前市场上有许多PCI桥芯片产品,最为常见的是AMCC、PLX、CYPRESS等公司的产品,作者选用PLX公司的PCI9054作为本系统的PCI接口芯片。DSP与PCI接口设计方案如图2所示。  DSP选用TI公司的TMS320VC5402,它的运算速度达100MIps,硬件接口功能强大(具有串行口、HPI主机接口和DMA控制器等),而且价格低廉,具有很高的性价比。接口的硬件连接如图3所示。  图3中,DSP通过PCI9054来读写PCI内存,地址空间由PCI的基地址开始。PCI9054作为DSP的从设备和RTL8139的主设备。当PCI写时,接收写信号,返回ready信号直到写FIFO满为止,并保持ready信号到写FIFO可用。当PCI9054从RTL8139读出数据时将保持ready信号,直到BALST信号(表示PCI总线上的最后传输)有效,读周期被终止,没有读出的数据将被FIFO舍弃。 要使嵌入式DSP系统要独立运行,必须外接EPROM或Flash存储器用于存放程序。与EPROM相比,Flash芯片功耗低,支持在工作电压下的擦写,可以方便地编写自己的Flash芯片烧录程序,通过在片方式完成对Flash芯片的写操作。本设计采用的是SST公司生产的SST39VF400A,它是一款基于CMOS技术的高性能、多用途的Flash存储芯片,其存储容量达4Mb,功耗低,使用2.7~3.3V单电源供电。为了方便程序的调试,外接了1片64K×16b的SRAM,以用于存放发送数据和接收数据,以便于对比,及时地发现数据传输的正确性。逻辑控制部分主要用于主处理器对外设(如PCI桥芯片、网络适配芯片、SRAM及Flash等)的读写控制及地址分配。 3 软件设计 软件设计主要分为PCI网桥和网络接口二部分。PCI网桥部分主要是对PCI9054进行初始化,即对它的PCI端配置寄存器和本地端配置寄存器进行正确的编程配置,以实现DSP与PCI网卡的无缝连接。网络接口部分的编程包括对RTL8139进行复位初始化,数据包的接收和发送。 RTL8139已经实现了OSI中的物理层和数据链路层的功能,只需再加上高层协议即可。作为一个嵌入式系统,为了节省系统资源,需要尽量使用简化的协议。因此IP地址和本机物理地址在初始化RTL8139时设定,采用本地管理的地址方式,上层协议进行了简化,没有封装复杂的TCP协议。 简化的网卡初始化程序如下: #define CMD_RST 0x10 //复位标志 #define CMD_RE 0x08 //接收使能 #define CMD_TE 0x04 //发送使能 #define SUCCESS 0xFF //网卡初始化成功标志 Reset_init_rtl8139() { CMD=0x10;//软复位网卡 while((read_cmd & CMD_RST)==0) read_cmd=CMD; //检查网卡是否复位完成 write_mac_ip();//设定网卡的MAC地址和IP地址 CMD=CMD_RE | CMD_TE; //接收发送使能 set_RxConfig(); //接收配置 set_TxConfig(); //发送配置 init_rx_addr(); //初始化接收缓冲区地址 Rxmissed=0; //clear 0 CMD=CMD_RE | CMD_TE; return SUCCESS; } 程序中:CMD为RTL8139的Command寄存器,通过它来对芯片复位并检查复位成功与否;write_mac_ip()是向IDR0"IDR5写入MAC地址,设定IP地址;set_RxConfig()主要是对Receive Configuration Register进行设置。此外,网卡初始化程序设定只接收物理地址匹配的包,不接收组播和广播。 RTL8139接收缓冲区的大小可选,并设定为16KB。初始化过程中根据DSP的快慢还需要加一些延时,这一点非常重要。因为许多寄存器的设置都需要时间,若时间不够,某些寄存器的值可能会设置不正确,从而导致初始化失败,RTL8139的收发功能也会受到影响。 RTL8139数据的收发用中断方式完成。当主处理器要向网上发送数据时,先将1帧数据通过DMA通道送到控制器的发送缓冲区,然后发出传送命令,RTL8139按照PCI总线主模式将数据从发送缓冲区转移到内部发送FIFO中。当FIFO中数据包完整时,RTL8139即开始包发送。控制器在数据发送完成后通过中断方式通知主处理器;接收数据时,网上来的数据包首先被放在接收FIFO中,同时RTL8139要进行组播地址过滤。当接收FIFO中数据包已达到接收配置寄存器的要求时,RTL8139请求PCI总线按照PCI主模式将数据传到接收缓冲区,接收满1帧后,同样以中断方式通知主处理器。数据的收发是通过 DMA通道来完成的。中断子程序流程图如图4所示。  数据包的封装按照IEEE802.3协议、IP协议和UDP协议,其帧格式如图5所示。  封装的过程依次在源数据前加上UDP头、IP头和LLC头。LLC头即通常所说的以太网包头,但也可以根据自己的需要加上其他协议如TCP、ARP或HTTP。不过在嵌入式系统中,为了节省资源,应尽量减少协议的使用。在分组语音数据传输中,实时语音数据可以用UDP,而控制信号可以用TCP。 4 结束语 本文所提出的DSP与RTL8139的接口解决方案已在试验中得到实现,并已用于IP分组语音数据的以太网传输,效果良好。随着ISA总线的淘汰,PCI接口的网络控制器必将在嵌入式领域中得到更广泛的应用。 |

网友评论