基于FPGA的多通道数据采集系统设计

发布时间:2010-8-13 15:26

发布者:lavida

|

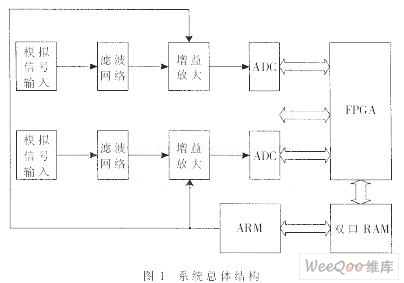

大地电磁场携带着地球内部的结构、构造、温度、压力以及物质成分的物理状态等信息,为人们研究板块运动的规律、追溯地球的演化历史提供了科学依据。大地电磁探测是研究大陆岩石圈导电性结构的有效方法之一,使人们从电性角度认识地球内部的构造形态,达到了解地下不同深度地质情况的目的。该技术应用前景广泛,可用于地下更深层找矿、找水、找油、监测海底潜艇等,对国民经济和国防的发展都有重要的推动作用。 最常用的数据采集方案多以MCU为核心,控制多路信号的采集及处理。但由于单片机本身的指令周期以及处理速度的影响,对于多通道A/D进行控制及数据处理,普通的MCU往往不容易达到要求。考虑到FPGA器件的高集成度、内部资源丰富、特别适合处理多路并行数据等明显优于普通微处理器的特点,并针对大地电磁数据采集系统对实时性和同步性的要求,本文提出了一种多通道数据采集方案。采用FPGA与ARM相结合的设计,采集主控制逻辑用FPGA实现,ARM用来实现采集数据的存储和数据传输控制。 1 系统总体结构 系统总体结构如图1所示。A/D转换器采用TI公司的24位高精度模数转换器ADS1255;FPGA采用Altera公司的EP2C35;ARM为ARM9内核的处理器S3C2410。双口RAM由EP2C35内部存储器块配置而成,该双口RAM与ARM的系统总线相连,映射为ARM的一块内存区。  AD前端处理电路的作用是实现对信号的放大、衰减以及阻抗匹配,从而满足ADC对输入信号的要求。滤波网络滤除高频噪声和工频信号的干扰,增益放大通过ARM给出的控制信号实现对模拟信号的不同增益的放大处理。ADS1255负责把模拟电信号转换成数字信号,可以通过功能选择设置ADS1255工作在不同的工作模式下。ADS1255的工作时钟由FPGA提供,改变FPGA输出时钟的频率就能实现AD采样率的改变。FPGA并行控制5路AD的数据采集,并把采集到的各路数据按顺序以字节的形式写入双口RAM中缓存。FPGA对双口RAM的数据写入和ARM对数据的读取是通过乒乓传输结构实现的。当FPGA写满双口RAM上半区后,向ARM申请中断,ARM响应中断后,读出上半区数据到内存中进行存储;同时FPGA向RAM的下半区写数据,写满下半区后也向ARM发出中断,通知ARM读出下半区数据。通过乒乓传输保证了系统数据采样和数据传输可以连续进行。 2 FPGA的逻辑设计 本方案中的数据采集流程如下:系统初始化后,ARM通过控制信号把采样频率、通道选择等参数通知给FPGA,然后FPGA向需要同步采样的通道对应的AD芯片提供统一时钟,使得AD同步地选择相应的通道进行数据的同步采样和转换,其结果由FPGA接收并存储在双口RAM对应的存储空间,然后由ARM从相应的双口RAM空间读取数据进行本地存储或经过网络传输给上位机进行处理。根据以上流程以及FPGA要实现的功能,整个FPGA逻辑设计划分为通道和采样率选择模块、时钟模块、双口RAM模块、AD采样控制模块、串并转换模块、数据存储控制模块、ARM接口控制模块。 各模块连接关系如图2所示。  2.1 通道和采样率选择模块 在实际应用中并不是每个通道都被使用,AD的采样率也不只一种,所以在通道的控制和采样率设置上应该具有可选择性。 通道和采样率选择模块提供2个8 bit的控制寄存器A和B。如图3所示,寄存器A的0~4 bit分别对应ADC通道CH0~CH4,5~7 bit保留;寄存器B的8 bit分别对应采样率FS0~FS7。如果要选择某几个通道,只需将寄存器A中相应的位置1,其他位置0,AD采样控制模块就会根据该寄存器中的内容使能相应的通道。如果要选择某一个采样频率,只需把寄存器B中相应的位置1,其他位置0,时钟模块会产生相应的时钟控制AD的采样率。在开启数据采集之前,ARM应根据所要求的通道和采样频率向寄存器A和B写入相应命令字。  2.2 时钟模块 本设计中外部输入时钟为16.384 MHz。由于设计中各个模块工作时钟的不同以及AD采样率的变化,所以需要多种不同的时钟信号。时钟模块的功能就是根据不同采样率为各个模块提供所需的时钟信号。由于该设计采用同步时序电路,它是基于时钟触发沿设计,对时钟的周期、占空比、延时、抖动提出了较高的要求,为此本设计中采用FPGA所带的PLL时钟资源驱动设计的主时钟,使其达到最低的时钟抖动和延迟。 2.3 双口RAM模块 本设计中双口RAM用于数据缓存,一方面存储各个AD芯片转换的数据,另一方面供ARM读取数据做进一步的存储与处理。它具有真正的双端口,可以同时对其进行数据存取,两个端口具有独立的控制线、地址线和数据线。该双口RAM模块是通过调用Altera FPGA自带的参数化模型库(Mega-lpm)实现的。 2.4 A/D采样控制模块 A/D采样控制模块的主要任务就是根据ADS1255的转换时序图,在其芯片的引脚发出相应的时序控制信号,使ADS1255完成启动、配置和数据读取等操作。ADS1255的控制操作如下:首先设置ADS1255的参数配置,读数据模,然后启动转换,通过查询ADS1255的DRDY信号判断是否转换完成,转换结束后将数据按bit顺序读出。同时将数据输出给串并转换模块,完成一次A/D转换操作。采样控制模块每完成一次采样操作,则停止等待下一个触发脉冲的到来。  这一控制过程通过状态机实现。图4给出了该A/D转换控制模块的状态转换图。当数据采集启动信号START为高电平时,状态机启动。 状态机的各个状态描述如下: (1)conv_init:状态机的初始状态。 (2)mode_set:设置ADS1255内部的控制寄存器。 (3)conv_start:启动A/D转换。 (4)conv_wait:等待A/D转换结束。如果转换结束则进入下一状态,否则将继续保持在该状态。 (5)conv_read:A/D转换结束后读出每个bit信息,同时使能移位寄存器进行串并转换。 (6)read_next:判断数据是否读完。如果没有返回conv_read状态,否则进入下一状态。 (7)conv_next:判断是否需要继续转换数据。如果没有就进入下一状态,否则返回conv_start状态。 (8)cony_end:表示本次采样任务结束。状态机保持在该状态,直到采样启动脉冲触发重新开始新的一次采样任务,状态机复位到conv_init状态。 2.5 串并转换模块 由于ADS1255是以串行输出转换结果的,故需要该模块将串行输出的数据转换为井行输出。该模块主要采用移位寄存器来实现,其移位控制信号由AD采样控制模块提供。 2.6 数据存储控制模块 该模块的作用是将5通道24 bit经过串并转换的采样数据按通道顺序,以从低字节到高字节的次序,一个一个字节将其写入双口RAM中,实际上相当于一个字节意义上的并串转换。该模块输入为5路采样数据reg24Data_0~4,dataF为输出的字节数据,wrenF为双口RAM的写控制信号。图5是一个五通道数据存储的仿真示意图。输入数据值分别为0x030201、0x060504、0x090807、0x121110、0x151413,输出字节数据为01~15,同时使能写RAM,满足设计要求。 2.7 ARM接口控制模块 该模块为ARM与FPGA及其双口RAM交互提供桥梁。当ARM向控制寄存器写入采集参数信息时,接口模块要将该信息通知通道和采样率选择模块;当ARM读取双口RAM中的数据时,接口模块对ARM的访问地址进行译码,选中对应的存储空间取出数据。 本文采用FPGA和ARM结合设计,很好地完成了多通道高精度的数据采集与处理,并且还详细介绍了FPGA逻辑的设计方法。FPGA逻辑通过硬件描述语言Verilog实现,已应用到磁数据采集系统中。本方案设计灵活,能很容易地扩展为更多路的数据采集,也能很容易地修改为与其他的A/D转换芯片接口。所以该方案可根据不同的应用进行扩展,进一步增强了系统应用的灵活性。 |

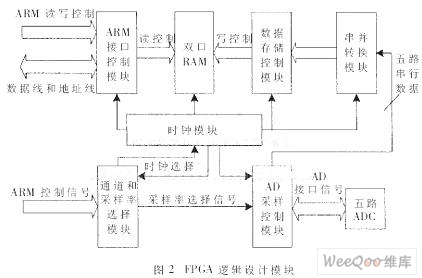

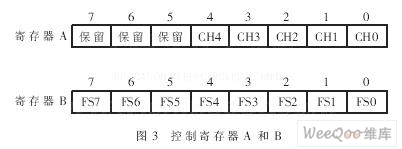

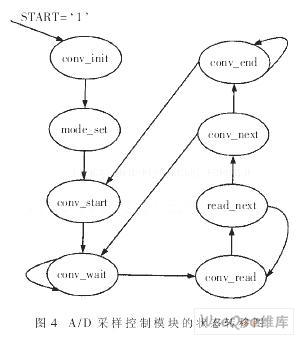

网友评论