ЛљгкзЫЬЌВтСПЕФЮЂаЭДцДЂЯЕЭГЕФЩшМЦ

ЗЂВМЪБМфЃК2010-8-12 18:09

ЗЂВМепЃКlavida

ЙиМќДЪЃК

ЗЩаа

|

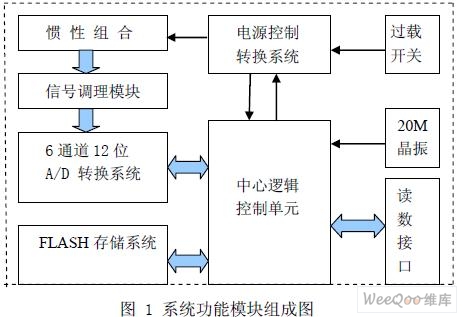

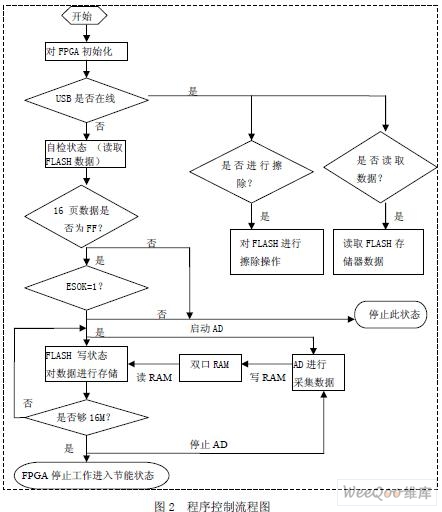

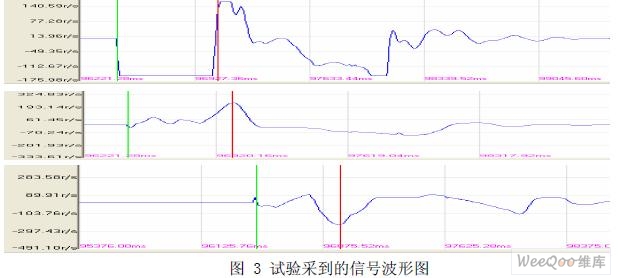

еЊвЊЃКБОЮФжївЊНщЩмСЫЮЂаЭДцДЂВтЪдЯЕЭГдкзЫЬЌВтСПжаЕФЩшМЦЃЌНсКЯЗЩааЬхдкЗЩааЪБИїжжБфЛЏзЫЬЌЕФВЩМЏЃЌБржЁЃЌДцДЂетвЛЮЪЬтЃЌЯъЯИЕиВћЪіСЫЮЂаЭДцДЂВтЪдЯЕЭГЕФЙЄзїдРэЁЂЯЕЭГзщГЩЁЂШэгВМўЩшМЦвдМАЫљЪЕЯжЕФадФмжИБъЃЛИљОнЮЂаЭДцДЂВтЪдЯЕЭГЕФОпЬхЙЄзїЙ§ГЬЃЌНсКЯДѓСПЕФХзШіЪдбщЃЌРћгУFPGAБШНЯЯЕЭГЕФЩшМЦКЭЭъЩЦСЫЮЂаЭДцДЂЦїЕФИїИіЙЄзїзДЬЌЃЌЬсИпСЫДцДЂЦїЯЕЭГЙЄзїЕФПЩППадЃЌзюКѓЭЈЙ§ШэМўЖдЪдбщЪ§ОнЕФЖСШЁКЭЗжЮіЃЌбщжЄИУЮЂаЭВтСПЯЕЭГЕФе§ШЗадЁЃ ИХЪі ЮЂаЭзЫЬЌВтЪдЯЕЭГдкКНЬьПЦММСьгђЦ№зХдНРДдНживЊЕФзїгУЃЌЖдШЗЖЈЗЩааЬхИїжжЗЩаазЫ ЬЌгазХживЊЕФВЮПМвтвхЁЃдкВтЪдСьгђжаЃЌЕЭЙІКФЃЌаЁЬхЛ§ЃЌдыЩљаЁЃЌДѓШнСПвбЪЧОКељЕФжївЊ ФПБъЁЃЮЂаЭзЫЬЌВтЪдЯЕЭГжївЊгУгкЗЩааЬхХзШіКѓЕНТфЕиЧАЕФШ§ЯђНЧЫйЖШМАЯпМгЫйЖШВЮЪ§ЕФВт СПЁЂВЩМЏЁЂБрТыКЭМЧТМЃЌВЂдкЗЩааЬхгВЛиЪеКѓЭъГЩвЃВтЪ§ОнЕФЪТКѓЖСШЁКЭДІРэЁЃ дкБОЮФЕФЩш МЦжаЃЌЗЩааЬхзЫЬЌЮЂаЭДцДЂЦїВтЪдЯЕЭГДяЕНВЂТњзуСЫДЋЭГЩЯФбвдЪЄШЮЕФИпадФмжИБъКЭаэЖрММ ЪѕЩЯЕФПСПЬвЊЧѓЃЌЦфжаЬхЛ§аЁЃЌЕЭЙІКФЃЌПЙЙ§диадФмИпЪЧБОЮФЩшМЦЕФжївЊЗНУцЁЃДгЯЕЭГНсЙЙ ЩшМЦЁЂЕчдДЩшМЦвдМАзДЬЌЩшМЦЕШЛЗНкБЃжЄСЫаЁЬхЛ§ЁЂЕЭЙІКФЕФЩшМЦвЊЧѓЃЌвВЬсИпСЫећИіЯЕЭГ ЕФПЙИпЙ§диадФмЁЃ 1 ЮЂаЭзЫЬЌДцДЂВтСПЯЕЭГЕФФЃПщзщГЩМАЙЄзїдРэ[1] ШчЭМ1 ЫљЪОЃЌЮЊЮЂаЭзЫЬЌДцДЂВтСПЯЕЭГПђЭМЁЃећИіЯЕЭГгЩЙ§диПЊЙиЁЂЙпадзщКЯЁЂЕчдДПи жЦМАБфЛЛЕчТЗЁЂаХКХЕїРэЕчТЗЁЂA/D зЊЛЛЯЕЭГЁЂжааФПижЦТпМЕЅдЊЁЂFLASH ДцДЂЦїКЭЖСЪ§Нг ПкЕчТЗЕШзщГЩЁЃ  ЗЩааЬхдкПежаЗЩаажаЕБДяЕНЖюЖЈЕФЙ§диСПЪБЃЌЯЕЭГНЋгЩЙ§диПЊЙиРДДЅЗЂЦєЖЏаХКХЃЌЗЩаа ЬхЕФШ§ЮЌНЧЫйЖШМАЯпМгЫйЖШВЮЪ§гЩЙпадзщКЯзЊЛЏЮЊЙЉМЧТМЦїВЩМЏЕФФЃФтаХКХЃЌМЧТМЦїНЋдк FPGA жааФПижЦЕЅдЊЕФЪБађПижЦЯТЖдФЃФтаХКХНјааВЩМЏЁЂБржЁКЭДцДЂЃЌЕБМЧТМЦїБЛЪеЛиЪБЃЌ НЋгЩЕиУцМьВтЯЕЭГЖдДцДЂЦїЕФЪ§ОнНјааЖСШЁКЭЪТКѓДІРэЁЃ ЕчдДПижЦМАБфЛЛФЃПщНгЪеЕНЁАЦєЖЏЁБУќСюКѓЃЌОЭНЋЗЩааЬхЩЯзАдиЕФЕчдДОзЊЛЏЪфГіИјЙп адзщКЯЙЉЕчЃЌЭЌЪБНЋЯЕЭГЕчГиОЙ§БфЛЛЪфГіЯЕЭГ3.3V ИјећИіМЧТМзАжУЙЉЕчЁЃаХКХЕїРэФЃПщОЭЪЧАбЙпадзщКЯаХКХЕїРэГЩПЩвдБЛМЧТМзАжУНгЪеЕФ0ЁЋ3.3V аХКХЃЌЭЌЪББЃжЄМЧТМзАжУзуЙЛЕФ ЪфШызшПЙЃЌМДВЛгАЯьБЛВтаХКХЕФЕчЦјЬиадЁЃ 6 ЭЈЕР12 ЮЛA/D зЊЛЛЯЕЭГЕФЙІФмЪЧдкжааФПижЦ ТпМФЃПщЕФПижЦЯТЃЌАДее12KHz ЕФВЩбљТЪЖдЙпадзщКЯЫЭРДЕФ6 ТЗаХКХНјааВЩМЏЃЌВЂНЋВЩМЏЕН ЕФЪ§ОнЫЭЕНжааФПижЦТпМФЃПщжаЁЃ жааФПижЦТпМФЃПщЪЧећИіМЧТМзАжУЕФКЫаФВПЗжЃЌЫќЕФЙІФмЪЧЖд6 ЭЈЕР12 ЮЛA/D зЊЛЛЯЕ ЭГЫЭРДЕФЪ§ОнАДЫГађВЩМЏКѓЫЭШы128M ШнСПЕФ8 ЮЛ FLASH ДцДЂЦїжаЃЌЦфТЗВЩбљТЪЮЊ2KHzЁЃ дк жааФПижЦТпМФЃПщПЊЪМЙЄзїЕФЭЌЪБЃЌОЭЫцжЎЗЂГіЁАздБЃЁБУќСюИјЕчдДПижЦМАБфЛЛФЃПщЃЌвдБЃ жЄЕчдДПижЦМАБфЛЛФЃПщМДЪЙдкЙ§диПЊЙидйЖЯПЊКѓШдФме§ГЃЙЄзїЃЌМДБЃжЄЙ§диПЊЙиЕФДЅЗЂгааЇ адЁЃ128M ШнСПЕФ8 ЮЛFLASH ДцДЂФЃПщжївЊгУгкЪ§ОнЕФДцДЂЃЌЦфШнСПЮЊ128MЃЌЪ§ОнЮЛЮЊ8 ЮЛЁЃ гЩгкFLASH ДцДЂЦїОпгаЕєЕчБЃГжЪ§ОнЕФЙІФмЃЌЫљвдВЛашвЊЩшМЦКѓБИЕчГиНјааЕєЕчБЃЛЄЪ§ОнЁЃ ИљОнЧАУцЕФММЪѕжИБъПЩжЊЃЌ128M ЕФШнСПдЖТњзуЫљвЊЧѓЕФДцДЂШнСПЁЃ ЖСЪ§НгПкФЃПщжївЊгУгк МЧТМзАжУМьВтЪБКЭЛиЪеКѓЪ§ОнЕФЖСШЁЁЃ 2 ЮЂаЭДцДЂЦїЯЕЭГЕФгВМўЩшМЦ ЮЂаЭзЫЬЌДцДЂЦїВтЪдЯЕЭГЖдЕчдДгаПСПЬЕФвЊЧѓЃЌвђЮЊДЫВтЪдЯЕЭГгЩЕчГиЙЉЕчЃЌИљОнЕЭЙІ КФЕФЩшМЦддђЃЌБОЩшМЦВЩгУСЫMAX8882 ЕФЕЭбЙВюЕчдДПижЦаОЦЌЃЌЖдЪфШы3.5VЁЋ5V ЕчбЙФмЭЌ ЪБзЊЛЛГі3.3V КЭ2.5 ЕчбЙЃЌЭЈЙ§ТпМГЬађПижЦЕчдДаОЦЌПЩгааЇПижЦећИіЯЕЭГЕФКФЕчСПЁЃЕБ ЦєЖЏЕчдДПижЦЯЕЭГЪБЃЌТпМПижЦжааФВњЩњздБЃаХКХРДПижЦMAX8882 ЕФshutdown ЪЙФмЖЫЃЌЪЙ ећИіЯЕЭГе§ГЃЙЉЕчЁЃЕБВЩМЏДцДЂЙ§ГЬЭъГЩЪБЃЌТпМПижЦжааФВњЩњДЅЗЂаХКХРДПижЦMAX8882 ЭЃжЙЙЄзїЃЌДгЖјећИіЯЕЭГДІгкНкФмзДЬЌЁЃ ЮЂаЭзЫЬЌДцДЂЦїЕФЕчТЗЩшМЦЫМТЗжївЊвРОнЖдЗЩааЬхЕФзЫЬЌВЮЪ§НјааЪЕЪБВЩМЏЃЌБржЁКЭДц ДЂетвЛЫМТЗНјааЩшМЦЃЌаХКХЕїРэЕчТЗЪЧНЋзЫЬЌФЃФтаХКХНјааЗжбЙЁЂТЫВЈКЭИњЫцдЫЗХКѓДЋЫЭЗЂ ИјФЃЪ§зЊЛЛаОЦЌЃЌ ФЃЪ§зЊЛЛЕчТЗВЩгУСЫУРаХЙЋЫОЕФMAX1295 аОЦЌЃЌЫќЪЧ6 ЭЈЕР12 ЮЛОЋЖШж№ ДЮБЦНќЪНЕФЪ§ФЃзЊЛЛЦїЃЌВЩбљТЪЮЊ265Ksps,ЦЌФкМЏГЩСЫИпадФмЕФВЩбљБЃГжЕчТЗКЭВЮПМЕчбЙ дДЁЃЭЌЪБЛЙОпгаНЯЕЭЕФЙІКФКЭНЯИпЕФаХдыБШЃЌПЩвдНјааФкВПКЭЭтВПЕФВЩбљФЃЪНЩшжУЃЌдкБОЩш МЦжаВЩгУСЫЭтВПВЩбљФЃЪНЁЃ ДцДЂЯЕЭГВЩгУСЫШ§аЧЙЋЫОЕФK9F1G08 FLASH ДцДЂЦїЃЌИУаОЦЌадФмСМКУЃЌЗтзАНЯаЁЃЌЮЊ ЮЂаЭЛЏВтЪдЯЕЭГЩшМЦЬсЙЉСЫБуРћЃЌдкТпМжааФЕФЪБађПижЦЯТЃЌЖдДцДЂЦїНјааЖСЁЂаДЁЂВСГ§Вй зїЃЌУПжжВйзїЖМВЩгУСЫгЩFLASH ЕФзДЬЌаХКХr/b НјаажаЖЯЕФЗНЪНЁЃдкаДВйзїЙ§ГЬжаЃЌвд8 ЮЛЪ§ОнНјааДцШЁЃЌдкДцДЂвЛвГЪ§ОнЪБвЊНјаавГБрГЬЃЌДѓдМвЊ300usЁЋ700us ЃЌЕШД§r/b зДЬЌ аХКХЕФИФБфКѓНјШыЯТвЛвГЕФДцДЂЃЌЮЊСЫЪЙВЩМЏКЭДцДЂЕФЫйЖШЯрЦЅХфЃЌдкFPGA ФкВПВЩгУСЫ8K Bits ЕФЫЋПкRAMЃЌдкFLASH ДцДЂЦїНјаавГБрГЬЕФЪБКђНјааЪ§ОнЕФЛКДцЁЃдкВСГ§ВйзїЙ§ГЬжаЃЌЖд FLASH ДцДЂЦївЊНјааПщВСГ§ЃЌВСГ§вЛПщЪБМфвЊ2msЁЋ3ms,ЕШД§r/b зДЬЌаХКХЕФИФБфКѓНј ШыЯТвЛПщЕФВСГ§ЁЃЭЌбљдкЖСШЁЪ§ОнВйзїжаЃЌУПЖСШЁвЛИізжНкЖМвЊЕШД§r/b ЕФжаЖЯЃЌЪ§ОнЭЈЙ§ МьВтЬЈКЭUSB ЕчРТДЋИјЩЯЮЛЛњЁЃ БОДЮЩшМЦЕФЮЂаЭзЫЬЌДцДЂЦїВтЪдЯЕЭГЕФСэвЛИіжївЊЭЛГіЕудкгкЫќЕФЮЂаЭЛЏ ЃЌећИіЕФМЧ ТМЦїЕФИїИіаОЦЌЖМВЩгУСЫаЁаЭЛЏЕФЬљЦЌЗтзАЃЌЕчТЗАхВЩгУСЫЫФВуАхЙЄвежЦзїЃЌжаМфЗжБ№ЮЊЕч дДВуКЭЕиВуЃЌВЛНіДѓДѓНЯаЁСЫМЧТМЦїЕФЬхЛ§ЃЌЭЌЪБЖдаХКХЕФИєРыКЭПЙИЩШХадвВЦ№ЕНСЫвЛЖЈЕФ Л§МЋзїгУЁЃ  3 ТпМСїГЬЭМЩшМЦ СїГЬЭММћЭМ2 ЫљЪОЃЌећИіЙ§ГЬгЩЙ§диПЊЙиЦєЖЏЕчдДПижЦаОЦЌвдЦєЖЏећИіFPGA ЕФПижЦ ЪБађЃЌИДЮЛФЃПщгЩЩЯЮЛЛњИДЮЛЃЌЩЯЕчздЖЏИДЮЛКЭШэИДЮЛзщКЯЖјГЩЃЌЕБЦєЖЏећИіЯЕЭГЪБЃЌЪзЯШ вЊЖдЯЕЭГГѕЪМЛЏИДЮЛЃЌЭЌЪБЖЈвхвЛИіДЅЗЂаХКХЁАesokЁБЪЙГѕЪМЛЏЮЊЁА0ЁБЃЌвдБуДЅЗЂПижЦЕЅдЊЃЌ ЪЙЯЕЭГНјШыздМьзДЬЌЃЌдкздМьФЃПщжаЃЌFPGA ЪзЯШвЊДгFLASH ДцДЂЦїЕкСљвГСЌајЖСШЁ16 вГЕФ Ъ§ОнЃЌВЂХаЖЯЪ§ОнЪЧЗёЮЊЁАFFЁБЃЌШчЙћВЛЪЧЃЌдђДцДЂЦїФкгаЪ§ОнДцдкЃЌЯЕЭГНЋЭЃжЙдкетИізД ЬЌЃЛШчЙћЪЧдђДЅЗЂаХКХЁАesokЁБЮЊЁА1ЁБ вдЦєЖЏA/D ВЩМЏЪ§ОнФЃПщКЭFLASH ДцДЂЪ§ОнФЃПщЃЌ ДЫЪБЃЌжааФПижЦФЃПщдкЯьгІВЩМЏФЃПщЕФжаЖЯЪЙA/D ФЃПщвд16K ЕФВЩбљТЪЭљFPGA ФкВПЕФЫЋПкRAM аДЪ§ОнЃЌЭЌЪБFLASH ДцДЂФЃПщдкжааФПижЦФЃПщЯТЃЌХаЖЯВЂЭЦНјRAM ЕФЕижЗвдЖСШЁRAM ЕФ Ъ§ОнЃЌдкЪ§ОнВЛЖЯаДШыFLASH ДцДЂЦїЕФЭЌЪБХаЖЯЪ§ОнШнСПЪЧЗёДяЕНжИЖЈЕФЪ§ОнСПЃЌШчЙћУЛгаЃЌ дђЗЕЛиЕНFLASH аДзДЬЌМЬајДцДЂЪ§ОнЃЌвЛЕЉДяЕНЃЌЯЕЭГдђДЅЗЂвЛИіаХКХРДПижЦЕчдДФЃПщЙиБе ЕчдДЃЌЪЙећИіЯЕЭГЭЃжЙЙЄзїЃЌвдМѕаЁКФЕчСПЁЃЕБВхЩЯЖСЪ§ПкЪБЦєЖЏUSB дкЯпЃЌдкЩЯЮЛЛњЕФПи жЦЯТЃЌЖдFLASH ДцДЂЦїНјааЖСШЁВйзїЃЌвдБуЖдЪ§ОнНјааЪТКѓЗжЮіКЭДІРэЁЃ  НсЪјгя ИУЮЂаЭзЫЬЌДцДЂВтЪдЯЕЭГЙЄзїадФмСМКУЃЌдкХзШіЪдбщжаЕУЕНШчЭМ3 ЫљЪОЕФаХКХЃЌДяЕНСЫ РэТлвЊЧѓЃЌГЩЙІЕФЭъГЩСЫЗЩааЬхзЫЬЌВЮЪ§ЕФВЩМЏКЭДцДЂЃЌЭЈЙ§ЖрДЮЪдбщжЄУїЃЌИУЮЂаЭВтЪдЯЕ ЭГОпгавЛЖЈЕФЙЄГЬгІгУадВЂЖдЦфЫћВтЪдЩшМЦгазХживЊВЮПМвтвхЁЃ |

ЭјгбЦРТл