ИпадФмCMOSМЏГЩЕчбЙБШНЯЦїЩшМЦ

ЗЂВМЪБМфЃК2010-8-12 13:56

ЗЂВМепЃКlavida

ЙиМќДЪЃК

БШНЯЦї

|

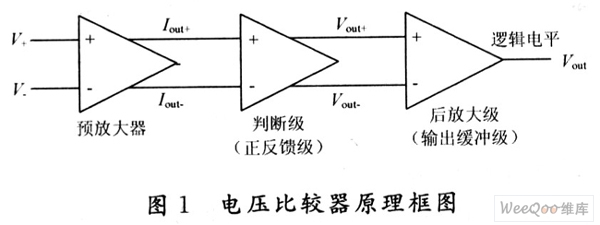

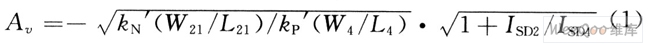

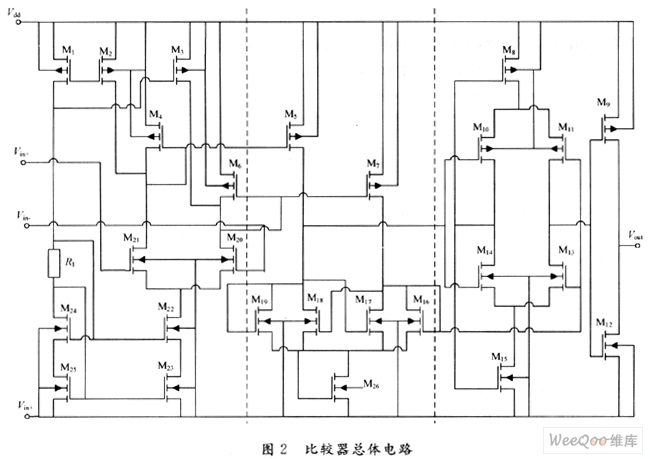

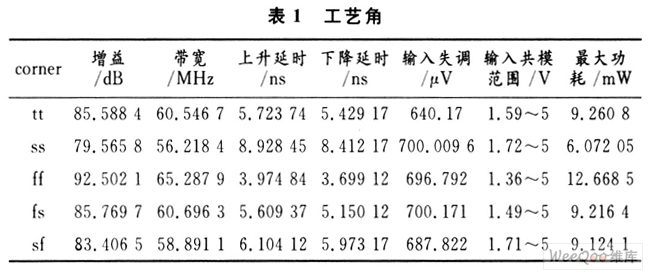

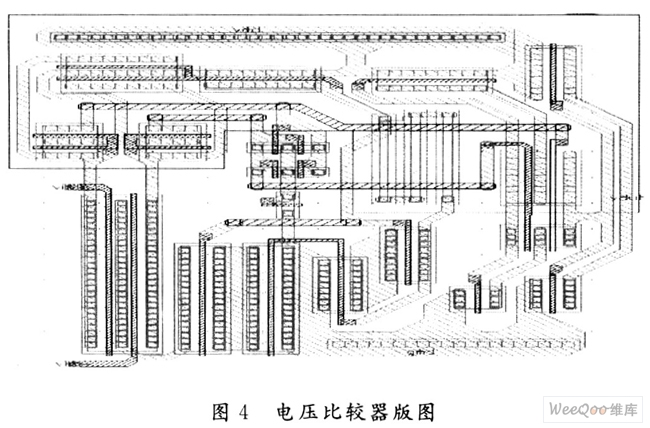

ЕчбЙБШНЯЦїЪЧЖдЪфШыаХКХНјааМјЗљгыБШНЯЕФЕчТЗЃЌЦфЙІФмЪЧБШНЯвЛИіФЃФтаХКХКЭСэвЛИіФЃФтаХКХ(ВЮПМаХКХ)ЃЌВЂвдЪфГіБШНЯЕУЕНЕФЖўНјжЦаХКХЁЃЦфдкAЃЏDзЊЛЛЦїЁЂЪ§ОнДЋЪфЦїЁЂЧаЛЛЙІТЪЕїНкЦїЕШЩшБИжагазХЙуЗКЕФгІгУЁЃдкИпЫйЖШЁЂИпОЋЖШAЃЏDзЊЛЛЦїжаЃЌБШНЯЦїЕФОЋЖШКЭЫйЖШжБНггАЯьзЊЛЛЕчТЗЕФзЊЛЛОЋЖШКЭзЊЛЛЫйЖШЕШЙиМќжИБъЃЛдкЪ§ОнДЋЪфЦїжаЃЌБШНЯЦїЕФадФмЖдЪ§ОнДЋЪфЕФЮѓТыТЪгазХКмДѓЕФгАЯьЃЛдкЧаЛЛЙІТЪЕїНкЦїжаЃЌЕїНкЦїЕФЙІТЪЕїНкадФмдкКмДѓГЬЖШЩЯвРРЕгкЕчбЙБШНЯЦїЕФадФмЁЃвђДЫЃЌЪЧИпЙЄзїЦЕТЪЁЂИпдівцЁЂЕЭЪЇЕїЕчбЙЁЂИпадФмЕФЕчбЙБШНЯЦїЃЌдкФЃФтМЏГЩЕчТЗКЭЪ§ЃЏФЃЛьКЯМЏГЩЕчТЗжаЪЎЗжживЊЁЃЗТецНсЙћБэУїЃЌИУЕчбЙБШНЯЦїЪЪгУгкИпЫйAЃЏDзЊЛЛЦїЁЂИпЫйЪ§ОнДЋЪфЦїМАИпадФмЧаЛЛЙІТЪЕїНкЦїЕШЩшБИжаЁЃ 1 БШНЯЦїЕчТЗЩшМЦ етРяНщЩмЕФЕчбЙБШНЯЦїЪЧДЋЭГЕФдЄЗХДѓЫјДцБШНЯЦїЃЌВЩгУдЄЗХДѓЦїЁЂЫјДцБШНЯЦїКЭЪфГіЛКГхМЖМЖСЊЕФЗНЪНРДЪЕЯжЃЌЦфдРэПђЭМШчЭМ1ЫљЪОЁЃ  ШчЭМ2жаЕквЛВПЗжЫљЪОЃЌM20КЭM21ЙЙГЩВюЗжЗХДѓЙмЃЛM4ЃЌM6зщГЩгадДИКдиЁЃM2ЃЌM3ЗжБ№гыM4ЃЌM6ВЂСЊЃЌвдЯђВюЗжЗХДѓЙмзЂШЫДѓЕчСїЃЌЭЌЪБвВМѕаЁСЫM4КЭM6ЕФПэГЄБШЃЌНЕЕЭСЫЕчТЗЕФЪфШыЕчШнЃЌвдРћгкЕчТЗЬсИпЦЕТЪЬиадЁЃИУЗХДѓЦїЕФдівцПЩБэЪОЮЊЃК  ДгЪН(1)ПЩвдПДГіЃЌдкЙмзгПэГЄБШШЗЖЈКѓЃЌAvгы(1+ISD2ЃЏISD4)1/2ГЩе§БШЃЌШєM2ЯђM21зЂШыДѓЕчСїЃЌдђдкБЃжЄИпЦЕЪБФмЬсИпЗХДѓЦїЕФдівцЁЃИУЗХДѓЦїЕФдівцЮЊ12ЃЎ9 dB(4ЃЎ415 7БЖ)ЃЌ3 dBДјПэЮЊ582ЃЎ64 MHzЁЃ 1ЃЎ2 ЫјДцБШНЯЕчТЗ ЫјДцБШНЯЕчТЗЪЧећИіБШНЯЦїЕФКЫаФВПЗжЃЌЫќгІФмЧјЗжКСЗќСПМЖЕФЪфШыаХКХВюЁЃШчЭМ2жаЕкЖўВПЗжЫљЪОЃЌ M17,M18НЛВцЛЅСЌЪЕЯже§ЗДРЁЃЌвдЬсИпБШНЯЕчТЗЕФдівцЁЃРћгУЧАМЖдЄЗХДѓЦїЕФЪфГіЃЌПижЦЫјДцЦїЪфШыЕчСїI+ЃЌI_ЕФБфЛЏЃЌШєI_дЖДѓгкI_ЃЌдђM16КЭ M18ЕМЭЈЃЌVout-Ёї0ЃЌUout+=(2L16I+ЃЏWІЬnCox)+VTHNЃЛШєI_діДѓЖјI+МѕаЁЃЌM18ЕФТЉвЛдДЕчбЙЩ§ИпЃЌЕБИпЕНM17ЕФ VTHNЪБЃЌM17ЕМЭЈЃЌДЫЪБM17ЙмПЊЪМГщШЁдРДСїЙ§M16ЙмЕФЕчСїЃЌетЛсЪЙM16ЙмЕФТЉвЛдДЕчбЙЯТНЕЃЌВЂЕМжТM18ЙмНижЙЃЌЕчТЗЕФЪфГізДЬЌЗЂЩњзЊЛЛЁЃЕБI-діДѓЕНвЛЖЈГЬЖШЪБЛсЕМжТM18НјШыБЅКЭЧјЃЌДЫЪБСйНчЕчСїжЕI-=(I+)(W17ІЬnCoxЃЏL17)ЃЏ(W16ІЬnCoxЃЏL16)ЃЌИУЕчСїСйНчЕувВЪЧЪфГіЕчбЙЗЂЩњзЊЛЛЕФСйНчЕуЁЃЭЌРэПЩЕУЃЌЕБI+діДѓЪБЃЌЗЂЩњзЊЛЛЕФЕчСїСйНчЕуI+=(I-)(W17ІЬnCoxЃЏL17)ЃЏ (W16ІЬCoxЃЏL16)ЁЃ  ИУЫјДцБШНЯЦїЗЂЩњзЊЛЛЪБЕФЪфШыЕчбЙВюЮЊ1ЃЎ37 mVЁЃДгЫјДцЦїЕФЫВЬЌЬиадПЩвдПДГіЃЌдкЪфШыаХКХЗЂЩњЬјБфЪБЃЌЭЈЙ§БШНЯЪфШыаХКХКЭ2ЃЎ5 VВЮПМаХКХЃЌЫјДцБШНЯЦїИјГіСНИіЯђЯрЗДЗНЯђБфЛЏЕФЪфГіаХКХЃЌЪЕЯжСЫБШНЯЙІФмЁЃ 1ЃЎ3 ЪфГіЛКГхЧ§ЖЏМЖ ЪфГіЛКГхЧ§ЖЏМЖ(гжГЦКѓЗХДѓЦї)ЕФжївЊзїгУЪЧАбЫјДцБШНЯЕчТЗЕФЪфГіаХКХзЊЛЏГЩТпМЕчЦН(0 VЛђ5 V)ЁЃШчЭМ2жаЕкШ§ВПЗжЫљЪОЃЌM8ЃЌM10ЃЌM11,M13,M14,M15зщГЩВюЗжздЦЋжУЕчТЗЃЌЫќФмЮќШЫКЭЙЉГіНЯДѓЕФЕчСїЃЌЪЙБШНЯЦїдкЧ§ЖЏДѓЕФШнадИКдиЪБЫйЖШВЛЪмАкТЪЕФЯожЦЁЃM9ЃЌM12зщГЩвЛИіЗДЯрЦїЃЌгУзїИНМгЕФдівцМЖЃЌЭЌЪБЪЕЯжИКдиЕчШнКЭздЦЋжУВюЗжЗХДѓЦїжЎМфЕФИєРыЁЃвЊЪЙЪфГіЛКГхМЖЙЄзїдкЯпадЧјЃЌЪфШыаХКХЕФЗљЖШвЛАувЊдк1ЁЋ3ЃЎ5 VжЎМфЃЌЫљвддкЕчТЗжаДЎШыM26ЙмРДЬсЩ§ЫјДцЦїЪфГіЕчбЙЕФЗљжЕЁЃ 2 ЕчТЗЗТец дк5 VЕчдДЕФЕчбЙЯТЃЌVin-ЖЫМг2ЃЎ5 VВЮПМаХКХЃЌдкCadenceШэМўЦНЬЈЯТгУSpec-treЙЄОпЖдЛљгкCSMC 0ЃЎ5 ІЬmCMOSЙЄвеФЃаЭЕФЕчТЗНјааЗТецЃЌЕУЕНБШНЯЦїЕФдівцЁЂДјПэЁЂЩЯЩ§бгЪБЁЂЯТНЕбгЪБЁЂЪфШыЙВФЃЗЖЮЇШчЭМ3ЫљЪОЁЃ  гУCadenceздДјЕФDraculaЙЄОпЖдАцЭМНјаабщжЄЃЌЭЈЙ§ЩшМЦЙцдђМьВщ(DRC)ЃЌИУАцЭМЗћКЯCSMC0ЃЎ5ІЬmCMOSЙЄвеЕФЯрЙиЩшМЦЙцдђЁЃЭЈЙ§ЕчТЗЭМКЭАцЭМЕФЖдее(LVS)ЃЌАцЭМжаЕФЦїМўМАЦїМўМфЕФСЌНгЧщПігыЕчТЗЭМжаЯрвЛжТЃЌБЃжЄСЫИУАцЭМЪЧЭМ2ЫљЪОЕчТЗЭМЕФЮяРэбкФЃЭМаЮМЏЁЃДЫЭтЃЌдкзіЭъDRCКЭ LVSКѓЃЌАцЭМЕФЕчЦјЙцдђМьВщ(ERC)вВЭЌЪБЭъГЩСЫЃЌетЪЧDraculaЙЄОпЕФвЛИіжївЊЬиЕуЁЃERCБЈИцЯдЪОИУАцЭМжаЮоЖЬТЗЁЂЖЯТЗЕШЕчЦјЙцдђДэЮѓЁЃ  4 Нс гя дкCSMC OЃЎ5ІЬm CMOSЙЄвеЬѕМўЯТЃЌВЩгУдЄЗХДѓЦїЁЂЫјДцБШНЯЕчТЗКЭЪфГіЛКГхМЖМЖСЊЕФЫјДцБШНЯЕчТЗНсЙЙЃЌЩшМЦСЫвЛИіИпЫйЁЂИпОЋЖШЕФИпадФмМЏГЩЕчбЙБШНЯЦїЃЌЫќОпгаЕЭЪфШыЪЇЕїЕчбЙЁЂЕЭЙІКФЕФЬиЕуЁЃЭъГЩДгЕчТЗдРэЭМЩшМЦЕНАцЭМЩшМЦКЭбщжЄ(DRCЃЌLVS)вдМАЙЄвеНЧЗТецКЭЗжЮіЕФећИіЩшМЦСїГЬЁЃДгЗТецНсЙћПЩвдПДГіЃЌетвЛИпадФмЕчбЙБШНЯЦїЪЪгУгкИпЫйAЃЏDзЊЛЛЦїЁЂИпЫйЪ§ОнДЋЪфЦїМАИпадФмЧаЛЛЙІТЪЕїНкЦїЕШЩшБИжаЁЃ3 АцЭМЩшМЦ МЏГЩЕчТЗЕФАцЭМЪЧаОЦЌдкЪЕМЪжЦзїЪБЮяРэбкФЃЭМаЮЕФМЏКЯЃЌЪЧДгЕчТЗдРэЭМЕНЪЕМЪаОЦЌЕФЙиМќЙ§ЖЩЛЗНкЁЃАцЭМЕФЩшМЦжБНггАЯьзХаОЦЌЕФзюжеадФмЁЃФЃФтМЏГЩЕчТЗАцЭМЕФЩшМЦвЊЧѓИќИпЃЌЫќВЛНігаММЪѕГЩЗжЃЌЛЙашвЊаэЖрвеЪѕадЕФВМОжКЭзпЯпЁЃ  ЛљгкCSMC 0ЃЎ5ІЬm CMOS(N-WellЙшеЄ)ЙЄвеЩшМЦЕФМЏГЩЕчбЙБШНЯЦїАцЭМШчЭМ4ЫљЪОЁЃЦфжаЕчзшЮЊжЦзїдкN-wellжаЕФP+РЉЩЂЬѕЃЛMOSЙмЮЊNORMALЦїМўЃЌЦфЙЕЕРПэГЄЮЊЖрОЇЙшеЄИВИЧгадДЧјВПЗжЕФПэГЄЁЃАќЮЇгадДЧјЕФN+diffКЭP+diffЃЌгУРДБэУїЙмзгЪЧNMOSЙмЃЌЛЙЪЧPMOSЙмЃЌАцЭМУцЛ§ЮЊ57ІЬmЁС69 ІЬmЁЃ |

ЭјгбЦРТл