一种支持ISP的Flash在嵌入式设计中的应用

发布时间:2010-8-12 13:52

发布者:lavida

|

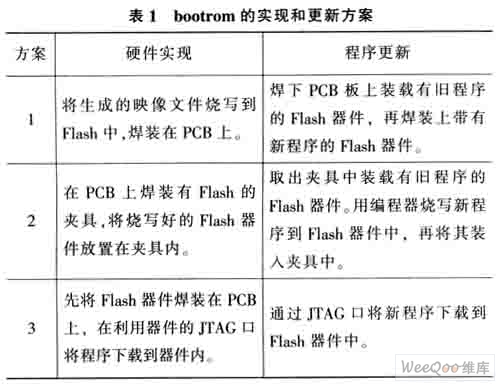

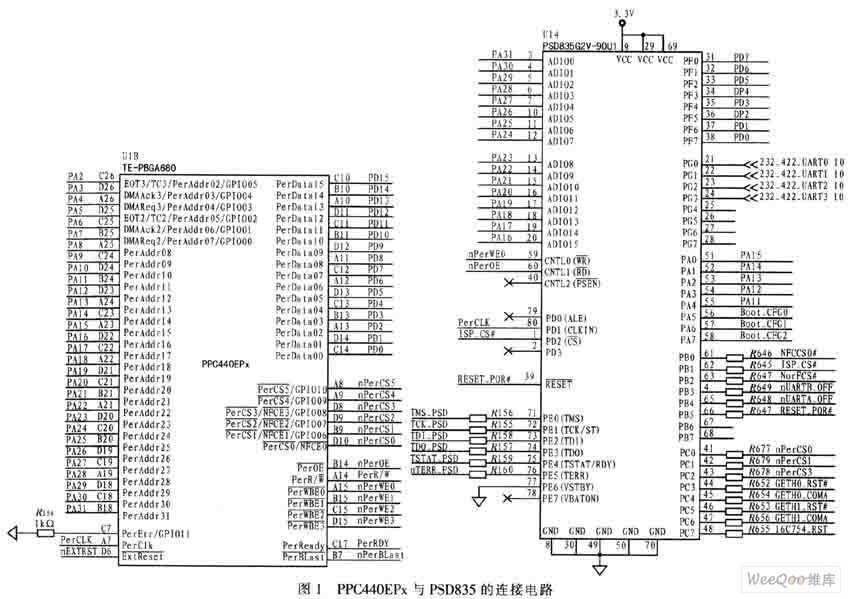

1 引言 在基于VxWorks的嵌入式系统开发过程中,板卡支持包BSP(Board Support Package)的开发是非常重要而又闲难的一个环节。因为不能确定硬件系统是否正常丁作,而后续应用开发都是以此为基础。 在实际开发中,为了提高开发效率,大多是采用以一个与目标板硬件相似的BSP为模板,并在此基础上修改移植。在这个过程中.除了CPU以外,另一个重要的器件就是装有启动程序的Flash器件。 2 系统介绍 采用高性能PowerPC系列器件PPC440EPx为核心设计的一款符合CPCI标准的嵌入式单板计算机系统。 该系统集成了丰富的外设接口和调试接口,可用于设备控制、设备管理、通信设备中的通信控制、协议处理、路由处理和网关处理等。其主要是面向航空设备和军用车载设备的应用。 在调试阶段,系统的启动是通过执行Boot flash中存储的bootrom映像文件完成的。Boot Flash器件采用ST公司的PSD835,通过EBC总线与PPC440EPx相连。EBC总线是PPC440EPx的并行总线。其可以与8位,16位或32位的外部设备通信,最多可支持6个不同时序要求的设备。其中,片选0分配给Boot Flash。上电时,PowerPC会自动访问BootFlash,进行系统初始化。操作系统是VxWorks,其映像文件放在NAND Flash中。 3 软件开发流程 软件系统的开发流程是:首先设计bootrom映像文件,并将其烧写到Flash器件中(该器件称为Boot ROM)。上电后,bootrom程序进行相应初始化后与Host主机通信,将操作系统映像文件下载到嵌入式系统平台的RAM中运行。如果程序不正确或需更新,则重新通过bootrom程序将新的映像文件下载到RAM中。 当所有程序都调试成功,整个系统作为产品发布。此时,则需将操作系统和应用程序映像文件烧写到在大容量的flash器件中(如NAND Flash),系统自动将从Flash中复制到RAM中执行。 4 bootrom设计方案的选择 bootrom应是一个短小精悍的程序,可初始化系统工作和通信接口(通常是串行接口和以太网接口);系统作为产品发布无需bootrom程序;调试 bootrom时,需频繁地将修改后的映像文件烧写到Boot ROM中。实现该Boot ROM电路有多种方案,如表1所示.  方案1是传统设计方案,成本低,可选择的Flash器件多。但在调试bootrom时,更新程序非常不方便。需要焊装Flash器件,很容易导致器件和 PCB板的物理损坏,而且效率非常低;而方案2从逻辑电路上来看,与方案1是一样的。但其由于其使用夹具,器件装卸简单,程序更新比方案1方便。但夹具成本较高,可靠性差,并且一般夹具体积较大,这就增加了PCB的布局、布线难度。上述两种方案,Flash的编程都需从PCB上取下,用编程器烧写。显然,这样的工作效率较低。方案3则采用支持ISP功能的Flash器件来实现Boot ROM,这就使得程序更新变得非常方便,极大提高工作效率。因此,根据嵌入式开发实际情况,为节约成本、提高工作效率,该系统设计选择方案3。考虑到 bootrom映像文件一般较小,选用ST公司的512 KB的Flash器件PSD835。 5 PSD835在嵌入式系统中的应用 5.1 硬件电路设计 该系统使用PSD835的主Flash作为Boot ROM。同时,还使用该器件的PLD资源实现一些控制和初始化配置功能。如图1所示,PSD835的存储器通过其CPU接口与PPC440EPx的外部总线接口(EBC)相连。  连接电路比较简单,只需将EBC的片选信号、读信号、地址和数据信号分别与PSD835的对应引脚相连即可。其他引脚被该器件的PLD使用,主要完成串口工作模式、PPC440EPx启动方式、片选信号的设置,以及网络控制信号的产生等功能。 在设计实际硬件电路时,应注意以下几点: (1)因为最终产品要通过NAND Flash启动,因此片选0可通过拨码开关或CPLD分别在PSD835和NAND flash的片选信号之间切换。PPC440EPx有8个bootstrap选项(设置CPU的时钟、启动、寄存器的初始值等),可以使用CPLD进行改变; (2)PPC440EPx的EBC总线无复用地址和数据信号。因此,数据总线与F端口相连。低16位的地址总线与PSD835的ADIO15~AD100相连,高位地址与A端口相连; (3)PPC440EPx的EBC的数据总线的最高位是Data0,地址总线的最高位是Addr2。连接时,注意不要将顺序接反; (4)为了提高编程速度,添加了2个JTAG信号:TERR和TSTAT。 5.2 PSD835的功能和编程设计 PSD835的Flash编程和PLD逻辑功能的实现,需要使用FlashLINK下载线(硬件)和PSDsoft EXPRESS(软件)。FlashLINK其实就是一个JTAG和并口的转换器;PSDsoftEXPRESS是PSD系列器件的设计软件。利用该工具软件定义器件的引脚功能、映射存储器、配置PLD等。所有的定义和配置与程序固件一起生成obj文件。该文件通过FlashLINK下载到PSD器件中。另外,利用该工具软件还可以完成擦除、校验、上载、空白检查等功能。而整个设计过程也非常简单,只需根据其设计流程简单点击鼠标即可完成PSD设计。图2 为PSD设计流程。  根据该系统设计简单描述如下:首先建立一个丁程文件。然后根据实际电路在下拉框中选择厂家和CPU型号,以及将用到的控制信号,再选择使用的PSD器件型号和封装。最后定义CPU和PSD连接的方式(即8位或16位总线模式,复用或非复用总线等等)。 该系统使用AMCC公司的PPC440EPx型CPU,下拉框中无该选项。这时可选择other,控制信号根据EBC总线的定义选择RD和WR。PSD与CPU数据总线为8位,地址和数据无复用,未使用ALE信号。 在设计阶段所做的设置较多,首先,定义电路中所使用的引脚。定义其名字、引脚是CPLD的输入还是输出,或是CPU的I/O;同时还要配置该引脚是组合逻辑还是时序逻辑;定义页寄存器的使用。系统中EBC的地址信号线足够多,因此将页寄存器作为PLD的输入信号;定义PSD器件内部存储器、寄存器的地址映射以及片选信号的逻辑表达式。因为本系统使用512 KB的主Flash存放启动代码,因此,其地址空间被定义在0xFFF80000~0xFFFFFFFF(BSP中定义)。实际电路设计时,为了简化设计,只使用20根地址信号线。因此,将主Flash地址定义在0x80000~0xFFFFF。则片选fs0在0x80000~0x8FFFF,则片选 fs1在0x90000~0x9FFFF。以此类推片选fs2~fs7的地址空间。其他的存储空间可分配在0x00000~0x7FFFF。片选信号的逻辑表达式为将EBC总线片选0取反;定义输出信号以及内部节点信号的逻辑。这实际上就是完成CPLD功能的设计。 附加定义中可设置安全位、用户代码、设置页保护。如果设置安全位,所有编程工具将不能访问PSD的内容。用户代码用于版本管理。对于具有保护功能的页, CPU就只能对其进行读操作(通过JTAG口或编程器改变其内容)。适配是检查器件是否能满足上述的各种配置,同时产生相应的报告文件。启动代码 bootrom.hex文件和上述的各种配置融合为一个.obj文件。设计中需要注意:bootrom映像文件不能太大(不能超过512 KB);主Flash的8个页都要指向同一个映像文件;映像文件的名字bootrom.hex最好改为不是以hex为后缀(如改为bootrom.a),否则会出错。将生成的.obj文件烧写到器件内部。正确完成上述流程就可调试程序。 6 结论 从PSD835的数据手册可知,该器件主要是应用于16位的单片机系统。该系统设计根据嵌入式系统中 BSP开发以及PSD835器件的特点,将该器件灵活运用于基于32位RISC器件PPC440EPx的嵌入式系统中,降低BSP的开发难度,提高工作效率。以此为基础实现的CPCI单板计算机已成功应用于某航载数据采集分析记录仪。 |

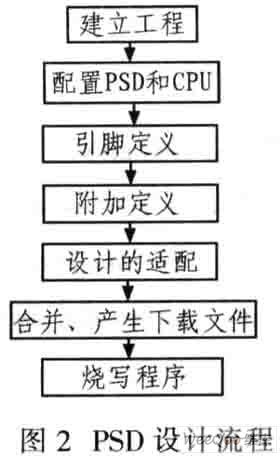

网友评论