LMSздЪЪгІТЫВЈЦїдкМЄВЈБЈАаЯЕЭГжаЕФгІгУ

ЗЂВМЪБМфЃК2010-8-10 15:58

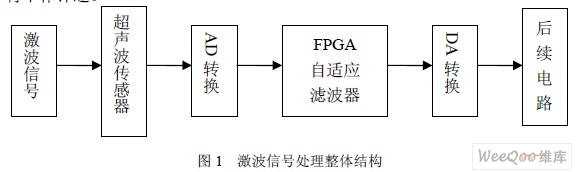

ЗЂВМепЃКlavida

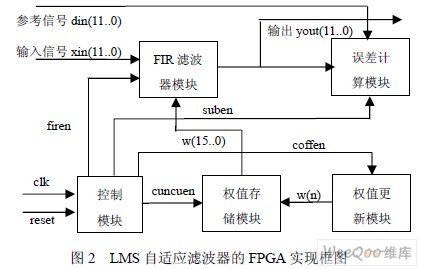

|

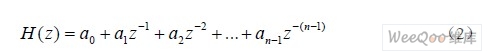

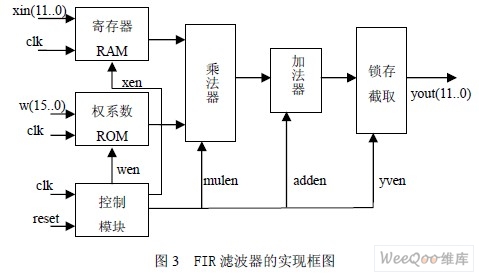

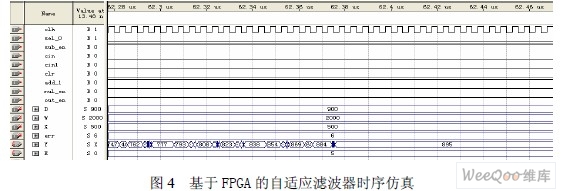

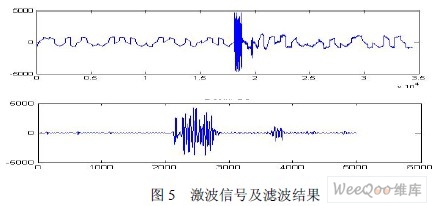

еЊвЊЃКдквАЭтИДдгбЕСЗЛЗОГЯТЃЌРћгУМЄВЈдРэНјааЪЕЕЏЩфЛїЕФОЋЖШзјБъБЈАаЃЌЪЧвЛЯюОпгаЯрЕБЬєеНадЕФММЪѕЁЃБОЮФВЩгУFPGAЃЈЯжГЁПЩБрГЬУХеѓСаЃЉНсКЯздЪЪгІТЫВЈММЪѕЃЌЖдБЈАаЯЕЭГВЩМЏЕФМЄВЈаХКХНјааСЫЪЕЪБТЫВЈДІРэЁЃВЩгУ VHDLгябдБрГЬЃЌРћгУ QUARTUS II6.0НјааСЫЗТецЁЃЪЕбщНсЙћжЄУїЃЌЕБЕЏЭшДЉЙ§АаЦНУцЪБЃЌЪ§ОнВЩМЏЕчТЗВЩМЏЕФМЄВЈаХКХКЌгаДѓСПдыЩљЃЌЛљгк FPGAЕФздЪЪгІТЫВЈЦїФмКмКУЕиТЫГ§СЫДѓВПЗжИЩШХдыЩљЃЌЕУЕНСЫБШНЯРэЯыЕФМЄВЈЪ§ОнЃЌЬсИпСЫБЈАаЯЕЭГЕФБЈАаОЋЖШЁЃ 0 ЧАбд гЩПеЦјЖЏСІбЇдРэЃЌЕБГЌвєЫйдЫЖЏЕФЮяЬхЃЌгЩгкдЫЖЏЫйЖШДѓгкОжВПЩљЫйЪБЛсВњЩњМЄВЈЃЌЕЏЕРЩљВЈЪЧГЌЩљЫйЕЏЭшЗЩааЪБГхЛїПеЦјЗжзгЫљаЮГЩЕФМЄВЈЃЈ Shock wavesЃЉЁЃВЩгУМЄВЈдРэНјааБЈАаЪЧвЛЯюОпгаЬєеНадЕФММЪѕЃЌЫќРћгУМЄВЈаХКХНјааГЌвєЫйЗЩааЬхЬНВтЃЌЪЧвЛжжаТЕФФПБъЬНВтЗНЗЈЁЃБОЮФбаОПЖдЯѓЮЊвЦЖЏАаГЕЃЌИУвЃПиздЖЏзАжУздДјЕчдДКЭЖЏСІзАжУЃЌФмдк 25Km/hФкЮоМЖЕїЫйЃЌЕЋЪЧЃЌгЩгкЦфЙЄзїЛЗОГБШНЯЖёСгЃЌздЩэеёЖЏЁЂЗчДЕЁЂЗЂЕчЛњКЭЕчЖЏЛњЕФОоДѓИЩШХЃЌбЯжигАЯьСЫздЖЏБЈАаЯЕЭГЕФБЈАаОЋЖШЁЃЮЊСЫЪЪгІЯжДњЛЏ*бЕСЗЕФашвЊЃЌБОЮФВЩгУ FPGAКЭздЪЪгІТЫВЈММЪѕЃЌРћгУгВМўЕчТЗРДЪЕЯж LMSздЪЪгІТЫВЈЦїЃЌЭъГЩЖдЧПБГОАдыЩљЛЗОГЯТМЄВЈаХКХЕФТЫВЈЃЌдкТњзуЪЕЪБЪ§ОнДІРэЧАЬсЯТЃЌвдЬсИпБЈАаЯЕЭГЕФБЈАаОЋЖШЁЃ 1 ЮЪЬтЕФЬсГіМАЗНАИбЁШЁ БОЩшМЦЦ№ГѕЩшМЦЕчТЗВЩгУЕФФЃФтИпЭЈТЫЦїЃЌКѓРДгжЩшМЦГЩДјЭЈТЫВЈЦїЃЌШЛЖјЭЈЙ§ЪЕМљЗЂЯжЃЌЦфТЫВЈаЇЙћЖМБШНЯВюЃЌФбвдТњзуЯЕЭГОЋЖШЕФвЊЧѓЃЛВЩгУЭЈгУ DSPЪ§зжаХКХДІРэЦїМўгУШэМўЩшМЦЪ§зжТЫВЈЦїЃЌЦфЪ§ОнЭЬЭТТЪЁЂДІРэЫйЖШКЭЪЕЪБаддЖВЛШчЛљгк FPGAгВМўЪЕЯжЕФЪ§зжТЫВЈЦїЃЌвђЮЊЃЌЛљгк FPGAЕФЪ§зжТЫЦїДњБэСЫЮДРДЪ§зжаХКХДІРэЕФЗЂеЙЗНЯђЃЌгУЛЇПЩвдКмЗНБуЕФНсКЯЪЕМЪашвЊЩшМЦГіздМКЕФПЩБрГЬЪ§зжаХКХДІРэаОЦЌЃЌЯждквбОНЯЮЊЙуЗКЕигІгУдкИпЖЫЪ§зжаХКХДІРэСьгђЁЃ здЪЪгІТЫВЈЦїЕФГЃгУЪЕЯжаЮЪНга FIRКЭIIRСНжжЃЌЖј FIRТЫВЈЦїЪЧЪЕМЪгІгУНЯЮЊЙуЗКЕФвЛжжЃЌFIRТЫВЈЦїжЛгаПЩЕїЕФСуЕуЃЌвђДЫЫќУЛга IIRвђМцгаПЩЕїЕФСуЕуКЭМЋЕуЖјДјРДЕФВЛЮШЖЈЮЪЬтЃЌДЫЭтЃЌLMSМЦЫуСПаЁЃЌвзгкгВМўЪЕЯжЃЌЙЪБОЮФВЩгУЕФТЫВЈЦїЪЧЛљгкFIRЛљДЁжЎЩЯЙЙНЈЕФ LMSздЪЪгІТЫВЈЦїЁЃ 2 ЯЕЭГЩшМЦНсЙЙ БОЮФЫљЩцМАЕФМЄВЈаХКХДІРэВПЗжЕФећЬхНсЙЙПђЭМШчЭМ 1ЫљЪОЃЌгЩаХКХВЩМЏДЋИаЦїЁЂФЃЪ§зЊЛЛЦїМўЁЂFPGAЦїМўЁЂЪ§ФЃзЊЛЛЦїМўЙЙГЩЁЃИпЫйЫВЬЌЕФМЄВЈаХКХБЛГЌЩљВЈДЋИаЦїВЖЛёвдКѓЃЌОЙ§ЪЪЕБЕїРэЫЭЕН ADзЊЛЛЦїМўЃЌБОЩшМЦВЩгУ MAX197ADзЊЛЛЦїМўЃЌгЩ FPGAЩшМЦЕФзДЬЌЛњЖдЦфПижЦЃЌНјаа ADзЊЛЛЃЌШЛКѓдйНјШыЛљгк FPGAЩшМЦЕФздЪЪгІТЫВЈЦїжаТЫВЈЃЌзюКѓдйНјаа DAзЊЛЛДЋЪфЕНКѓајДІРэЕчТЗЃЌгЩгкБОЩшМЦЕФжївЊШЮЮёЪЧЩшМЦЛљгк LMSЫуЗЈЕФздЪЪгІТЫВЈЦїЃЌЦфЫќВПЗжНЋВЛзїЯъЪіЁЃ  3 LMSздЪЪгІТЫВЈЦїЩшМЦ LMSЫуЗЈЪЧвдЦкЭћЯьгІКЭТЫВЈЦїЪфГіаХКХжЎМфЕФОљЗНжЕЮЊзМдђЃЌвРОнЪфШыаХКХдкЕќДњЙ§ГЬжаЙРМЦЬнЖШЪИСПЃЌВЂИќаТШЈжЕЯЕЪ§вдДяЕНзюгааЇЕФвЛжжздЪЪгІЕќДњЫуЗЈЃЌЫќдкгХЛЏЗНЗЈжаВЩгУСЫЛљгкЫцЛњЬнЖШЕФзюЫйЯТНЕЗЈЁЃИљОн LMSЫуЗЈЕФЪЕЯжЙ§ГЬЃЌдк FPGAЪЕЯжЪБЃЌПЩвдЗжЮЊжївЊЕФМИИіФЃПщЃКFIRТЫВЈЦїФЃПщЁЂЮѓВюМЦЫуФЃПщЁЂШЈжЕДцДЂФЃПщЁЂШЈжЕИќаТФЃПщвдМАПижЦФЃПщЁЃЦфФЃПщПђЭМШчЭМ 2ЫљЪОЁЃЩшМЦжаВЩгУ VHDLгябдЩшМЦЃЌИљОн MAX197ЕФзЊЛЛвЊЧѓЃЌЦфЪфГіЮЊ 12ЮЛПэЖШЕФЪ§зжаХКХЃЌвђДЫЃЌДЫДІВЩгУ 12ЮЛВЂааЪ§ОнЪфШыЃЌ12ВЂааЪ§ОнЪфГіЃЌШЈжЕЯЕЪ§ЕФЪ§ОнПэЖШЮЊ 16ЮЛЃЌresetЮЊЯЕЭГИДЮЛЃЌИпЕчЦНгааЇЃЌclkЮЊЯЕЭГЪБжгЃЌfirenЮЊ FIRТЫВЈЦїЪЙФмЃЌsubenЮЊЮѓВюМЦЫуФЃПщЪЙФмЃЌcuncuenЮЊШЈжЕДцДЂФЃПщЪЙФмЃЌcoffenЮЊШЈжЕИќаТФЃПщЪЙФмЃЌЖМЮЊИпЕчЦНгааЇЁЃ  4 здЪЪгІТЫВЈЦїЕФ FPGAЪЕЯж 4.1 NНз FIRТЫВЈЦїФЃПщЕФЩшМЦ FIR ТЫВЈЦїЪЧЪ§зжТЫВЈЦїЕФвЛжжЃЌЫќЕФЪфГіПЩвдгУВюЗжЗНГЬБэЪОШчЯТЃК  ЦфжаЃКN ЪЧFIR ТЫВЈЦїЕФГщЭЗЪ§ЃЌx(i)БэЪОЕкi ЪБПЬЕФЪфШыбљБОЃЌh(i)ЪЧFIR ТЫВЈЦїЕФЕкi МЖГщЭЗЯЕЪ§ЁЃFIR ТЫВЈЦїЕФЕЅЮЛТіГхЯьгІh(n)ЪЧвЛИігаЯоГЄађСаЃЌЦфЯЕЭГКЏЪ§ПЩБэЪОЮЊЃК  дкЩшМЦжаЃЌЮЊСЫНкЪЁ FPGAЕФФкВПзЪдДЃЌЬсИпРћгУаЇТЪЃЌДЫДІВЩгУДЎааГЫМгЕФЗНЗЈЪЕЯжЁЃ FIRТЫВЈЦїФЃПщЪЕЯж 16НзЕФ FIRТЫВЈЃЌЪфШыСПжївЊАќРЈ ADзЊЛЛКѓЕФМЄВЈаХКХЪ§ОнЕФЪфШыКЭШЈжЕЯЕЪ§ЕФЪфШыЃЌxinЪЧ ADзЊЛЛКѓЕФЪфГіаХКХЃЌЮЊ 12ЮЛзжПэЃЌЦфжа 1ЮЛЗћКХЮЛЃЌ10ЮЛОЋЖШЮЛЃЌНЋДЫаХКХДцДЂдкЩюЖШЮЊ NЕФ RAMжазїЮЊ 16Нз FIRТЫВЈЦїЕФЪфШыЃЛFIRЕФШЈЯЕЪ§ winДцДЂдкСэЭтвЛИі RAMжаЃЌзжПэ 16ЮЛЃЌЦфжазюИпЮЛЮЊЗћКХЮЛЁЃЭЈЙ§ПижЦФЃПщЪфГіЕижЗаХКХПижЦЖСИїИіДцДЂФЃПщЕФЖСаДЖЏзїЃЌДЫДІЕФГЫЗЈЦїЮЊ 28ЮЛгаЗћКХЪ§ЕФГЫЗЈЦїЃЌМгЗЈЦїЭъГЩРлМгШЮЮёЃЌЕБ 16НзГЫЗЈвдМАРлМгдЫЫузіЭъКѓЃЌгЩПижЦФЃПщЪфГі youtenаХКХЃЌЖдЫјДцЕФЪ§ОнНјаагааЇНиШЁЃЌШЛКѓЪфГіЁЃЦфЪЕЯжЕФПђЭМШчЭМ 3ЫљЪОЁЃдкИУЩшМЦжаЃЌВЩгУ VHDLгябдБрГЬЭъГЩЃЌЩњГЩЖдгІЕФЖЅВудРэЗћКХЃЌШЛКѓАДЩшМЦЗНАИАбЫќУЧСЌНгГЩЖЅВудРэЭМЁЃ  4.2ПижЦФЃПщБОФЃПщжївЊЪЧПижЦДгМЄВЈЪ§ОнЪфШыФЃПщКЭШЈЯЕЪ§ЪфШыФЃПщЖСШЁЪ§ОнЪфШыаХКХКЭШЈЯЕЪ§ЕНГЫЗЈЦїЕФЪфШыЖЫЃЌЭЌЪБЛЙПижЦРлМгЦїЭъГЩРлМгШЮЮёЃЌШЛКѓВњЩњвЛИіЪЙФмаХКХЃЌЖдЪфГіЪ§ОнНјааНиШЁВйзїЃЌШЛКѓЪфГіЕНЯТвЛМЖФЃПщжаЁЃБОФЃПщЮЊећИіЯЕЭГЕФКЫаФВПЗжЃЌЫќжївЊЭъГЩЃКГѕЪМЛЏИїИіФЃПщЃЛИљОнЯЕЭГЪБжгВњЩњИїИіФЃПщЕФПижЦаХКХЃЌПижЦУПИіЕЅдЊЭъГЩЬиЖЈЕФЙЄзїЃЛВЩгУећЬхСїЫЎЯпКЭОжВПСїЫЎЯпЕФЗНЪНЃЌаЕїИїИіФЃПщЙЄзїЃЌДгЖјЬсИпећИіТЫВЈЯЕЭГЕФећЬхадФмЁЃ 4.3МЦЫуФЃПщ БОФЃПщАќРЈЃКЮѓВюМЦЫуФЃПщКЭШЈжЕМЦЫуФЃПщЁЃЮѓВюФЃПщЪЕМЪОЭЪЧвЛИіМѕЗЈЦїЃЌжївЊМЦЫу FIRТЫВЈЦїЪфГіКЭЦкЭћжЕжЎМфЕФЮѓВюЃЌШЛКѓЃЌдкПижЦФЃПщЕФзїгУЯТЃЌЕБЮѓВюТњзуЩшМЦвЊЧѓЪБЃЌБуЪЙФмЦфЪфГіЃЌЕУЕНзюжеЕФЪфГіНсЙћЁЃдкШЈжЕМЦЫуФЃПщжаЃЌзлКЯПМТЧЪеСВадКЭЩшМЦЪЕЯжЃЌЩшЖЈ u=1/4092ЃЌМД u=10HЃЌетбљжЛашЖдЮѓВюМЦЫуФЃПщЕФЮѓВюЪфГіНјаавЦЮЛдЫЫуМДПЩЪЕЯжЃЌЪЁЕєСЫГЫЗЈЦїЕФЪЙгУЃЌНкЪЁСЫ FPGAзЪдДЃЌЬсИпСЫМЦЫуЫйЖШЃЌСэЭтЃЌдкМЦЫу 2ue(k)x(k)ЪБЃЌПЩвддк e(k)гы x(k)ЯрГЫКѓжБНггввЦ 12ЮЛЃЌМДПЩЕУГіШЈжЕБфСПЁЃ 5 здЪЪгІТЫВЈЦїЕФЗТецгыаЃбщ дк Quartus II6.0злКЯЛЗОГЯТЃЌЪзЯШЖдЪфШыЩшМЦЮФМўЃЈ .vhdЁЂ.bdfЃЉНјааБрвыЃЈАќРЈНЈПтЁЂТпМзлКЯЁЂЦїМўЪЪХфЁЂЗТецЪ§ОнНиШЁЕШЃЉЃЌЯЕЭГздЖЏБрвыЭъГЩКѓздЖЏЩњГЩ .pofЮФМўЃЌШЛКѓЭЈЙ§ JTAGЯТдиЕчРТАб .pofЮФМўЯТдиЕН FPGAЦїМўжаМДПЩЁЃБОЩшМЦбЁгУ CycloneIIЯЕСаЕФ EP2C8Q208C8аОЦЌЃЌЯЕЭГЪБжгЮЊ 20MHzЃЌЪфШыаХКХЁЂВЮПМЪфШыКЭТЫВЈЦїЪфГіЖМЪЧ 12ЮЛЃЌПМТЧЕН FPGAЛЙвЊЪЕЯжЦфЫќЙІФмЃЌвђДЫдкНјааЯЕЭГЕФаОЦЌбЁаЭЪБЃЌСєгаНЯДѓЕФШпгрСПЁЃЪЕбщЪБЃЌЕїЪдЕчТЗАхДгМЦЫуЛњжаЖСШЁЪфШыЪ§ОнЕН FPGAжаЃЌШЛКѓОЙ§ FPGAДІРэКѓЃЌНЋДІРэЕФЪ§ОнЫЭЛиМЦЫуЛњжаЁЃ ЗТецЪБЃЌЩшЦкЭћаХКХЮЊ 900ЃЌЪфШыаХКХЮЊ 500ЃЌЪЕМЪЪфГіЮЊ 895ЃЌЮѓВюЮЊ 5ЃЌдк 63.2usДІЪеСВЕНЮШЖЈзДЬЌЁЃЦфЪБађЗТецВЈаЮШчЭМ 4ЫљЪОЁЃ  гУLabVIEWБраДЕФЩЯВуШэМўВЩМЏМЄВЈЪ§ОнЃЌвдtxtЮФМўИёЪНБЃДцЁЃгІгУMATLABЕФloadУќСюЃЌЛцжЦГіЭМ 5ЩЯАыВПЗжЕФМЄВЈаХКХЃЌОнЭМУїЯдПДГіЃЌЕЏЭшДЉЙ§АаЦНУцЪБЕФМЄВЈЛьдггаДѓСПИпЕЭЦЕИЩШХЁЃЮЊСЫбщжЄЩЯЪіздЪЪгІТЫВЈЦїЕФТЫВЈФмСІЃЌдкНјааЪЕбщЪБЃЌНЋДЫЪ§ОнЫЭШыЕНFPGAжаНјааДІРэЃЌдйЫЭЛиЕНМЦЫуЛњжаЃЌдЫгУЛцЭМШэМўЛцжЦЦфТЫВЈНсЙћЃЌЦфТЫВЈНсЙћМћЭМ5ЁЃ  ДгЩЯЭМПЩвдПДГіЃЌдкЧПдыЩљИЩШХЯТЃЌКмФбЗжБцГіецЪЕгааЇЕФгагУаХКХЃЌВЩгУ LMSздЪЪгІТЫВЈЦїНјааТЫВЈКѓ,ФмЙЛецЪЕгааЇЕиТЫГ§ИЩШХдыЩљЁЃ 6 НсЪјгя БОЮФРћгУ FPGAЦїМўЪЕЯжСЫЛљгк LMSздЪЪгІ FIRТЫВЈЦїЃЌгЩЩЯЪіЪЕбщНсЙћПЩвдПДГіЃЌЛљгк FPGAЪЕЯжЕФздЪЪгІТЫВЈЦїЃЌФмЙЛЪЕЪБгааЇЕиТЫçºдгдкМЄВЈаХКХжаЕФдыЩљЃЌФмЙЛзМШЗВЖзНЕНецЪЕЕФМЄВЈаХКХЃЌЮЊКѓајВПЗжДІРэЕьЖЈСЫМсЪЕЕФЛљДЁЃЌДгЖјЮЊЬсИпздЖЏБЈАаЯЕЭГЕФБЈАаОЋЖШЕьЖЈСЫМсЪЕЛљДЁЁЃ БОЮФзїепДДаТЕуЃКНЋЯШНјЕФ FPGAММЪѕКЭздЪЪгІТЫВЈММЪѕгІгУгкздЖЏБЈАажаЃЌЪЕЯжСЫЛљгк FPGAЕФздЪЪгІТЫВЈЦїЃЌЖдећИіМЄВЈаХКХДІРэЯЕЭГНјааСЫжиДѓИФНјЃЌЬсИпСЫвЦЖЏБЈАаЯЕЭГЕФБЈАаОЋЖШЁЃ |

ЭјгбЦРТл