ЛљгкFPGAЕФВННјЕчЛњМгМѕЫйПижЦЦїЕФЩшМЦ

ЗЂВМЪБМфЃК2010-8-10 14:38

ЗЂВМепЃКlavida

|

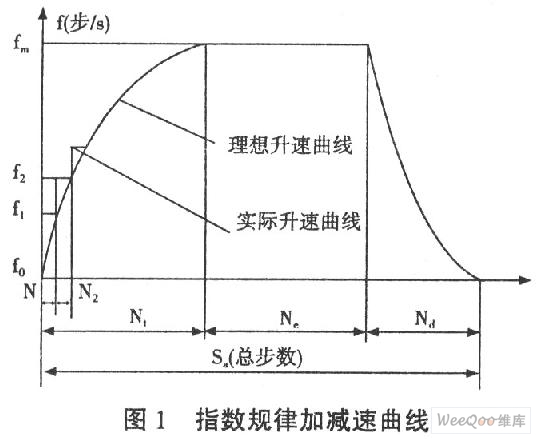

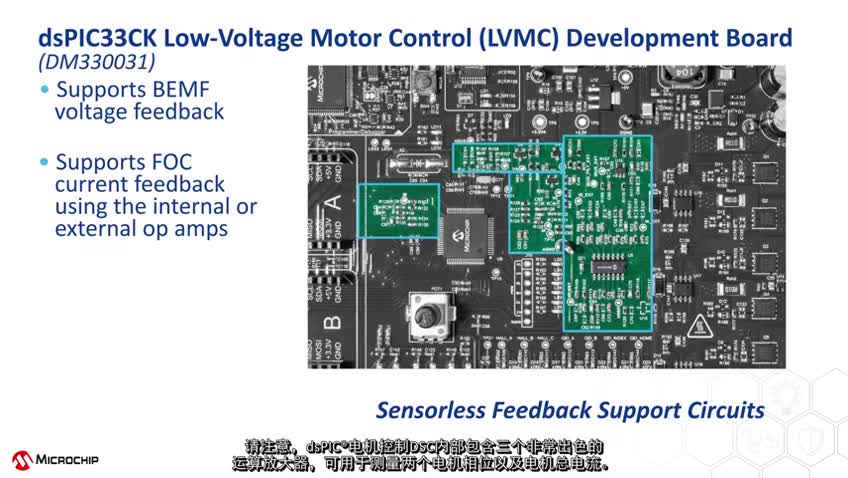

0 в§бд МИЪЎФъРДЃЌЪ§зжММЪѕЁЂМЦЫуЛњММЪѕКЭгРДХВФСЯЕФбИЫйЗЂеЙЃЌЮЊВННјЕчЛњЕФгІгУПЊБйСЫЙуРЋЕФЧАОАЁЃгЩВННјЕчЛњгыЧ§ЖЏЕчТЗзщГЩЕФПЊЛЗЪ§ПиЯЕЭГЃЌМШЗЧГЃМђЕЅЁЂСЎМлЃЌгжЗЧГЃПЩППЁЃДЫЭтЃЌВННјЕчЛњЛЙЙуЗКгІгУгкжюШчДђгЁЛњЁЂЕёПЬЛњЁЂЛцЭМвЧЁЂахЛЈЛњМАздЖЏЛЏвЧБэЕШЁЃе§вђЮЊВННјЕчЛњЕФЙуЗКгІгУЃЌЖдВННјЕчЛњЕФПижЦЕФбаОПвВдНРДдНЖрЃЌдкЦєЖЏЛђМгЫйЪБШєВННјТіГхБфЛЏЬЋПьЃЌзЊзггЩгкЙпадЖјИњЫцВЛЩЯЕчаХКХЕФБфЛЏЃЌВњЩњЖТзЊЛђЪЇВНЃЛдкЭЃжЙЛђМѕЫйЪБгЩгкЭЌбљдвђдђПЩФмВњЩњГЌВНЁЃЮЊЗРжЙЖТзЊЁЂЪЇВНКЭГЌВНЃЌЬсИпЙЄзїЦЕТЪЃЌвЊЖдВННјЕчЛњНјааЩ§НЕЫйПижЦЁЃБОЮФНщЩмвЛИігУгкздЖЏФЅБпЛњЕФВННјЕчЛњЩ§НЕЫйПижЦЦїЃЌгЩгкПМТЧСЫЭЈгУадЃЌЫќПЩвдгІгУгкЦфЫћГЁКЯЁЃ ДгВННјЕчЛњЕФОиЦЕЬиадПЩжЊЃЌВННјЕчЛњЕФЪфГізЊОиЫцзХТіГхЦЕТЪЕФЩЯЩ§ЖјЯТНЕЃЌЦєЖЏЦЕТЪдНИпЃЌЦєЖЏзЊОиОЭдНаЁЃЌДјЖЏИКдиЕФФмСІдНВюЃЌЦєЖЏЪБЛсдьГЩЪЇВНЃЌЖјдкЭЃжЙЪБгжЛсЗЂЩњЙ§ГхЁЃвЊЪЙВННјЕчЛњПьЫйЕФДяЕНЫљвЊЧѓЕФЫйЖШгжВЛЪЇВНЛђЙ§ГхЃЌЦфЙиМќдкгкЪЙМгЫйЙ§ГЬжаМгЫйЖШЫљвЊЧѓЕФзЊОиМШФмГфЗжРћгУИїИідЫааЦЕТЪЯТВННјЕчЛњЫљЬсЙЉЕФзЊОиЃЌгжВЛФмГЌЙ§етИізЊОиЁЃвђДЫЃЌВННјЕчЛњЕФдЫаавЛАувЊОЙ§МгЫйЁЂдШЫйЁЂМѕЫйШ§ИіНзЖЮЃЌвЊЧѓМгМѕЫйЙ§ГЬЪБМфОЁСПЕФЖЬЃЌКуЫйЪБМфОЁСПГЄЁЃЬиБ№ЪЧдквЊЧѓПьЫйЯьгІЕФЙЄзїжаЃЌДгЦ№ЕуЕНжеЕудЫааЕФЪБМфвЊЧѓзюЖЬЃЌетОЭБиаывЊЧѓМгЫйЁЂМѕЫйЕФЙ§ГЬзюЖЬЃЌЖјКуЫйЪБЕФЫйЖШзюИпЁЃЖјвдЧАЩ§ЫйКЭНЕЫйДѓЖрбЁдёАДжБЯпЙцТЩЃЌВЩгУетжжЗНЗЈЪБЃЌЫќЕФТіГхЦЕТЪЕФБфЛЏгавЛИіКуЖЈЕФМгЫйЖШЁЃдкВННјЕчЛњВЛЪЇВНЕФЬѕМўЯТЃЌЧ§ЖЏТіГхЦЕТЪБфЛЏЕФМгЫйЖШКЭВННјЕчЛњзЊзгЕФНЧМгЫйЖШГЩе§БШЁЃдкВННјЕчЛњЕФзЊОиЫцТіГхЦЕТЪЕФЩЯЩ§БЃГжКуЖЈЪБЃЌжБЯпЙцТЩЕФЩ§НЕЫйВХЪЧРэЯыЕФЩ§НЕЫйЧњЯпЃЌЖјВННјЕчЛњЕФзЊОиЫцТіГхЦЕТЪЕФЩЯЩ§ЖјЯТНЕЃЌЫљвджБЯпОЭВЛЪЧРэЯыЕФЩ§НЕЫйЧњЯпЁЃвђДЫЃЌАДжБЯпЙцТЩЩ§НЕЫйетжжЗНЗЈЫфШЛМђЕЅЃЌЕЋЪЧЫќВЛФмБЃжЄдкЩ§НЕЫйЕФЙ§ГЬжаВННјЕчЛњзЊзгЕФНЧМгЫйЖШЕФБфЛЏКЭЫќЕФЪфГіСІОиБфЛЏЯрЪЪгІЃЌВЛФмзюДѓЯоЖШЕФЗЂЛгЕчЛњЕФМгЫйадФмЁЃБОЯЕЭГбАЧѓвЛжжЛљгкFPGAПижЦЕФАДжИЪ§ЙцТЩЩ§НЕЫйЕФРыЩЂПижЦЫуЗЈЃЌОЖрДЮдЫааЃЌДяЕНдЄЦкФПБъЁЃ 1 МгМѕЫйПижЦЫуЗЈ 1ЃЎ1 МгМѕЫйЧњЯп БОЩшМЦАДееВННјЕчЛњЕФЖЏСІбЇЗНГЬКЭОиЦЕЬиадЧњЯпЭЦЕМГіАДжИЪ§ЧњЯпБфЛЏЕФЩ§НЕЫйТіГхађСаЕФЗжВМЙцТЩЃЌвђЮЊОиЦЕЬиадЪЧУшЪіУПвЛЦЕТЪЯТЕФзюДѓЪфГізЊОиЃЌМДдкИУЦЕТЪЯТзїЮЊИКдиМгИјВННјЕчЛњЕФзюДѓзЊОиЁЃвђДЫАбОиЦЕЬиадзїЮЊМгЫйЗЖЮЇЯТПЩвдДяЕН(ЕЋВЛФмГЌЙ§)ЕФзюДѓЪфГізЊОиРДФтЖЉЩ§НЕЫйТіГхађСаЕФЗжВМЙцТЩЃЌОЭНгНќгкзюДѓзЊОиПижЦЕФзюМбЩ§НЕЫйЙцТЩЁЃетбљФмЙЛЪЙЕУЦЕТЪдіИпЪБЃЌБЃжЄЪфГізюДѓЕФСІОиЃЌМДФмЙЛЖдзюДѓЕФСІОиНјааИњЫцЃЌФмГфЗжЕФЗЂЛгВННјЕчЛњЕФЙЄзїадФмЃЌЪЙЯЕЭГОпгаСМКУЕФЖЏЬЌЬиадЁЃ гЩВННјЕчЛњЕФЖЏСІбЇЗНГЬКЭОиЦЕЬиадЧњЯпЃЌдкКіТдзшФсзЊОиЕФЧщПіЯТЃЌПЩЭЦЕМГіШчЯТЗНГЬЃК  ЪНжаЃЌ  ЮЊзЊзгзЊЖЏЙпСПЃЌKЮЊМйЖЈЪфГізЊОиАДжБЯпБфЛЏЪБЕФаБТЪЃЌІгЮЊОіЖЈЩ§ЫйПьТ§ЕФЪБМфГЃЪ§ЃЌдкЪЕМЪЙЄзїжагЩЪЕбщРДШЗЖЈЁЃfmЮЊИКдизЊОиЯТВННјЕчЛњЕФзюИпСЌајдЫааЦЕТЪЃЌВННјЕчЛњБиаыдкЕЭгкИУЦЕТЪЯТдЫааВХФмБЃжЄВЛЪЇВНЁЃ(1)ЪНЮЊВННјЕчЛњЕФЩ§ЫйЬиадЃЌгЩДЫЗНГЬПЩЛцжЦГіЕчЛњЩ§ЫйЧњЯпЁЃ(1)ЪНБэУїЧ§ЖЏТіГхЕФЦЕТЪfгІЫцЪБМфtзїжИЪ§ЙцТЩЩЯЩ§ЃЌетбљОЭПЩвддкНЯЖЬЕФЪБМфФкЪЙВННјЕчЛњЕФзЊЫйЩЯЩ§жСвЊЧѓЕФдЫааЫйЖШЁЃМјгкДѓЖрЪ§ЕФВННјЕчЛњЕФОиЦЕЬиадЖМНќЫЦЯпадЕнМѕЕФЃЌЫљвдЩЯЪіЕФПижЦЙцТЩЮЊзюМбЁЃ 1ЃЎ2 МгМѕЫйРыЩЂДІРэ дкБОЯЕЭГжаЃЌFPGAЪЙгУЗжЦЕЦїЕФЗНЪНРДПижЦВННјЕчЛњЕФЫйЖШЃЌЩ§НЕЫйПижЦЪЕМЪЩЯЪЧВЛЖЯИФБфЗжЦЕЦїГѕдижЕЕФДѓаЁЁЃжИЪ§ЧњЯпгЩгкЮоЗЈЭЈЙ§ГЬађБржЦРДЪЕЯжЃЌПЩвдгУНзЬнЧњЯпРДБЦНќЩ§ЫйЧњЯпЃЌВЛвЛЖЈУПВНЖММЦЫузАдижЕЁЃ ШчЭМ1ЫљЪОЃЌзнзјБъЮЊЦЕТЪЃЌЕЅЮЛЪЧВН/УыЃЌЦфЪЕЗДгГСЫзЊЫйЕФИпЕЭЁЃКсзјБъЮЊЪБМфЃЌИїЖЮЪБМфФкзпЙ§ЕФВНЪ§гУNРДБэЪОЃЌВНЪ§ЦфЪЕЗДгГСЫааГЬЁЃЭМжаБъГіРэЯыЩ§ЫйЧњЯпКЭЪЕМЪЩ§ЫйЧњЯпЁЃ  ВННјЕчЛњЕФЩ§ЫйЙ§ГЬПЩАДвдЯТВНжшНјааДІРэЁЃ (1)ШєЪЕМЪдЫааЫйЖШЮЊfgЃЌДг(3ЃЎ4)ЪНжаПЩЫуГіЩ§ЫйЪБМфЮЊЃК  (2)НЋЩ§ЫйЖЮОљдШЕиРыЩЂЮЊnЖЮМДЮЊНзЬнЩ§ЫйЕФЗжЕЕЪ§ЃЌЩЯЩ§ЪБМфЮЊtrЃЌдђУПЕЕЫйЖШБЃГжЪБМфЮЊЃК  ГЬађжДааЙ§ГЬжаЃЌЖдУПЕЕЫйЖШЖМвЊМЦЫудкетЕЕЫйЖШгІзпЕФВНЪ§ЃЌШЛКѓвдЕнМѕЗНЪНМьВщЃЌМДУПзпвЛВНЃЌУПЕЕВНЪ§Мѕ1ЁЃЕБМѕжССуЪБЃЌБэЪОИУЕЕЫйЖШгІзпЕФВНЪ§МКзпЭъЃЌгІНјШыЯТвЛЕЕЫйЖШЁЃвЛжБбЛЗЕНИјГіЕФЫйЖШДѓгкЛђЕШгкИјЖЈЕФЫйЖШЮЊжЙЁЃМѕЫйЙ§ГЬгыЩ§ЫйЙ§ГЬИеКУЯрЗДЁЃ 2 ЦЕТЪТіГхЕФЪЕЯж ЦЕТЪТіГхФЃПщЕФКЫаФЪЧПЩПиЗжЦЕЦїЃЌгЩЭтВПЕФОЇеёВњЩњБъзМЦЕТЪЃЌжЛвЊдкЗжЦЕЦїЕФЪфШыЖЫЪфШыЯргІЕФЗжЦЕЯЕЪ§ЃЌОЭПЩвдЕУЕНЫљашЕФЦЕТЪЁЃБОФЃПщЪЧРћгУVHDLгВМўУшЪігябдЃЌЭЈЙ§QuartusIIПЊЗЂЦНЬЈЃЌЪЙгУAlteraЙЋЫОЕФFPGAЃЌЩшМЦСЫвЛжжФмЙЛТњзуЩЯЪіИїжжвЊЧѓЕФНЯЮЊЭЈгУЕФПЩПиЗжЦЕЦїЁЃЭМ2ЮЊЗжЦЕЦїЕФдРэЭМЃЌЭМ3ЮЊЗжЦЕЦїЕФЗТецВЈаЮЭМЁЃ  3 Нсгя ЛљгкгВМўУшЪігябдVHDLЩшМЦЕФПижЦЦїОпгаПЊЗЂЩшМЦжмЦкЖЬЁЂЗчЯеЕЭЁЂЯЕЭГМЏГЩЖШИпЁЂЙІКФЕЭЕШгХЕуЃЌНЋЪЧаОЦЌЩшМЦЕФжїСїЗНЯђЁЃПЊЗХЪНЪ§ПиЯЕЭГжаЃЌбаОПЪЕЯжФмгВМўИДгУЕФМгМѕЫйФЃПщвдМАЯрЙиЙІФмФЃПщЃЌРћгУПЩБрГЬТпМЦїМўFPGAЕФПЩжиЙЙФмСІЃЌФмАДашЧѓСщЛюЪЕЯжЙІФмШЋЖЈжЦЕФдЫЖЏПижЦаОЦЌЁЃБОЮФЩшМЦСЫздЖЏФЅБпЛњжаЕФжИЪ§МгМѕЫйПижЦЦїЁЃдкДЫЛљДЁЩЯЃЌжЛашРЉеЙЯргІИіЪ§ЕФМгМѕЫйФЃПщМДПЩЪЕЯжЖржсСЊЖЏМгМѕЫйПижЦЁЃ |

ЭјгбЦРТл