SOPC 技术在直序扩频收发机模块中频的应用

发布时间:2010-8-10 14:36

发布者:lavida

|

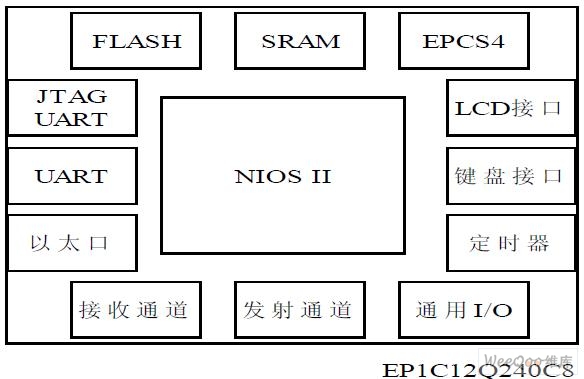

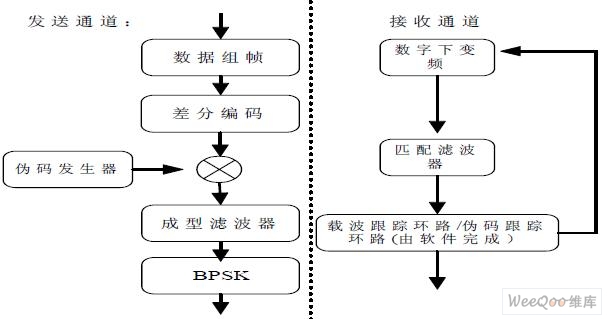

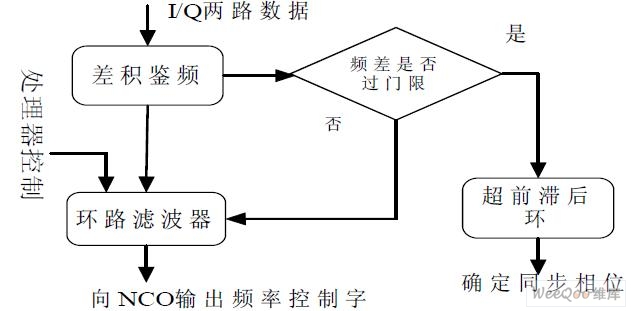

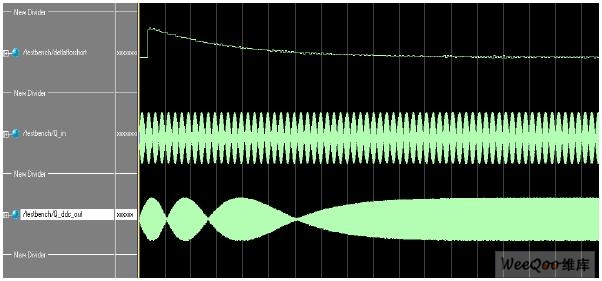

1 前言 嵌入式系统发展朝着小体积、低功耗、高性能的趋势发展。MCU、DSP 和FPGA 三种处理器在现代嵌入式系统中扮演的角色呈现三分天下的局面。为了结合MCU、DSP 和FPGA 各自的优点,上个世纪90 年代末期到本世纪初,各个可编程逻辑器件厂商开始提出自己的SOPC(System on a programmable chip) 片上可编程系统的软件和硬件一体化解决方案,并提供从低端的消费电子到高端的网络通信等市场产品。SOPC 概念的提出给今后嵌入式的发展提供了很好的方向。 Altera 公司推出的NIOS II 嵌入式处理器是目前世界上最流行的软核嵌入式处理器。把NIOS II 嵌入到FPGA 中,用户可以获得200DMIPS 的性能,并可以从60 多个ALTERA 提供的IP 核中选择所需要的,以此来创建一个最适合的嵌入式系统。 目前扩频收发机处理模块的实现方式主要有两种,一种是专用芯片,如STEL2000A 直接序列扩频系统专用芯片。另一种是以DSP 芯片为核心,搭配外围FPGA 来实现扩频信号的处理。采用专用芯片可以降低系统的开发难度,但是缺乏灵活性,不能满足特殊场合的应用。随着数字信号处理器和可编程器件的功能不断增强,DSP + FPGA 这一模式得到越来越广泛的应用。DSP + FPGA 芯片的高速运算性能使得部分硬件功能软件化,极大地增强了系统的灵活性。另一方面,可编程逻辑器件厂商通过在FPGA 芯片中嵌入硬核或软核嵌入式处理器,极大地增强了芯片的功能,改变了以往只是将FPGA 作为外围芯片这一模式。我们用嵌入式处理器替代专用DSP 处理器和通用控制器,再配以众多的IP 核资源,就可以在单片FPGA 上构建一个可编程片上系统,即SOPC(System On Programmable Chip)。本文将用 NIOS II 的SOPC 解决方案实现一个扩频收发机中频模块。 2 设计思想 本文应用背景为直扩抗干扰扩频电台的研制项目。在发射端将信号扩频调制后发送出去,在接收端将信号解扩解调后显示并存储。即实现信息的无线扩频传输。项目要求的电台具有功耗低,体积小,外围接口丰富灵活,扩频码码长可变,能适用于多种需求方式下,并具有可升级功能等特点。 根据分析,使用专用芯片显然不能满足方案的特殊要求。另外,使用 FPGA+DSP 的传统方案,由于DSP 相对固定的外界接口,无法向外界提供丰富且灵活的接口,限制了它在某特殊场合的应用,而且方案的成本高,体积大。特别是对于系统的升级或者系统要求有所改变时候,该方案显得十分困难。而本文提出的基于NIOS II 的SOPC 解决方案则完全可以胜任项目的需求。 3 系统介绍 3.1 系统结构介绍 本设计选用 FPGA 其中嵌入NIOS II 的方式实现扩频收发机。扩频收发机系统FPGA 整体框图如下:  FPGA 选用Altera 公司的EP1C20Q240C8,嵌入处理器选用NIOS II 标准型,可以达到200DMIPS 的性能。8M 的SRAM 缓存上位机与FPGA 的交换数据,32M 的FLASH 用于存储NIOS II 的软件代码和要保存的数据。EPCS4 是ALTERA 专用的存储器,存储FPGA 的配置文件。上位机可通过UART 和以太口向设备传输数据,而JTAG UART 则可以使FPGA在线编程,不断更新硬件,提供方便实用的升级方案。LCD 和键盘构成人机界面。接收发送模块用于完成扩频解扩的算法,另外系统还包括必要的I/O 以及指示灯。 3.2 系统设计分析 本系统使用这样的方案,是根据 NIOS II 的特点决定的。首先,NIOS II 具有可裁减,可搭建的特点,可以向片外提供多种且多个接口,提供的种类完全由设计者决定。因此本方案提供了串口,以太口,LCD 接口,键盘接口,存储器接口等。如果在其它环境应用需要别的接口,只需要再向NIOS II 添加即可,不用改换处理器芯片,大大增加系统灵活性。其次,在单片 FPGA 上进行开发,避免多个芯片(如DSP)协同开发的麻烦,降低了开发难度,同时降低了调试难度。特别是FPGA 所自带的JTAG UART 口可以实现用户的硬件升级,大大增加产品的生命周期。 3.3 主要模块介绍 收发通道:将计算机上的文件通过标准串口存储到SRAM,根据人机界面的指示NIOSII 将SRAM 的数据读出,并在NIOS II 的控制下进入发送通道。在发送通道中,首先将数据进行必要的组帧,扩频(扩频码由人机界面设定的伪码提供),通过成型滤波器消去码间串扰,最后进行BPSK 调制发送到射频模块。框图如下:  接收通道:数字信号进入接收通道。在接收通道中,首先进行数字下变频,然后通过匹配滤波器(根据人机界面设定的扩频码选择相应的匹配滤波长度),最后经过载波跟踪环路和码跟踪环路(在NIOS II 上编程完成)解调解扩数据,按照设定输出给电脑或者存入flash。 人机界面: 由系统提供的键盘和液晶显示器可以根据用户的要求配置系统,并将设置结果和必要的系统信息反映给用户。配置的内容包括: 是否将数据保存到 flash。 设置并提供扩频码,同时在接收端根据设置进行可变长度的匹配滤波。 调整载波跟踪环中环路参数,以不同的策略进行跟踪。 液晶显示器可以根据以上配置提供的信息来显示给用户。 3.4 软件实现部分: 载波跟踪环和码跟踪环由于控制比较复杂,运算比较多而实时性要求不高所以采用NIOS II 上软件来实现。流程如下:  载波的环路滤波器输入是上级的频差信号,同时根据NIOS II 的输入来调整环路参数,采用不同的跟踪策略。输出频率控制字给NCO。下图说明频差的变化以及数字下变频前后信号的变化。  上图是在modelsim5.7 上的布线后仿真图,第一个信号是频差,第二个信号是未下变频的信号,第三个信号是下变频以后的信号。由图可见频差在不断缩小变成零,下变频信号最后频率消失,同步成为一条直线。 4 结束语: 本方案采用SOPC 的概念实现扩频收发机,较之传统的FPGA+DSP 方案,新的嵌入式方案降低了硬件复杂度,增强了系统的灵活性,降低了开发成本和调试难度,使用户高效快速的搭建系统。可以想象,在不久的将来,SOPC 技术将成为嵌入式发展的先锋。 本文的创新点:详细说明了一款基于SOPC 技术的直序扩频收发机中频模块设计方案。该系统以一片FPGA 其中嵌入软核的方式完成系统全部功能,提高系统可靠性,大大增加了系统灵活性,提高了扩展性。 |

网友评论