АыУГ¶аНЁөАADCК№ПөНіРФДЬҙпөҪёьПИҪшЛ®ЖҪ

·ўІјКұјдЈә2010-8-6 15:51

·ўІјХЯЈәlavida

|

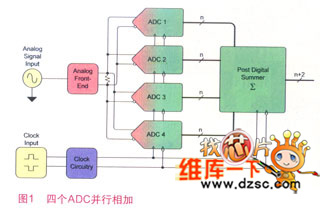

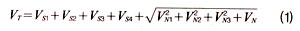

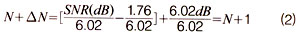

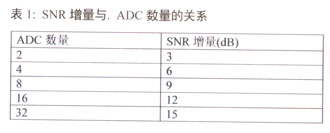

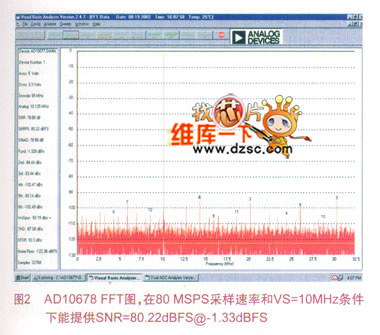

ҫНПсНГЧУУХ»у№·ИьЕЬТ»СщЈ¬НГЧУұШРлТӘұИ№·ЕЬөДҝмЈ¬ТӘЗуЧоСПёсөДКэҫЭІЙјҜПөНіөДРФДЬЧФИ»ТӘёЯУЪГсУГДЈКэЧӘ»»Жч(ADC)ЎЈХвР©ј«СПёсөДТӘЗуНЖ¶ҜICЦЖФмЙМј°ЖдУГ»§өД·ўХ№Ј¬іцПЦРн¶аВъЧгёЯ¶ЛКэҫЭІЙјҜПөНіРиЗуөДЎ°ФцЗҝРФДЬЎұөДҙҙРВ·Ҫ·ЁЎЈ ЖдЦРТ»ЦЦ·Ҫ·ЁКЗНЁ№эІЙУГ¶аНЁөАADCМоідЧӘ»»ЖчөДЎ°КұП¶ЎұАҙҙу·щ¶ИФцјУІЙСщЛЩВКЎўҪөөНФлЙщ»тА©Х№¶ҜМ¬·¶О§ЎЈЛжЧЕёш¶ЁҙшҝнәН·ЦұжВКПВөДөҘёцADCөДіЙұҫЎўіЯҙзәН№ҰәДөДҪөөНЈ¬ІўЗТЛжЧЕ¶аёцЧӘ»»ЖчЈЁНЁіЈ·вЧ°ФЪТ»ЖрЈ©өДУҰУГФҪАҙФҪ¶аЈ¬ёГ·Ҫ·ЁұдөГФҪАҙФҪЗРКөҝЙРРЎЈ ұҫОДҪ«МЦВЫБҪЦЦ¶аНЁөА·Ҫ·ЁЈәРЕәЕЖҪҫщ--ұЈЦӨІЙСщЛЩВКІ»ұдЈ¬ФцјУ·ЦұжВКЈ»КұјдҪ»ЦҜЎӘЎӘұЈЦӨ·ЦұжВКІ»ұдЈ¬МбёЯІЙСщЛЩВКЎЈІЙУГХвБҪЦЦ·Ҫ·ЁөДІъЖ·ТСҫӯө®ЙъЈ¬АэИзADI№«ЛҫөДAD10678(16 bitЈ¬80 MSPS ADC)әНAD12500(12 bitЈ¬500 MSPS ADC)ЎЈ РЕәЕЖҪҫщ РЕФлұИЈЁSNRЈ¬ТФ dBОӘөҘО»Ј©Ј¬КЗіЙПсәНАЧҙпөИУҰУГЦРөД№ШјьРФДЬЦёұкЎЈХвР©ПөНіЦРК№УГөДADCҝЙДЬ»бКЬөҪРн¶аНвІҝФлЙщФҙөДУ°ПмЈ¬°ьАЁКұЦУФлЙщЎўөзФҙФлЙщәНІјПЯТэИлөДсоәПКэЧЦФлЙщЎЈЦ»ТӘІ»Па№ШФлЙщФҙөДЖҪ·ҪәНөДЖҪ·ҪёщЈЁRSSЈ©РЎУЪADC№МУРБҝ»ҜФлЙщЈ¬КдіцЖҪҫщҫН»бУРР§өШҪөөНЧЬМеұҫөЧФлЙщЎЈ ДЗР©РиТӘҪПёЯSNRөДПөНіНЁіЈК№УГКэЧЦәуҙҰАнЖчҪ«¶аёцADCНЁөАөДКдіцјУәНЎЈРЕәЕЦұҪУПајУЈ¬¶шАҙЧФөҘ¶АADCЈЁјЩЙиІ»Па№ШЈ©өДФлЙщІЙУГRSSјУәНЈ¬ТтҙЛКдіцјУәНМбёЯБЛЧЬМеSNRЎЈЛДёцADCКдіцөДјУәН»бМбёЯ6 dB SNRЈ¬јҙ1 LSBЎЈAD6645 14 bit 80 MSPS ADC№ж¶ЁУРР§О»КэЈЁENOBЈ©ОӘ12ЎЈНј1КҫіцЛДёцAD6645өДКдіцјУәНФцјУБЛ2 bit·ЦұжВКәН1 bitРФДЬЎЈ  ГҝёцADCөДКдИл°ьә¬Т»ёцРЕәЕПоЈЁVSЈ©әНТ»ёцФлЙщПоЈЁVNЈ©ЎЈ¶ФЛДёцФлЙщөзС№ЗуәНөГөҪөДЧЬөзС№VTөИУЪЛДёцРЕәЕөзС№өДПЯРФәНјУЙПЛДёцФлЙщөзС№өДRSSЦөЈ¬јҙЈә  УЙУЪVS1=VS2=VS3=VS4Ј¬өИР§УЪРЕәЕұ»·ЕҙуБЛЛДұ¶Ј¬¶шADCөДФлЙщЈЁRMSЦөЈ©Ц»·ЕҙуБЛБҪұ¶Ј¬ҙУ¶шК№РЕФлұИФцҙуБҪұ¶Ј¬јҙФцјУ6.02 dBЎЈТтҙЛЈ¬ЛДВ·РЕәЕЗуәНЛщ»сөГөД6.02 dBФцБҝ(?SNR)К№УРР§·ЦұжВКМбЙэБЛ1bitЎЈТтОӘSNR(dB)=6.02N+1.76Ј¬NОӘО»КэЈ¬ЛщТФЈ¬  ұн1 ЦРКҫіцБЛ¶аёцADCКдіцјУәНЛщ»сөГөДSNRФцБҝЎЈҙУјтөҘРФҝјВЗЈ¬ЛДёцADCјУәНКЗПФИ»өДСЎФсЎЈДіР©ЦШТӘУҰУГТІ»бҝјВЗёь¶аөДADCјУәНЈ¬ө«УҰИЎҫцУЪЖдЛьПөНіЦёұкТӘЗуЈЁ°ьАЁіЙұҫЈ©әНҝЙМṩөДУЎЦЖөзВ·°еЈЁPCBЈ©іЯҙзЎЈ  14 bit ADCАнПлөДSNRОӘ(6.02 ЎБ 14) + 1.76 = 86.04 dBЎЈИ»¶шЈ¬AD6645өДјјКхЧКБПЦРМṩөДSNRөДөдРНЦөҪцОӘ74 dBЈ¬ЛщТФЖдENOBҪцОӘ12 bitЎЈ ТтҙЛЈ¬ЛДВ·ЧӘ»»ЖчКдіцЗуәНҝЙТФІ№іҘ¶оНвөД1 bit·ЦұжВКЈ¬јУЙПФӯАҙПөНіј¶ENOBҝЙөҪҙп13 bit(80 dB) ЎЈ өұИ»Ј¬ХвСщөДПөНіРиТӘё¶іцТ»Р©ЙијЖЕ¬БҰЈ¬ТФј°Т»Р©ПөНіФӯРНЙијЖЎўјш¶ЁәНІвКФҝӘ·ўөДҙъјЫЎЈө«КЗЈ¬AD10678јҜіЙБЛ4ёцAD6645Ј¬Т»ёцКұЦУ·ЦЕдПөНіЈ¬ТФј°Т»ёцТСЕдЦГәГөДёҙФУҝЙұаіМВЯјӯЖчјю(CPLD)ТФМṩёЯЛЩјУ·ЁФЛЛгЎЈПЦФЪҝЙМṩөДAD10678ТФөНіЙұҫәНХјУГ2.2 ЎБ 2.8УўҙзPCBГж»эөД·вЧ°Ј¬НЁ№эІвКФНкИ«ҙпөҪ№ж¶ЁјјКхЦёұкЎЈНј2ЛщКҫөДҝмЛЩёөБўТ¶ұд»»ЈЁFFTЈ©Ҫб№ыЦӨГчБЛADCөДУЕБјРФДЬЈ¬ФЪ80 MSPSКұЦУәН10 MHzДЈДвКдИлМхјюПВДЬ№»Мṩ80.22 dB SNRЎЈ  іэБЛМбёЯSNRЈ¬ХвЦЦМеПөҪб№№»№МбёЯБЛDCҫ«¶ИЎЈЛДёцADCөДК§өчәНФцТжОуІоКЗІ»Па№ШөДЈ¬ТтҙЛІЙУГҪөөНФлЙщТ»СщөД·Ҫ·ЁАҙҪөөНПөНіК§өчәНФцТжОуІоЎЈө«КЗФЪПЯРФОуІо·ҪГжЙПГ»УРёДЙЖЈ¬КөјКЙПОЮФУЙў¶ҜМ¬·¶О§(SFDR)ИЎҫцУЪЧоІоөДADCЎЈ ө«КЗХвЦЦ·Ҫ°ёРиТӘХјУГҪПҙуөДPCBГж»эәН4ұ¶өД№ҰәДЈ¬ө«УлТФ4ұ¶ІЙСщЛЩВК№ӨЧчөДөҘADCөДКдіцЖҪҫщ·Ҫ°ёПаұИЈ¬ІЙУГХвЦЦ·Ҫ·ЁИФИ»ҫЯУРУЕКЖЎЈҫЎ№ЬТФМбёЯІЙСщЛЩВКФцјУІЙСщөгКэТІ»бҪөөНКдИлРЕәЕЦРөДіЈДЈФлЙщЎЈЛжЧЕЦЖФм№ӨТХөДёДҪшЈ¬РВөДЙијЖК№ADCөДДЪәЛ№ҰәДҪшТ»ІҪҪөөНЈ»БнНвҝЙМṩөД4НЁөАәН8НЁөАADCөДіцПЦК№¶аADCПөНіёьИЭТЧКөПЦЈ¬ІўЗТјхРЎБЛ·вЧ°іЯҙзЎЈАэИзЈ¬AD9259 4 НЁөА14 bit, 50 MSPS ADCІЙУГ 48ТэПЯLFCSP (7 mm ЎБ 7 mm) ·вЧ°Ј¬ЖдГҝНЁөА№ҰәДҪцОӘ100 mWЎЈ ЛдИ»УГМбёЯКдИлөзС№өДұкЧј»ҜЧц·ЁАҙМбёЯ№ж¶ЁөДSNRКЗҝЙРРөДЈ¬ө«Хв»бФцјУЗэ¶Ҝ·ЕҙуЖчөДЙијЖС№БҰЈ¬ІўЗТУЙУЪРЕәЕәНФлЙщТ»Жрұ»·ЕҙуЈ¬ЛщТФ»бҪөөНПөНіSNRЎЈјУәНМеПөҪб№№өДБнТ»ёцОўГоУЕөгКЗЈ¬Въ¶ИДЈДвКдИлІ»РиТӘҙуУЪК№УГөҘADCКұөДКдИлЎЈ ұИҪПУІјюәНИнјюіЙұҫЈ¬РЕәЕЖҪҫщөД·Ҫ·ЁұҫЙнТӘұИКэЧЦВЛІЁУРУЕКЖЈ¬ө«¶ФУЪТӘМṩҫӯјГУРР§өДУІјюҙҰАнәНИнјюВЛІЁөДЧЬМеПөНіҝјВЗЛщТӘЗуөДКэЧЦВЛІЁЈ¬ИнјюіЈіЈК№№ӨЧчёьИЭТЧЎЈ |

НшУСЖАВЫ