0.35ҰМm CMOS№вҪУКХ»ъЗ°ЦГ·ЕҙуЖчЙијЖ

·ўІјКұјдЈә2010-8-4 09:55

·ўІјХЯЈәlavida

|

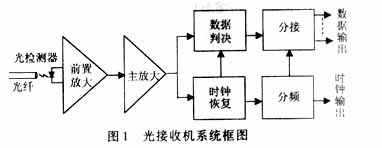

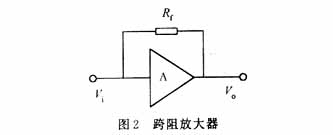

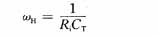

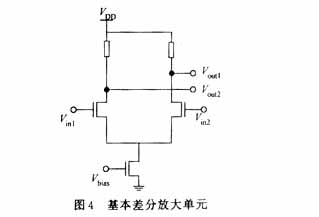

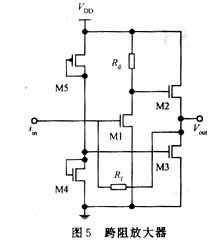

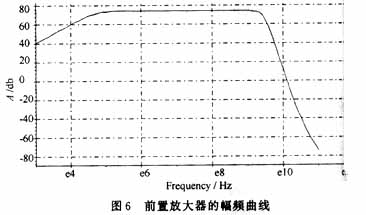

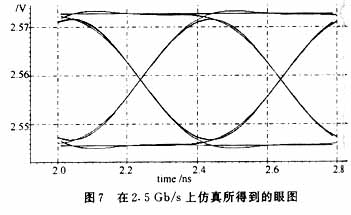

ҪьДкАҙЈ¬ЛжЧЕЙз»бРЕПў»ҜіМ¶ИІ»¶ПМбёЯЈ¬РЕПўҪ»»»БҝіКұ¬ХЁРФФціӨЈ¬№вПЛНЁРЕёЙПЯПөНіТФЖдёЯЛЩЎўҙуИЭБҝөДУЕөгұ»№г·әУҰУГУЪөзРЕНшЎўјЖЛг»ъНшВзЎЈ2Ј®5 Gb/sі¬ёЯЛЩ№вПЛНЁРЕПөНіТСҫӯН¶ИлК№УГЎЈЧчОӘ№вПЛНЁРЕПөНіЦР№вҪУКХ»ъөД№ШјьІҝ·ЦЈ¬З°ЦГ·ЕҙуЖчөДРФДЬФЪәЬҙуіМ¶ИЙПҫц¶ЁБЛХыёц№вҪУКХ»ъөДРФДЬЎЈ №эИҘЈ¬¶ФУЪёЯЛЩөДјҜіЙөзВ·Ј¬¶аІЙУГGaAs№ӨТХАҙКөПЦЎЈө«КЗЛжЧЕЙоСЗОўГЧCMOS№ӨТХөДІ»¶П·ўХ№Ј¬ХӨіӨІ»¶ПјхРЎЈ¬ПЦФЪ0Ј®35ҰМm CMOS№ЬөДҪШЦ№ЖөВКТСҫӯҙпөҪ13Ј®5 GHzЈ¬ҝЙТФКөПЦёЯЛЩөДјҜіЙөзВ·ЎЈұҫОДІЙУГМЁНеTSMC0Ј®35ҰМmCMOS№ӨТХКөПЦБЛУГУЪ№вПЛҙ«КдПөНіSTM- 16 (2.5Gb/s)ЛЩВКј¶өДЗ°ЦГ·ЕҙуЖчЎЈ 1 З°ЦГ·ЕҙуЖчјтҪй З°ЦГ·ЕҙуЖчФЪ№вҪУКХ»ъПөНіЦРЛщҙҰО»ЦГИзНј1ЛщКҫЎЈУЙНј1ҝЙјыЈ¬№вҪУКХ»ъЦчТӘУЙЈә№вјмІвЖчЎўЗ°ЦГ·ЕҙуЖчЎўЦч·ЕҙуЖчЎўКэҫЭЕРҫцөзВ·ЎўКұЦУ»ЦёҙөзВ·әН·ЦҪУЖчөИөзВ·ЧйіЙЎЈЖдЦРЗ°ЦГ·ЕҙуЖчҙҰФЪ№вҪУКХ»ъПөНіөДЗ°¶ЛЈ¬ҙҰАнөДКЗОўИхөДРЕәЕЈ¬ТтҙЛЛыөДРФДЬҪ«ЦұҪУУ°ПмХыёц№вҪУКХ»ъөДРФДЬЎЈ  ФЪҪУКХ»ъЦРЈ¬јмІвЖчёРУҰ№вРЕәЕЈ¬КдіцҰМAј¶өзБчВціеРЕәЕЎЈ¶шЗ°ЦГ·ЕҙуЖчөДЧчУГҫНКЗҪ«ҙЛөзБчРЕәЕ·ЕҙуІўЧӘ»ҜіЙөзС№РЕәЕЈ¬Цч·ЕҙуЖчҪ«З°ЦГ·ЕҙуЖчКдіцөДөзС№РЎРЕәЕ·ЕҙуЦБТ»ёцЧг№»ҙуЗТәг¶ЁөД·щ¶ИЈ¬ТФұгЗэ¶ҜәуРшКұЦУ»ЦёҙәНКэҫЭЕРҫцөзВ·ЎЈКұЦУ»ЦёҙәНКэҫЭЕРҫцөзВ·УГАҙКөПЦКұЦУәНКэҫЭөДФЩЙъЎЈЧоәу·ЦҪУЖч°СёЯЛЩКэҫЭБч·ЦҪУОӘөНЛЩКэҫЭБчЎЈЛщТФ¶ФЗ°ЦГ·ЕҙуЖчУРТФПВјёөгТӘЗуЈә (1)ҫЎБҝјхРЎөзВ·ұҫЙнТэИлөДФлЙщЎЈ (2)УРЧг№»ёЯөДФцТжЈ¬МбёЯБйГф¶ИЎЈ (3)УлРЕәЕЛЩВКПаККУҰөДҙшҝнЎЈ 2 өзВ··ЦОц ТӘ°СөзБчРЕәЕЧӘ»ҜіЙөзС№РЕәЕЈ¬Т»ЦЦУРР§өД·Ҫ°ёКЗІЙУГҝзЧиРНЗ°ЦГ·ЕҙуЖчЈ¬ИзНј2ЛщКҫЎЈ  ХвЦЦАаРНөД·ЕҙуЖчНЁ№э·ҙАЎөзЧиRfМṩёә·ҙАЎЈ¬ДЬМṩһ¶ЁөДФцТжәНҙуөДҙшҝнЎЈ ҝзЧи·ЕҙуЖчөДҙшҝнұнКҫОӘ  ЖдЦРЈәRiRf/AОӘ·ЕҙуЖчөДКдИлЧиҝ№ЎЈ Нј2ЦРAОӘ·ЕҙуЖчөДҝӘ»·ФцТжЈ»CTОӘКдИлјДЙъөзИЭЈ¬°ьАЁ№вјмІвЖчөДҪбөзИЭәН·вЧ°өзИЭЎЈЛщТФЈ¬ҝЙТФҝҙіцКдИлөзЧиәНКдИлөзИЭҫц¶ЁБЛ·ЕҙуЖчөДҙшҝнЎЈАэИзЈ¬јхРЎRfЈ¬»бК№ФцТжјхРЎЎўҙшҝнұдҝнЎЈө«RfјхРЎ»бК№өзВ·өДФлЙщұдҙуЈ¬ҪөөН·ЕҙуЖчөДБйГф¶ИЎЈТтҙЛЈ¬ОӘҙпөҪөзВ·өДЙијЖТӘЗуҫНРиФЪФлЙщЎўФцТжәНҙшҝнөИРФДЬЦ®јдҪшРРХЫЦФЎЈ 3 өзВ·ЙијЖ З°ЦГ·ЕҙуЖчөДҪб№№ҝтНјИзНј3ЛщКҫЎЈ  Нј3ЦР№вјмІвЖчөИР§ОӘөзБчФҙiinәНөзИЭCinІўБӘЈ¬CinОӘҪбөзИЭЈ»БнНвЈ¬ФЪЗ°ЦГ·ЕҙуЖчәуФцјУБЛ»щұҫІо·Ц·ЕҙуөҘФӘИзНј4ЛщКҫЈ¬ДҝөДКЗКөПЦөзВ·өДЛ«¶ЛКдіц(ЖдәуЦч·ЕҙуЖчОӘЛ«¶ЛКдИл)Іў·ЕҙуРЕәЕЎЈІЙУГБҪј¶Іо·Ц·ЕҙуЖчЈ¬Ц®јдУГФҙј«ёъЛжЖчКөПЦЗ°Т»ј¶КдіцәНәуТ»ј¶КдИлөДЦұБчөзЖҪПаЖҘЕдЎЈ  Іо·Ц·ЕҙуЖчөДБҪКдИл¶Л·ЦұрУлҝзЧи·ЕҙуЖчөДКдіц¶ЛЦұҪУБ¬ҪУәННЁ№эТ»ёцRCВЛІЁНшВзБ¬ҪУЈ¬ҙУ¶шұЈЦӨ»щұҫІо·Ц·ЕҙуЖчБҪКдИл¶ЛҫЯУРПаН¬өДЦұБчөзЖҪЎЈRCөННЁНшВзөДRCіЈКэҫц¶ЁБЛЗ°ЦГ·ЕҙуЖчөДөНЖөҪШЦ№ЖөВКfLЎЈФЪfLТ»¶ЁөДЗйҝцПВЈ¬RФҪҙуЈ¬ЛщРиТӘөДCҫНФҪРЎЎЈ ҝзЧи·ЕҙуЖчИзНј5ЛщКҫЈ¬ІЙУГөзС№ІўБӘёә·ҙАЎөДРОКҪЎЈУЙ№ІФҙ·ЕҙуәНФҙј«ёъЛжЧйіЙ»щұҫ·ЕҙуІҝ·ЦЈ¬УлRf№ІН¬№№іЙөзС№ІўБӘёә·ҙАЎЎЈ  4 ДЈДвҪб№ы ІЙУГМЁНеTSMC0Ј®35ҰМmCMOS№ӨТХМṩөДBSIM3ФӘјюДЈРНәНЙМУГөДSmartSpiceөзВ··ВХжИнјю¶ФЗ°ЦГ·ЕҙуЖчҪшРРБЛ·ВХжЎЈ ДЈДвҪ»Бч·ЦОцөГөҪөД·щЖөМШРФЗъПЯИзНј6ЛщКҫЎЈ·ЕҙуЖчЧЬөДФцТжОӘ73 dBҰёЈ¬3 dBҙшҝнОӘ2Ј®2 GHzЎЈөНЖөҪШЦ№ЖөВКОӘ50 kHzЎЈ  Нј7ОӘКдИл5ҰМAЈ¬2Ј®5 Gb/sөДОұЛж»ъРтБРЈ¬ІЙУГSmartSpice·ЦОцЛщөГКдіцСЫНјЎЈ  5 °жНјЙијЖ З°ЦГ·ЕҙуЖчәЛ°жНјИзНј8ЛщКҫЈ¬НјЦРЧуЙПІҝ·ЦОӘҝзЧи·ЕҙуЖчЈ¬КЗТ»ёцІ»¶ФіЖөДНјРОЎЈУТ°лІҝ·ЦКЗБҪј¶Іо·Ц·ЕҙуЖчЈ¬УЙУЪКЗ¶ФіЖөДНјРОЈ¬ЛщТФФЪ»жЦЖ°жНјКұҝЙТФЦ»»ӯЙПұЯІҝ·ЦЈ¬И»әуёҙЦЖ·ӯЧӘПВАҙЎЈҝзЧи·ЕҙуЖчәНІо·Ц·ЕҙуЖчЦ®јдКЗRCөННЁНшВзөДөзЧиЈ¬өзИЭЦөұИҪПҙуЈ¬ІЙУГНвҪУРОКҪЎЈЙППВұЯҪзҙҰНјРООӘөзФҙПЯЈ¬ПЯөДҝн¶ИТӘЧг№»ҝнЈ¬ТФГвөзБч№эҙуЙХ»ЩЎЈЦРјдәбПЯОӘөШПЯЈ¬Н¬КұК№УГБҪІгҪрКфЈ¬ХвСщјИјхРЎБЛПЯҝнЎўҪЪКЎБЛГж»эУЦДЬұЈЦӨНЁ№эҙуөДөзБчЎЈ  ёГ°жНјІЙУГCadenceЙијЖ№ӨҫЯЙијЖЎЈГж»эОӘ40Ј®15 mmЎБ0Ј®20 mmЎЈёГРҫЖ¬ТСНЁ№эМЁНеTSMC0Ј®35ҰМmөДNЪеЎўБҪІг¶аҫ§№иЎўЛДІгҪрКфөДCMOS№ӨТХБчЖ¬Ј¬УЙУЪЗ°ЦГ·ЕҙуЖчәНЦч·ЕҙуЖчТ»Н¬БчЖ¬Ј¬РҫЖ¬ЧЬГж»эОӘ1 mmЎБ0Ј®70 mmЎЈ РҫЖ¬ПФОў·ЕҙуХХЖ¬ИзНј9ЛщКҫЈ¬НјЦРЧу°лІҝ·ЦОӘЗ°ЦГ·ЕҙуөзВ·Ј¬УТ°лІҝ·ЦОӘПЮ·щ·ЕҙуөзВ·ЎЈ  6 Ҫб№ыІвКФ УЙУЪІвКФМхјюЛщПЮЈ¬ІвКФЦРЦ»ДЬУГОұЛж»ъВл·ўЙъЖчІъЙъөДөзС№ВціеРЕәЕАҙҙъМжёЯЛЩөДВціеөзБчРЕәЕЈ¬ІвКФПөНіҝтНјИзНј10ЛщКҫЎЈ  Нј11ОӘХыёцРҫЖ¬ФЪЖ¬ІвКФҪб№ыЎЈЗ°ЦГ·ЕҙуЖчКдИлОӘ2Ј®5 Gb/s·е·еЦө10 mVөДөзС№РЕәЕЈ¬Цч·ЕҙуЖчКдіц°Ъ·щОӘ200 mVpЈӯpЎЈ КдіцКэҫЭөДСЫНјЦРРДЙПЖ«Фј60 mVЈ¬ХвКЗТтОӘІвКФІЙУГөҘ¶ЛКдіцЎЈЛ«¶ЛКдіцКұОЮҙЛПЦПуЎЈ  7 Ҫб Уп ұҫОДҪйЙЬБЛІЙУГ0Ј®35ҰМmCMOS№ӨТХКөПЦУГУЪSDHПөНіSTM-16ЛЩВКј¶№вҪУКХ»ъөДЗ°ЦГ·ЕҙуЖчөДЙијЖЎЈөзВ·ДЈДвҪб№ыәН¶ФРҫЖ¬ІвКФҪб№ыБоИЛВъТвЈ¬ЧјұёЧцУЎЛўөзВ·°е¶ФЖдҪшТ»ІҪІвКФЈ¬ІўҪшРРУЕ»ҜёДҪшЎЈ |

НшУСЖАВЫ