ЩфЦЕЕчТЗАхПЙИЩШХЩшМЦ

ЗЂВМЪБМфЃК2010-8-4 09:55

ЗЂВМепЃКlavida

|

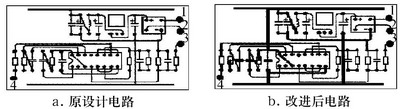

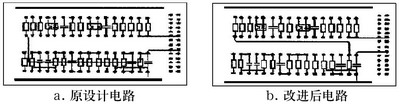

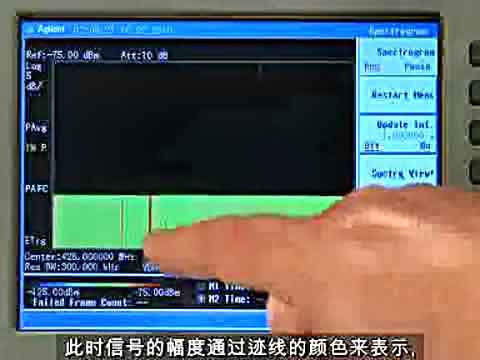

ЫцзХЭЈаХММЪѕЕФЗЂеЙ,ЮоЯпЩфЦЕЕчТЗММЪѕдЫгУдНРДдНЙу,ЦфжаЕФЩфЦЕЕчТЗЕФадФмжИБъжБНггАЯьећИіВњЦЗЕФжЪСП,ЩфЦЕЕчТЗгЁжЦЕчТЗАх( PCB)ЕФПЙИЩШХЩшМЦЖдгкМѕаЁЯЕЭГЕчДХаХЯЂЗјЩфОпгаживЊЕФвтвхЁЃЩфЦЕЕчТЗPCBЕФУмЖШдНРДдНИп, PCBЩшМЦЕФКУЛЕЖдПЙИЩШХФмСІгАЯьКмДѓ,ЭЌвЛЕчТЗ,ВЛЭЌЕФPCBЩшМЦНсЙЙ,ЦфадФмжИБъЛсЯрВюКмДѓЁЃЕчДХИЩШХаХКХШчЙћДІРэВЛЕБ,ПЩФмдьГЩећИіЕчТЗЯЕЭГЕФЮоЗЈе§ГЃЙЄзї,вђДЫШчКЮЗРжЙКЭвжжЦЕчДХИЩШХ,ЬсИпЕчДХМцШнад,ОЭГЩЮЊЩшМЦЩфЦЕЕчТЗPCBЪБЕФвЛИіЗЧГЃживЊЕФПЮЬтЁЃ ЕчДХМцШнадEMCЪЧжИЕчзгЯЕЭГдкЙцЖЈЕФЕчДХЛЗОГжаАДееЩшМЦвЊЧѓФме§ГЃЙЄзїЕФФмСІЁЃЕчзгЯЕЭГЫљЪмЕФЕчДХИЩШХВЛНіРДздЕчГЁКЭДХГЁЕФЗјЩф,вВгаЯпТЗЙЋЙВзшПЙЁЂЕМЯпМфёюКЯКЭЕчТЗНсЙЙЕФгАЯьЁЃдкбажЦЩшМЦЕчТЗЪБ,ЯЃЭћЩшМЦЕФгЁжЦЕчТЗАхОЁПЩФмВЛвзЪмЭтНчИЩШХЕФгАЯь,ЖјЧввВОЁПЩФмаЁЕиИЩШХгАЯьБ№ЕФЕчзгЯЕЭГЁЃ ЩшМЦгЁжЦАхЪзвЊЕФШЮЮёЪЧЖдЕчТЗНјааЗжЮі,ШЗЖЈЙиМќЕчТЗЁЃетОЭЪЧвЊЪЖБ№ФФаЉЕчТЗЪЧИЩШХдД,ФФаЉЕчТЗЪЧУєИаЕчТЗ,ХЊЧхИЩШХдДПЩФмЭЈЙ§ЪВУДТЗОЖИЩШХУєИаЕчТЗЁЃЩфЦЕЕчТЗЙЄзїЦЕТЪИп,ИЩШХдДжївЊЪЧЭЈЙ§ЕчДХЗјЩфРДИЩШХУєИаЕчТЗ,вђДЫЩфЦЕЕчТЗPCBАхПЙИЩШХЩшМЦЕФФПЕФЪЧМѕаЁPCBАхЕФЕчДХЗјЩфКЭPCB АхЩЯЕчТЗжЎМфЕФДЎШХЁЃ 1 ЩфЦЕЕчТЗАхЩшМЦ 1. 1 дЊЦїМўЕФВМОж гЩгкSMTвЛАуВЩгУКьЭтТЏШШСїКИРДЪЕЯждЊЦїМўЕФКИНг,вђЖјдЊЦїМўЕФВМОжгАЯьЕНКИЕуЕФжЪСП,НјЖјгАЯьЕНВњЦЗЕФГЩЦЗТЪЁЃЖјЖдгкЩфЦЕЕчТЗPCBЩшМЦЖјбд, ЕчДХМцШнадвЊЧѓУПИіЕчТЗФЃПщОЁСПВЛВњЩњЕчДХЗјЩф,ВЂЧвОпгавЛЖЈЕФПЙЕчДХИЩШХФмСІ,вђДЫдЊЦїМўЕФВМОжвВгАЯьЕНЕчТЗБОЩэЕФИЩШХМАПЙИЩШХФмСІ,жБНгЙиЯЕЕНЫљЩшМЦЕчТЗЕФадФмЁЃЙЪдкНјааЩфЦЕЕчТЗPCB ЩшМЦЪБГ§СЫвЊПМТЧЦеЭЈPCBЩшМЦЪБЕФВМОжЭт,жївЊЛЙаыПМТЧШчКЮМѕаЁЩфЦЕЕчТЗжаИїВПЗжжЎМфЕФЯрЛЅИЩШХЁЂШчКЮМѕаЁЕчТЗБОЩэЖдЦфЫћЕчТЗЕФИЩШХвдМАЕчТЗБОЩэЕФПЙИЩШХФмСІЁЃ ИљОнОбщ,ЩфЦЕЕчТЗаЇЙћЕФКУЛЕВЛНіШЁОігкЩфЦЕЕчТЗАхБОЩэЕФадФмжИБъ,КмДѓВПЗжЛЙШЁОігкгыCPUДІРэАхМфЕФЯрЛЅгАЯь,вђДЫдкНјааPCBЩшМЦЪБ,КЯРэВМОжЯдЕУгШЮЊживЊЁЃВМОжЕФзмддђЪЧдЊЦїМўгІОЁПЩФмЭЌвЛЗНЯђХХСа,ЭЈЙ§бЁдёPCBНјШыШлЮ§ЯЕЭГЕФЗНЯђРДМѕЩйЩѕжСБмУтКИНгВЛСМЕФЯжЯѓ;ИљОнОбщдЊЦїМўМфзюЩйвЊга 0.5mmЕФМфОрВХФмТњзудЊЦїМўЕФШлЮ§вЊЧѓ,ШєPCBАхЕФПеМфдЪаэ,дЊЦїМўЕФМфОргІОЁПЩФмПэЁЃЖдгкЫЋУцАхвЛАугІЩшМЦвЛУцЮЊSMDМАSMCдЊМў,СэвЛУцдђЮЊЗжСЂдЊМўЁЃ ВМОжжагІзЂвт : 1)ЪзЯШШЗЖЈгыЦфЫћPCB АхЛђЯЕЭГЕФНгПкдЊЦїМўдкPCBАхЩЯЕФЮЛжУ,БиаызЂвтНгПкдЊЦїМўМфЕФХфКЯЮЪЬт(МгдЊЦїМўЕФЗНЯђЕШ) ; 2)вђЮЊеЦЩЯгУЦЗЕФЬхЛ§ЖМКмаЁ,дЊЦїМўМфХХСаКмНєДе,вђДЫЖдгкЬхЛ§НЯДѓЕФдЊЦїМў,БиаыгХЯШПМТЧ,ШЗЖЈГіЯргІЮЛжУ,ВЂПМТЧЯрЛЅМфЕФХфКЯЮЪЬт; 3)ШЯецЗжЮіЕчТЗНсЙЙ,ЖдЕчТЗНјааЗжПщДІРэ(МгИпЦЕЗХДѓЕчТЗЁЂЛьЦЕЕчТЗМАНтЕїЕчТЗЕШ) ,ОЁПЩФмНЋЧПЕчаХКХКЭШѕЕчаХКХЗжПЊ,НЋЪ§зжаХКХЕчТЗКЭФЃФтаХКХЕчТЗЗжПЊ,ЭъГЩЭЌвЛЙІФмЕФЕчТЗгІОЁСПАВХХдквЛЖЈЕФЗЖЮЇжЎФк,ДгЖјМѕаЁаХКХЛЗТЗУцЛ§;ИїВПЗжЕчТЗЕФТЫВЈЭјТчБиаыОЭНќСЌНг,етбљВЛНіПЩвдМѕаЁЗјЩф,ЖјЧвПЩвдМѕЩйБЛИЩШХЕФЛњТЪ,ЬсИпЕчТЗЕФПЙИЩШХФмСІ; 4)ИљОнЕЅдЊЕчТЗдкЪЙгУжаЖдЕчДХМцШнадУєИаГЬЖШВЛЭЌНјааЗжзщЁЃЖдгкЕчТЗжавзЪмИЩШХВПЗжЕФдЊЦїМўдкВМОжЪБЛЙгІОЁСПБмПЊИЩШХдД(БШШчРДздЪ§ОнДІРэАхЩЯCPUЕФИЩШХЕШ) ЁЃ 1. 2 ВМЯп дкЛљБОЭъГЩдЊЦїМўЕФВМОжКѓ,ОЭПЩПЊЪМВМЯпСЫЁЃВМЯпЕФЛљБОддђЮЊ:дкзщзАУмЖШаэПЩЧщПіЯТ,ОЁСПбЁгУЕЭУмЖШВМЯпЩшМЦ,ВЂЧваХКХзпЯпОЁСПДжЯИвЛжТ,гаРћгкзшПЙЦЅХфЁЃ ЖдгкЩфЦЕЕчТЗ,аХКХЯпЕФзпЯђЁЂПэЖШЁЂЯпМфОрЕФВЛКЯРэЩшМЦ,ПЩФмдьГЩаХКХДЋЪфЯпжЎМфЕФНЛВцИЩШХ;СэЭт,ЯЕЭГЕчдДздЩэЛЙДцдкдыЩљИЩШХ,ЫљвддкЩшМЦЪБЦЕЕчТЗPCBЪБвЛЖЈвЊзлКЯПМТЧ,КЯРэВМЯпЁЃВМЯпЪБ,ЫљгазпЯпгІдЖРыPCBАхЕФБпПђ2 mmзѓгв,вдУтPCBАхжЦзїЪБдьГЩЖЯЯпЛђгаЖЯЯпЕФвўЛМЁЃ ЕчдДЯпвЊОЁПЩФмПэ,вдМѕЩйЛЗТЗЕчзш,ЭЌЪБЪЙЕчдДЯпЁЂЕиЯпЕФзпЯђКЭЪ§ОнДЋЕнЕФЗНЯђвЛжТ,вдЬсИпПЙИЩШХФмСІ;ЫљВМаХКХЯпгІОЁПЩФмЖЬ,ВЂОЁСПМѕЩйЙ§ПзЪ§ФП;ИїдЊЦїМўМфЕФСЌЯпдНЖЬдНКУ,вдМѕЩйЗжВМВЮЪ§КЭЯрЛЅМфЕФЕчДХИЩШХ;ЖдВЛЯрШнЕФаХКХЯпгІОЁСПЯрЛЅдЖРы,ЧвОЁСПБмУтЦНаазпЯп,Жјдке§ЗДСНУцЕФаХКХЯпгІЯрЛЅДЙжБ;ВМЯпЪБдкашвЊЙеНЧЕФЕиЗНгІвд135ЁуНЧЮЊвЫ,БмУтЙежБНЧЁЃ ВМЯпЪБгыКИХЬжБНгЯрСЌЕФЯпЬѕВЛвЫЬЋПэ,зпЯпгІОЁСПРыПЊВЛЯрСЌЕФдЊЦїМў,вдУтЖЬТЗ;Й§ПзВЛвЫЛдкдЊЦїМўЩЯ,ЧвгІОЁСПдЖРыВЛЯрСЌЕФдЊЦїМў,вдУтдкЩњВњжаГіЯжащКИЁЂСЌКИЁЂЖЬТЗЕШЯжЯѓЁЃдкЩфЦЕЕчТЗPCBЩшМЦжа,ЕчдДЯпКЭЕиЯпЕФе§ШЗВМЯпЯдЕУгШЦфживЊ,КЯРэЕФЩшМЦЪЧПЫЗўЕчДХИЩШХЕФзюживЊЕФЪжЖЮЁЃ PCBЩЯЯрЕБЖрЕФИЩШХдДЪЧЭЈЙ§ЕчдДКЭЕиЯпВњЩњЕФ,ЦфжаЕиЯпв§Ц№ЕФдыЩљИЩШХзюДѓЁЃЕиЯпШнвзаЮГЩЕчДХИЩШХЕФжївЊдвђдкгкЕиЯпДцдкзшПЙЁЃЕБгаЕчСїСїЙ§ЕиЯпЪБ,ОЭЛсдкЕиЯпЩЯВњЩњЕчбЙ,ДгЖјВњЩњЕиЯпЛЗТЗЕчСї,аЮГЩЕиЯпЕФЛЗТЗИЩШХЁЃЕБЖрИіЕчТЗЙВгУвЛЖЮЕиЯпЪБ,ОЭЛсаЮГЩЙЋЙВзшПЙёюКЯ,ДгЖјВњЩњЫљЮНЕФЕиЯпдыЩљЁЃ вђДЫ,дкЖдЩфЦЕЕчТЗPCBЕФЕиЯпНјааВМЯпЪБгІИУзіЕН: 1)ЖдЕчТЗНјааЗжПщДІРэЪБ,ЩфЦЕЕчТЗЛљБОЩЯПЩЗжГЩИпЦЕЗХДѓЁЂЛьЦЕЁЂНтЕїЁЂБОеёЕШВПЗж,вЊЮЊИїИіЕчТЗФЃПщЬсЙЉвЛИіЙЋЙВЕчЮЛВЮПМЕу,МДИїФЃПщЕчТЗИїздЕФЕиЯп,етбљаХКХОЭПЩвддкВЛЭЌЕФЕчТЗФЃПщжЎМфДЋЪфЁЃШЛКѓ,ЛузмгкЩфЦЕЕчТЗPCB НгШыЕиЯпЕФЕиЗН,МДЛузмгкзмЕиЯпЁЃгЩгкжЛДцдквЛИіВЮПМЕу,вђДЫУЛгаЙЋЙВзшПЙёюКЯДцдк,ДгЖјвВОЭУЛгаЯрЛЅИЩШХЮЪЬт; 2)Ъ§зжЧјгыФЃФтЧјОЁПЩФмвдЕиЯпНјааИєРы,ВЂЧвЪ§зжЕигыФЃФтЕивЊЗжРы,зюКѓНггкЕчдДЕи; 3)дкИїВПЗжЕчТЗФкВПЕФЕиЯпвВвЊзЂвтЕЅЕуНгЕиддђ,ОЁСПМѕаЁаХКХЛЗТЗУцЛ§,ВЂгыЯргІЕФТЫВЈЕчТЗЕФЕиЯпОЭНќЯрНг; 4)дкПеМфдЪаэЕФЧщПіЯТ,ИїФЃПщжЎМфзюКУФмвдЕиЯпНјааИєРы,ЗРжЙЯрЛЅжЎМфЕФаХКХёюКЯаЇгІЁЃ 2 ЪЕбщВтЪд ЯТУцМИИіЪЕбщВтЪдЪТР§,ЫЕУїСЫВЛЭЌдвђДјРДЕФИЩШХМАЦфЪЕМЪЕФНтОіАьЗЈЁЃ 2. 1 ЕчдДЯпКЭЕиЯпДјРДЕФИЩШХ ЭМ1ШЁздФГИпбЙПижЦБЃЛЄPCBЕФВПЗжЕчТЗЁЃЭМ1aЮЊдЩшМЦЕчТЗЁЃгЩгкЕчдДЯпКЭЕиЯпЕФгЁжЦЕМЯпПэЖШЬЋЯИ,ЕчТЗдкЙЄзїЪБОжЪмЭтНчИЩШХ;ЭМ1bЪЧОЙ§ИФНјКѓЕФЕчТЗ,ЦфЕчдДЯпКЭЕиЯпМгДжжС5 mm,НтОіСЫЕчТЗЕФИЩШХЮЪЬтЁЃ  ЭМ1ФГИпбЙПижЦБЃЛЄPCBЕФВПЗжЕчТЗ 2. 2 дЊЦїМўВМОжВЛКЯРэДјРДЕФИЩШХ ЭМ2ШЁздФГРзДяЗЂЩфЛњДХГЁПижЦБЃЛЄPCBЕФВПЗжЕчТЗЁЃжиаТВМОждЊЦїМўКѓИФНјЕФPCB ЕчТЗ(ШчЭМ2b)НЯИФНјЧАЕФPCB ЕчТЗ(ШчЭМ2a)дкПЙИЩШХадФмЩЯгаКмДѓЕФИФЩЦЁЃ  ЭМ2ФГРзДяЗЂЩфЛњДХГЁПижЦБЃЛЄPCBЕФВПЗжЕчТЗ 2. 3 ВМЯпВЛКЯРэДјРДЕФИЩШХ ЭМ3ШЁздФГРзДяCFAЕчдДПижЦБЃЛЄPCBЕФВПЗжЕчТЗЁЃЭМ3aЮЊдЩшМЦЕчТЗЁЃгЩгкВМЯпЪБНЋИпбЙШЁбљаХКХЯпВМгкБеЛЗШЁбљЛиТЗжа,ЪЙБеЛЗШЁбљЕчТЗдкЙЄзїЪБвзЪмЭтНчЕФИЩШХ,дьГЩОГЃЮѓБЈЙ§бЙЙЪеЯ;ЖјЭМ3bЪЧОЙ§ИФНјКѓЕФPCBЕчТЗ,гЩгкБмПЊСЫИпбЙШЁбљаХКХЯпДјРДЕФИЩШХ,ИФНјКѓЕФPCBЕчТЗЙЄзїПЩППЮШЖЈЁЃ  ЭМ3ФГРзДяCFAЕчдДПижЦБЃЛЄPCBЕФВПЗжЕчТЗ 3 Нсгя ЩфЦЕЕчТЗPCBЩшМЦЕФЙиМќдкгкШчКЮМѕЩйЗјЩфФмСІвдМАШчКЮЬсИпПЙИЩШХФмСІ,КЯРэЕФВМОжгыВМЯпЪЧЩшМЦЪБЦЕЕчТЗPCBЕФБЃжЄЁЃЮФжаЫљЪіЗНЗЈгаРћгкЬсИпЩфЦЕЕчТЗPCBЩшМЦЕФПЩППад,НтОіКУЕчДХИЩШХЮЪЬт,НјЖјДяЕНЕчДХМцШнЕФФПЕФЁЃ |

ЭјгбЦРТл