以DDS为参考的PLL在现代电台设计中的应用

发布时间:2010-8-3 11:28

发布者:lavida

|

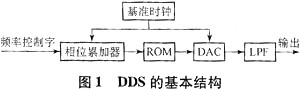

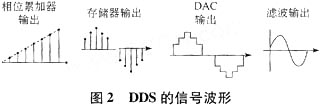

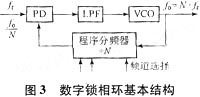

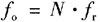

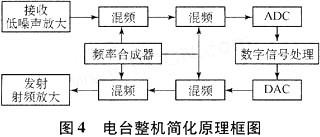

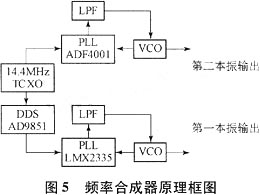

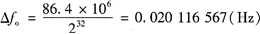

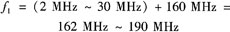

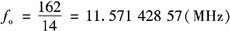

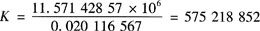

现代电台的特点主要是多用途、多制式、多频段。随着数字技术的发展,中频以下通常采用数字化处理,中频到射频用混频器进行频率变换。对频率合成器的设计提出了更高的要求,例如分辨率、转换速度、工作频率范围、相位噪声等指标。PLL(锁相环)频率合成通过锁相环完成频率的加、减、乘、除运算。该方法结构简单、便于集成,且输出频率高、频谱纯度高,目前使用比较广泛,但存在高分辨率和快转换速度之间的矛盾,一般只能用于大步进频率合成技术中。DDS(直接数字合成)是近年来迅速发展起来的一种新的频率合成方法。这种方法简单可靠、控制方便,且具有很高的频率分辨率和转换速度,缺点是输出频率不能太高。如果把两者结合起来,用DDS的输出作为PLL的参考信号,就能满足现代电台对频率合成器的设计要求。本文将介绍DDS和PLL的工作原理,并结合一电台(工作频率2 MHz~500 MHz)的设计,给出DDS做参考的PLL频率合成器的设计方案。 1 DDS的结构及工作原理 DDS的基本结构由参考时钟、相位累加器、ROM、DAC(数模转换器)和LPF(低通滤波器)组成,见图1。  DDS的工作原理是:在参考时钟fr的控制下,频率控制字K由累加器得到相应的相位数据,把此数据作为取样地址,来寻址正弦ROM表进行相位-幅度变换,输出不同的幅度编码;再经DAC得到相应的阶梯波;最后经LPF对阶梯波进行平滑处理,即可得到由频率控制字决定的连续变化的输出正弦波。见图2。  DDS的输出频率fo、参考时钟频率fr、相位累加器长度N以及频率控制字K之间的关系为:  DDS的频率分频率为:  由于DDS的最大输出频率受奈斯特取样定理限制,所以fmax=f/2。 2 PLL的结构及工作原理 设计中通常采用数字锁相频率合成法,其基本结构由参考时钟fr、VCO(压控振荡器)、程序分频器(÷N)、PD(鉴相器)、LPF等组成。见图3。  当PLL达到稳定状态后,若输入信号为一固定频率的正弦波,则VCO的输出信号频率经程序分频器分频后与输入信号频率相等,它们之间的相位差为一常值。这种状态为环路的锁定状态。此时有:  3 基于DDS的频率合成器的设计 3.1 电台整机方案 该电台工作频率范围为2 MHz~500 MHz,具有调频、调幅(包括单边带)、调相(QPSK)等功能,还可工作于跳扩频方式。在短波频段(2 MHz~30 MHz)要求调谐间隔为10 Hz,其余频段为100 Hz。设计中采用二次变频方案,第一中频取160MHz,第二中频取10.7 MHz。当然,对于160 MHz附近频段,只采用一次变频至10.7 MHz。第二中频以下采用数字化处理。简化原理框图如图4所示。  3.2 频率合成器方案 频率合成器须输出第一本振、第二本振两路信号。第二本振为固定频率170.7 MHz,选用ADF4001 PLL电路,参考时钟采用14.4 MHz温度补偿晶体振荡器,环路鉴相频率100 kHz。第一本振信号是由14.4 MHzTCXO(温度补偿晶体振荡器)经DDS频率合成器(选用AD9851)产生参考信号,再由PLL电路锁定在工作频率上。原理框图如图5所示。  3.2.1 器件的选择 选用Analog Devices公司的DDS芯片AD9851,该芯片的最高工作时钟为180 MHz,内部除了完整的高速DDS外,还集成了时钟6倍频器和一个高速比较器。本方案使用14.4 MHz TCXO,经6倍频器产生86.4 MHz参考时钟频率,DDS输出的频率分辨率为:  PLL选用National Semiconductor公司的双频率合成器电路LMX2335,其最高工作频率1.1 GHz。 3.2.2 工作频率计算 以短波频段(2 MHz~30 MHz)为例,第一本振输出频率为:  考虑到环路的锁定时间,LMX2335的鉴相频率取200 kHz左右,对于较大范围调整频率,可改变LMX233的程序分频数N,例如:162 MHz~172 MHz,N取14×60=840;172 MHz~182 MHz,N取15×60=900;182 MHz~190 MHz,N取16×60=960。LMX233的参考分频数R固定为60。DDS输出频率控制在11 MHz~13 MHz,可在小范围内调整PLL的输出频率。下面以输出162 MHz为例说明DDS频率控制字K的算法。 DDS输出频率为:  频率控制字K为:  在162 MHz~172 MHz频率范围内,频率误差=0.020 116 567×14≈0.28 Hz。 3.2.3 应注意的问题 DDS的输出应经过一中心频率为12 MHz、带宽为2 MHz的带通滤波器。具体设计可使用Agilent ADS软件。该电路是高速数模混合电路,在制作印制电路板时,一定要注意数模干扰问题。为此,印制电路板一定要使用4层板。在进行电路布局时,将数字部分和模拟部分分开;将电源层分为数字电源和模拟电源;将地层分为数字地和模拟地。每个有源器件的电源都要加去耦电容,并且尽可能地靠近电源输入处,以帮助滤除高频噪声。 4 结束语 目前频率合成技术主要有直接频率合成、PLL频率合成、DDS这3种形式。由于PLL方式的频率合成器存在高分辨率和快转换速度之间的矛盾,而DDS方式的输出带宽又有限,因此在设计工作频率宽、调协精度高的频率合成器时,这两种方式均不能满足技术要求。但是,采用DDS+PLL方式,可以满足高精度和宽频带的需要,其实现的难点是如何提高合成器输出频谱纯度。在实际印制电路板制作中,DDS的良好接地和合理布线非常有助于系统设计的实现。 |

网友评论