ЮЂДІРэЦїЪЕЪБЪБжгаОЦЌMM58167BдРэгыгІгУ

ЗЂВМЪБМфЃК2010-8-3 11:24

ЗЂВМепЃКlavida

|

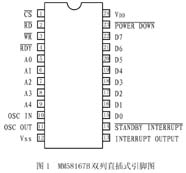

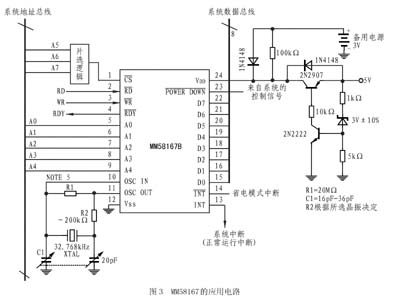

1. ИХЪі MM58167BзїЮЊзмЯпаЭЮЂДІРэЯЕЭГжаЕФЪЕЪБЪБжгдДЃЌЦфФкВПАќРЈвЛИіПЩбАжЗЕФЪЕЪБМЦЪ§ЦїЁЂ56 bitЦЌФкRAMКЭСНИіЪфГіжаЖЯЃЌЖјЧвPOWER DOWNв§НХЕФгааЇаХКХПЩЪЙаОЦЌНјШыЪЁЕчЙЄзїФЃЪНЁЃИУаОЦЌЕФЪБМфЛљзМЪЧвЛИі32.768kHzЕФОЇеёЁЃЦфЬиЕуШчЯТЃК ЁёгыЮЂДІРэЦїМцШн(8 bitЪ§ОнзмЯп); ЁёОпгаДгКСУыЕНдТЕФМЦЪ§ЦїЃЛ Ёё56 bitФкВПRAMПЩгыЪЕЪБЪБМфБШНЯЃЛ Ёё2ИіжаЖЯЪфГіПЩВњЩњ8жжжаЖЯаХКХЃЛ ЁёPOWER DOWNЪфШыПЩЪЙЫљгаЪфШыЪфГіЪЇаЇЖјжЛСєвЛИіSTANDBYжаЖЯЃЛ ЁёзДЬЌЮЛПЩжИЪОдквЛИіЖСжмЦкжаЪЧЗёГіЯжМЦЪ§ИќаТЃЛ Ёё4ФъШеРњ(ЮоШђФъ)ЃЛ Ёё24аЁЪБЪБжгЃЛ ЁёВЩгУ24НХDIPЗтзА(ШчЭМ1ЫљЪО)ЁЃ   2. ЙІФмФЃПщНщЩм 2.1 ЪЕЪБЪБжгМЦЪ§ ЪЕЪБЪБжгЕФУПИіМЦЪ§ЦїЗжГЩЪЎЮЛКЭИіЮЛСНИіЪ§зжЃЌУПИіЪ§зжгЩ4 bitзщГЩBCDТы(МћБэ1)ЃЌШЮКЮВЛгУЕФbitдкЖСЪББЃГжТпМЁА0ЁБЃЌдкаДЪББЛКіТдЁЃШЮКЮВЛгУЕФbitВЛВЮгыBCDТыЕФКЯГЩЁЃБШШчаЁЪБМЦЪ§ЦїЕФЪЎЮЛВЛгІГЌЙ§2ЃЌЙЪжЛаш2 bitБэЪОЃЌЖјЦфгр2 bitПеЯаЃЌгУЖЬЛЎЯп(Ѓ)БэЪОЁЃ  МЦЪ§ЦїЕФПЩбАжЗВПЗжЪЧДгКСУыЕНдТЁЃМЦЪ§ЦїБОЩэЪЧвЛИіТіЖЏМЦЪ§ЦїЃЌЙЄзїгк4.5VвдЩЯЪБЕФТіЖЏбгЪБаЁгк60ІЬs(ЙЄзїгк2.2VЪБаЁгк300ІЬs)ЁЃ 2.2 ЦЌФкRAM ЦЌФкЕФ56 bitRAMПЩзїЮЊвЛАуЕФЪ§ОнДцДЂЦїЪЙгУЃЌвВПЩвдЫјДцгыЪЕЪБЪБжгБШНЯЕФБШНЯжЕЁЃУПЕБЪЕЪБЪБжгЕФЕБЧАжЕгыRAMжаЫјДцЕФЩшжУжЕБШНЯЯрЕШЪБОЭПЩвдВњЩњБЈОЏжаЖЯЁЃЦфжажЛгаКСУыЕФИіЮЛКЭаЧЦкЕФЪЎЮЛВЛВЮМгБШНЯ(МЦЪ§ЦїжавВЮДгУЕНЃЌШчБэ1ЫљСа)ЁЃШчЙћRAMжаФГИіBCDТыЕФзюИп2ИігааЇЮЛБЛжУЮЊЁА1ЁБЃЌдђШЯЮЊИУЮЛзмЯрЕШЖјВЛВЮгыБШНЯЃЌМДБЛЦСБЮЕєЁЃвђДЫЩшжУБЈОЏжаЖЯЕФЙцТЩЮЊЃКЗВЪЧБШжИЖЈЪБМфЕЅЮЛИпЕФЮЛЃЌЩшжУГЩ0CH(МД1100BЃЌзюИп2ЮЛЮЊЁА1ЁБ)ЃЌЖјБШжИЖЈЪБМфЕЅЮЛЕЭЕФЮЛЩшЮЊЁА00HЁБЁЃБШШчЃЌЯЃЭћУПЬьЕФЩЯЮч10ЁУ15ВњЩњБЈОЏжаЖЯЃЌдђБШаЁЪБИпЕФЪБМфЕЅЮЛ(аЧЦкЁЂШеЦкЁЂдТ)ЖМЩшЮЊ0CHЃЌЖјБШЗжжгЕЭЕФЪБМфЕЅЮЛ(УыЁЂАйЗжУыЁЂКСУы)ЖМЩшГЩ00HЁЃ 2.3 жаЖЯКЭБШНЯЦї ИУаОЦЌЙВга2ИіжаЖЯЪфГіЁЃЕквЛИіЪЧв§НХINTERRUPT OUTPUT(жаЖЯгааЇЪБЪфГіИпЕчЦН)ЃЌИУв§НХОБрГЬПЩЪфГі8жжРраЭЕФжаЖЯаХКХЃЌМД10HzЁЂ1HzЁЂУПЗжжгвЛДЮЁЂУПаЁЪБвЛДЮЁЂУПЬьвЛДЮЁЂУПаЧЦквЛДЮЁЂУПдТвЛДЮЛђЦЌФкRAMЩшжУЕФЪБМфгыЪБжгМЦЪ§ЦїЪБМфБШНЯЯрЕШЪБВњЩњжаЖЯЁЃЮЊСЫдЪаэФГжжРраЭЕФжаЖЯЃЌжЛашЭљжаЖЯПижЦМФДцЦїЕФЯргІЮЛаДЁА1ЁБЃЌЕБвЛИіЛђИќЖрЮЛБЛжУЁА1ЁБЃЌИУЮЛЖдгІЕФМЦЪ§ЦївчГіЗСуЪБЃЌНЋжУЮЛжаЖЯзДЬЌМФДцЦїЕФЯргІЮЛВЂВњЩњжаЖЯ(ЪЙжаЖЯЪфГіНХГіЯжИпЕчЦН)ЃЌжЛвЊЖСШЁжаЖЯзДЬЌМФДцЦїОЭПЩвдЪЖБ№жаЖЯРраЭВЂИДЮЛжаЖЯЃЌШчЭМ2ЫљЪОЁЃ ЕкЖўИіжаЖЯЪфГіЪЧв§НХSTANDBY INTERRUPT(ТЉМЋПЊТЗЃЌЕЭЕчЦНгааЇ)ЃЌжЛвЊЦЌФкRAMжаЩшжУЕФЪБМфгыМЦЪ§ЦїБШНЯЮЧКЯЃЌВЂДЫжаЖЯвбОдЪаэ(ЭљЕижЗ16HЕФD0ЮЛаДЁА1ЁБдЪаэЃЌаДЁА0ЁБНћжЙ)ЃЌМДПЩВњЩњИУжаЖЯЁЃ 2.4 ЪЁЕчЙЄзїФЃЪН POWER DONWЪфШыв§НХЪЕМЪЩЯЪЧЕкЖўИіЦЌбЁаХКХЁЃЫќПЩЪЙЫљгаЪфШыЪфГіЪЇаЇЖјжЛСєSTANDBYжаЖЯЃЌЕБв§НХPOWER DOWNЪфШыЕЭЕчЦНЪБЃЌвЧЦїНЋВЛЯьгІШЮКЮЦЌЭтаХКХЃЌЫќЛсБЃДцЪБМфжЕВЂДђПЊSTANDBYжаЖЯ(БиаыдкЪфШыЕЭЕчЦНЧАБрГЬКУ)ЁЃдкVDDЧаЛЛЕНБИгУЕчдДЛђЪЁЕчФЃЪНЧАЃЌв§НХPOWER DOWNгІЮЌГжзюЩй1ІЬsЕФЕЭЕчЦНЃЌЖјЧвдкЧаЛЛVDDКЭPOWER DOWNв§НХзДЬЌЪБЃЌЫљгаЪфШыНХЕФЕчЦНОљгІДІдкгааЇЗЖЮЇФк(VSSЃ0.3VЁЋVDDЃЋ0.3V)ЁЃ 2.5 МЦЪ§ЦїЁЂRAMЕФИДЮЛКЭЦєЖЏУќСю ЭљЕижЗ12HКЭ13HаДШыFFHПЩвдЗжБ№ИДЮЛМЦЪ§ЦїКЭЦЌФкRAMЃЌЖјЦєЖЏУќСю(еыЖдЕижЗ15HЕФвЛИіаДТіГх)НЋЛсИДЮЛ1/1000УыЁЂ1/100УыЁЂ1/10УыЁЂУыЁЂ10УыМЦЪ§ЦїЃЌДЫУќСюгУРДЖдЪБжгОЋУмЦєЖЏЃЌЕБИУУќСюжДааЪБЃЌШчЙћУыМЦЪ§ЦїжЕДѓгк59ЃЌдђЗжМЦЪ§ЦїСЂПЬМг1ЃЌЗёдђЗжМЦЪ§ЦїжЕВЛЪмгАЯьЁЃ 2.6 зДЬЌЮЛ ЕижЗ14HЕФD0ЮЛЪЧвЛИізДЬЌЮЛЃЌУПЕБЖСШЁМЦЪ§ЦїЕФжЕЪБЗЂЩњМЦЪ§ЗзЊЃЌзДЬЌЮЛОЭЛсБЛжУЁА1ЁБЃЌШчЙћзДЬЌЮЛжУЁА1ЁБЃЌдђМЦЪ§жЕгІИУжиЖСЁЃЫљвддкУПДЮЖСМЦЪ§ЦїжЕЪБЖМгІНєИњЖСвЛДЮзДЬЌЮЛЃЌЖјЧвИУЖСШЁУќСюЛсЪЙзДЬЌЮЛИДЮЛЁЃ 2.7ВтЪдФЃЪН ЦЌбЁЯпКЭаДПижЦЯпБЃГжЕЭЕчЦНВЂЧвЕижЗЮЌГждк1FHЪБОЭНјШыВтЪдФЃЪНЃЌдкИУФЃЪНжаЃЌЪЎКСУыМЦЪ§ЦїЕФЪБжгЪфШыжБНгСЌНгЕН32.768kHzЃЌетбљПЩЪЙМЦЪ§ЦїгУБШе§ГЃдЫааЪБИќИпЕФЦЕТЪМЦЪ§ЃЌвдДяЕНВњЦЗЕїЪдЕФФПЕФЁЃ 3. ЕфаЭгІгУ ЭМ3ЮЊMM58167BЕФгІгУЕчТЗЃЌашвЊЫЕУїЕФЪЧЃЌMM58167BЕФ9НХКЭ10НХжЎМфгІгУЕиЯпИєПЊЃЌвдБмУтОЇеёЕФЙЄзїЪмЕижЗЯпЕФИЩШХЁЃ |

ЭјгбЦРТл