ИпЫйPCBЩшМЦШэМўallegro16.6АцБОдМЪјЙмРэНчУцНВНт

ЗЂВМЪБМфЃК2016-12-21 09:41

ЗЂВМепЃКkdyhdl

ЙиМќДЪЃК

ИпЫйPCBЩшМЦШэМў , allegro16.6АцБО

|

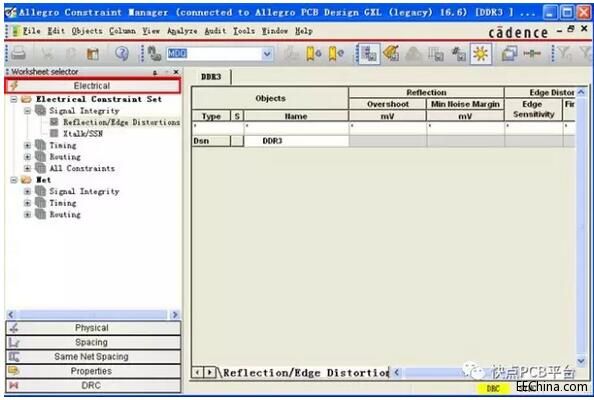

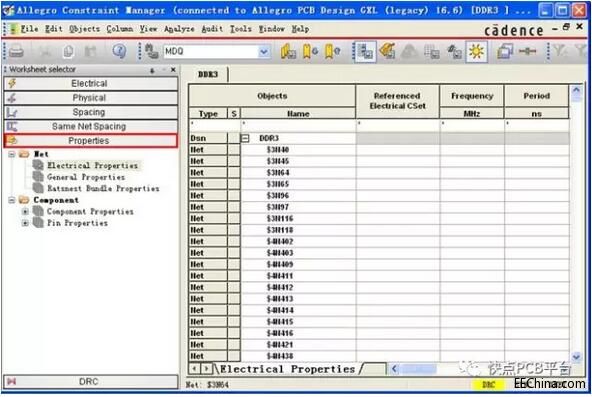

cadenceдМЪјЙмРэЦїдкPCBЩшМЦЙцдђЩшжУжаЪЧБиВЛПЩЩйЕФЃЌЫќвВГЦЮЊDRCМьВщЙцдђЃЌгУРДШЗЖЈЕчТЗАхЕФзпЯпЙцдђЪЧЗёЗћКЯPCBЩшМЦвЊЧѓЁЃБОНкжївЊЪЧИјДѓМвНщЩмдМЪјЙмРэЦїЕФ6ИіНчУцЁЃ ЪзЯШЃЌПЩвдЭЈЙ§ВЫЕЅSetup/constraints/Constraint ManagerЁЛђепЕуЛїЭМБъ 2016_12_20_1482200678_930859.jpgНјШыдМЪјЙмРэЦїЁЃ ЕчЦјЙцдђЩшжУНчУц 1

ElectricalЃКЕчЦјЙцдђЩшжУбЁЯюЃЌдкElectrical Constraint SetжаЩшжУВЛЭЌЕФЕчЦјЙцдђЃЌдкNetЯТНЋЧАУцЕФЙцдђИГгшашвЊЕФЭјТч ЮяРэЙцдђЩшжУНчУц 2

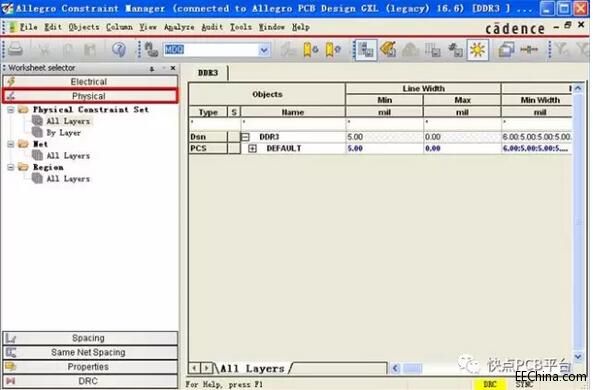

PhysicalЃКЮяРэЙцдђЩшжУбЁЯюЃЌдкPhysical Constraint SetжаЩшжУВЛЭЌЕФЮяРэЙцдђЃЌдкnetЯТНЋЧАУцЕФЙцдђИГгшашвЊЕФЭјТчЃЛЦфжаRegion ЪЧЧјгђЙцдђЃЌжївЊеыЖдBGAЁЂв§НХМфОраЁЁЂГіЯпУмЖШИпЕФЦїМўЃЌашЛцжЦвЛИіЧјгђПђВЂИГгшЧјгђЙцдђЃЌЧјгђФкЯпПэКЭМфОрЖМПЩФмаЁгкЧјгђЭтЃЌЮяРэЙцдђЯТФмЙЛИГгшЮяРэЙцдђЁЃ МфОрЙцдђЩшжУНчУц 3

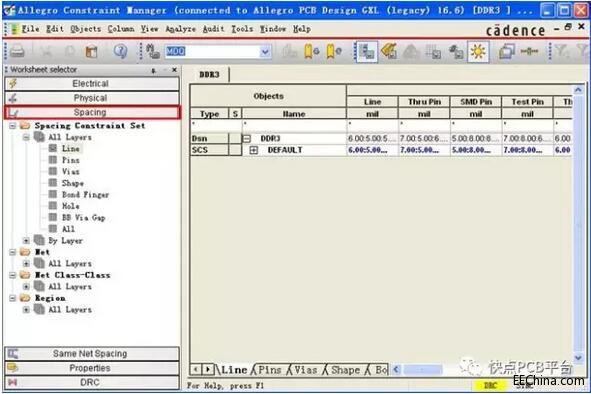

SpacingЃКМфОрЙцдђЩшжУбЁЯюЃЌдкSpacing Constraint SetжаЩшжУВЛЭЌЕФЮяРэЙцдђЃЌдкnetЯТНЋЧАУцЕФЙцдђИГгшашвЊЕФЭјТчЃЌNet Class-ClassЪЧЩшжУЭјТчРржЎМфЕФМфОрЃЌВЙГфЭјТчМфОржЎМфЕФВЛзуЁЃRegionжаПЩвдИГгшЧјгђМфОрЙцдђЁЃ ЭЌУћЭјТчМфОрЙцдђЩшжУНчУц 4

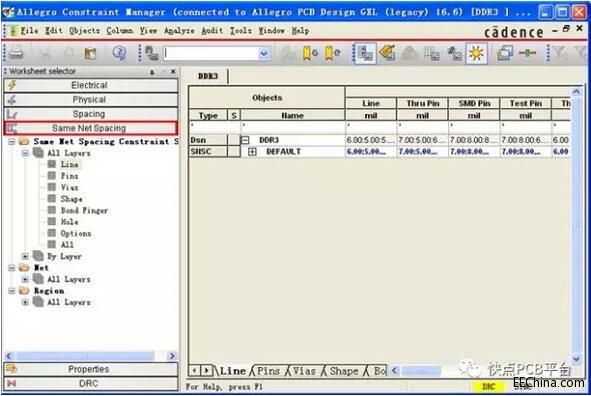

Same Net SpacingЃКЭЌУћЭјТчМфОрЩшжУбЁЯюЃЌМДвЛИіЭјТчБОЩэжЎМфЕФМфОрЃЌжївЊЪЧдкашвЊШЦЯпЪБдЫгУЁЃ ЪєадЩшжУНчУц 5

DRCНчУц 6

DRCЃКDRCДэЮЛВщПДбЁЯюЃЌФмЙЛВщПДВЛЭЌЙцдђЯТДэЮѓЕФЪ§СПКЭЮЛжУЃЌвдМАКЭДэЮѓЯрЙиЕФЙцдђдМЪјЬѕМўЁЃ ЖдИпЫйPCBЩшМЦШэМў cadence16.6АцБОдМЪјЙмРэЦїНчУцНјааНщЩмЭъБЯКѓЃЌЯТЦкМЬајЮЊДѓМвНщЩмгыЭјТчгаЙиЕФдМЪјгыЙцдђЕФНВНтЁЃ |

ЭјгбЦРТл