基于TLC2543设计的采集系统

发布时间:2010-7-30 13:40

发布者:lavida

|

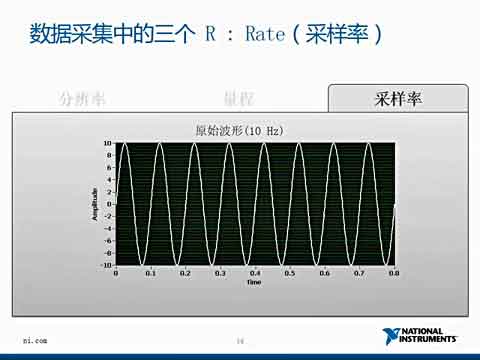

1 引言 实验和工程实际中我们要进行大量的数据处理。运用单片机采集系统能很好的解决这些问题。基本的采集系统一般由MCU,A/D,PC构成, MCU 是整个系统的核心,A/D是数据的源头,PC是数据的归宿地。A/D转换器的选择直接关系到采集精度是否理想。现在TLC2543这款A/D转换器运用很广泛。TLC2543是TI公司的12位串行模数转换器,使用开关电容逐次 逼近技术完成A/D转换过程。由于是串行输入结构,能够节省51系列单片机I/O资源;且价格适中,分辨率较高。 2 TLC2543的引脚排列及说明 (1) TLC2543的封装形式 TLC2543的封装形式:DB、DW或N封装以及FN封装,这两种封装的引脚的排列及说明见图1。  (2) TLC2543的简要工作过程 TLC2543的工作过程分为两个周期:I/O周期和转换周期。 a) I/O周期 I/O周期由外部提供的I/O CLOCK定义,延续8、12或16个时钟周期,决定于选定的输出数据长度。器件进入I/O周期后同时进行两种操作。 l在I/O CLOCK的前8个脉冲的上升沿,以MSB前导方式从DATA INPUT端输入8位数据流到输入寄存器。其中前4位为模拟通道地址,控制14通道模拟多路器从11个模拟输入和三个内部测电压中选通一路送到采样保持电路,该电路从第4个I/O CLOCK脉冲的下降沿开始对所选信号进行采样,直到最后一个I/O CLOCK脉冲的下降沿。I/O周期的时钟脉冲个数与输出数据长度(位数)同时由输入数据的D3、D2位选择为8、12或16。当工作于12或16位时,在前8个时钟脉冲之后,DATA INPUT无效。 l在DATA OUT端串行输出8、12或16位数据。当CS保持为低时,第一个数据出现在EOC的上升沿。若转换由CS控制,则第一个输出数据发生在CS的下降沿。这个数据串是前一次转换的结果,在第一个输出数据位之后的每个后续位均由后续的I/O时钟下降沿输出。 b) 转换周期 在I/O周期的最后一个I/O CLOCK下降沿之后,EOC变低,采样值保持不变,转换周期开始,片内转换器对采样值进行逐次逼近式A/D转换,其工作由与I/O CLOCK同步的内部时钟控制。转换完成后EOC变高,转换结果锁存在输出数据寄存器中,待下一个I/O周期输出。I/O周期和转换周期交替进行,从而可减小外部的数字噪声对转换精度的影响。 3 接口时序 可以用四种传输方法使TLC2543得到全12位分辩率,每次转换和数据传递可以使用12或16个时钟周期。 一个片选()脉冲要插到每次转换的开始处,或是在转换时序的开始处变化一次后保持为低,直到时序结束。 图2显示每次转换和数据传递使用16个时钟周期和在每次传递周期之间插入的时序,图3显示每次转换和数据传递使用16个时钟周期,仅在每次转换序列开始处插入一次时序。   4 硬、软件设计 4.1 硬件设计 MAX3232为RS-232收发器,简单易用,单+5V电源供电,仅需外接几个电容即可完成从TTL电平到RS-232电平的转换;AT89C52 为51系列的芯片,使用方便可靠。引脚排列如图4、图5所示。   硬件电路原理图如下图6所示:  在设计制作时要注意如下3个问题: (1) 电源去耦 当使用TLC2543这种12位A/D器件时,每个模拟IC的电源端必须用一个0.1μF的陶瓷电容连接到地,用作去耦电容。在噪声影响较大的环境中,建议每个电源和陶瓷电容端并一个10μF的钽电容,这样能够减小噪声的影响。 (2) 接地 对模拟器件和数字器件,电源的地线回路必须分开,以防止数字部分的噪声电流通过模拟地回路引入,产生噪声电压,从而对模拟信号产生干扰。所有的地线回路都有一定的阻抗,因此地线要尽可能宽或用地线平面,以减小阻抗,连线应当尽可能短,如果使用开关电源,则开关电源要远离模拟器件。 (3) 电路板布线 使用TLC2543时一定要注意电路板的布线,电路板的布线要确保数字信号和模拟信号隔开,模拟线和数字线特别是时钟信号线不能互相平行,也不能在TLC2543芯片下面布数字信号线。 4.2 软件编程 单片机程序主要包括串行数据采集模块“DATA_AD”和串行数据传输模块“RS232”,调试所用到的显示子程序在此略去。 TLC2543的通道选择和方式数据为8位,其功能为:D7、D6、D5和D4用来选择要求转换的通道,D7D6D5D4=0000时选择0通道,D7D6D5D4=0001时选择1通道,依次类推;D3和D2用来选择输出数据长度,本程序选择输出数据长度为12位,即D3D2=00或D3D2=10;D1,D0选择输入数据的导前位,D1D0=00选择高位导前。TLC2543在每次I/O周期读取的数据都是上次转换的结果,当前的转换结果在下一个I/O周期中被串行移出。第一次读数由于内部调整,读取的转换结果可能不准确,应丢弃。(这里只给出A/D程序) file://TLC2543/ A/D转换用程序用C51编写。 #define uchar unsigned char #define uintunsigned int file://==========AD/采样模块============// sbit CLOCK =P1^1; sbit D_IN=P1^2; sbit D_OUT =P1^3; sbit _CS=P1^4; uint read2543(uchar port) file://从/TLC2543读取采样值, file://形/参port是采样的通道号 { uint data ad;uint data i; uchar data al=0,ah=0; CLOCK=0; _CS=0; for(i=0;i5结束语 实际运行证明,用TLC2543芯片对数据进行采集预定的功能已经实现。同时用C51编写的程序以后有很好的移植性。 |

网友评论