»щУЪҰМC/OS-IIЗ¶ИлКҪІЩЧчПөНіөДTCSCКөСйҝШЦЖЖчЗ°ЦГөҘФӘЙијЖ

·ўІјКұјдЈә2010-7-30 13:39

·ўІјХЯЈәlavida

|

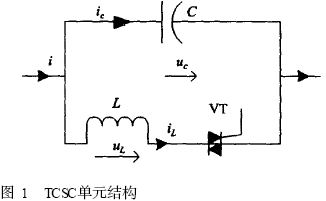

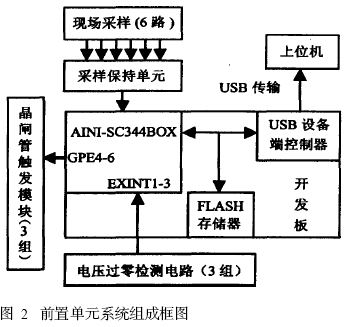

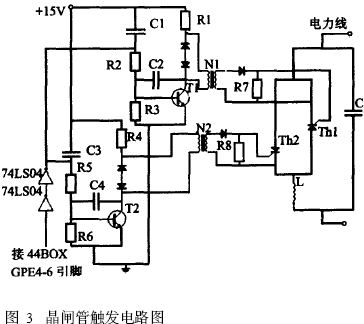

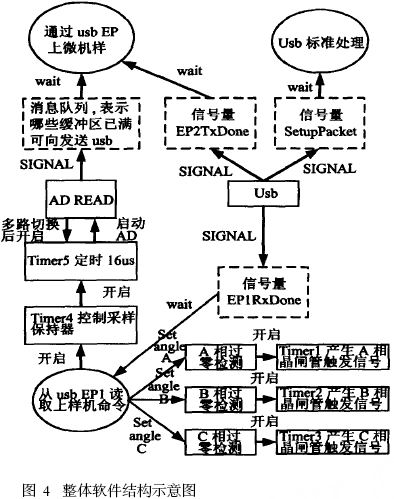

ҝЙҝШҙ®БӘІ№іҘ( TCSC) КЗИбРФҪ»БчКдөзПөНі( FACTS)ёЕДоМбіцәуөДөЪТ»ёцFACTSЧ°ЦГЎЈ УЙУЪTCSCЦұҪУҙ®ИлКдөзПЯВ·,ҝЙТФБ¬РшЎўҝмЛЩЎўҙу·¶О§өШөчҪЪПЯВ·Чиҝ№(ұҫЙнөДЧиҝ№ҙУИЭРФөҪёРРФұд»Ҝ) ,әНЖдЧФЙнөДКэҫЭІЙјҜУлјаҝШ( SCADA)ПөНіПаЕдәП,ҝЙТФКөПЦФ¶·ҪЧиҝ№әН№ҰВКіұБчөчҪЪ,ЖҪПўөШЗшРФ№ҰВКХсөҙ,МбёЯПөНіФЭМ¬ОИ¶ЁРФ,ТЦЦЖҙОН¬ІҪРіХсЎЈ ұҫОДНЁ№эТ»ёцФЪСРПоДҝЎӘЎӘёЈҪЁ-»Ә¶«өзНш»ҘБӘөДҝЙҝШҙ®І№СРҫҝ,ПкПёҪйЙЬБЛҝЙҝШҙ®БӘІ№іҘ( TCSC)КөСйҝШЦЖЖчөДЗ°ЦГөҘФӘІҝ·ЦЙијЖ,ТФұгУЪОӘКөјКҫцІЯМṩНкХыЎўЧјИ·өДКөСйКэҫЭЎЈ TCSCөДОИМ¬МШРФ·ЦОцөзВ·ДЈРН TCSCөД»щұҫҪб№№КЗ№М¶ЁөДҙ®І№өзИЭCІўБӘТ»ёцУЙЛ«Птҫ§Хў№Ь(КөјКТІҝЙ°СБҪёцөҘПтҫ§Хў№ЬІўБӘ·ҙҪУФЪТ»Жр)ҝШЦЖөДөзҝ№L ,Нј1ЛщКҫОӘОИМ¬·ЦОцУГөДTCSCДЈРН: ЛьөДФЛРРДЈКҪУР: 1) ҫ§Хў№ЬҪШЦ№ЎЈ TCSCөИН¬УЪ№М¶Ёҙ®БӘІ№іҘЎЈ 2) ҫ§Хў№ЬЕФВ·ЎЈ ФЪөзБчХэ»т·ҙ·ҪПтБч№эVTКұ,Л«Птҫ§Хў№ЬVT·ЦұрФЪ180Ўг·¶О§ДЪИ«өјНЁ,ПЯВ·өзБчҙуІҝ·ЦНЁ№эL ,ХыёцTCSCіКПЦРЎөзҝ№МШРФЎЈ 3) ИЭРФОўөчДЈКҪЎЈ VTөјНЁҪЗҪПРЎ,ХыёцTCSCөДЧиҝ№іКПЦҙуУЪCұҫЙнөДИЭҝ№МШРФЎЈ 4) ёРРФОўөчДЈКҪЎЈ VTөДөјНЁҪЗҪПҙу,ХыёцTCSCөДЧиҝ№іКПЦёРРФөзҝ№МШРФЎЈ  НЁ№эЖдФЛРРДЈКҪҝЙТФҝҙіц,ҝШЦЖЛ«Птҫ§Хў№ЬVTөДөјНЁҪЗҝЙТФёДұдLC»·В·өјНЁөзБч,ҙУ¶шҝЙТФБ¬РшҝмЛЩөчХыTCSCЧиҝ№Цө¶шҙпөҪЖдҝШЦЖДҝөДЎЈ КөСйҝШЦЖПөНіУЙЙПО»Цч»ъәНЗ°ЦГҝШЦЖөҘФӘЧйіЙ,ЙПО»»ъЦчТӘёәФрПөНі·ЦОц,ҝШЦЖЛг·ЁөДИ·¶ЁЎЈ З°ЦГөҘФӘКөПЦёЯЛЩКэҫЭІЙјҜ,ADЧӘ»»,УлЙПО»»ъҝмЛЩҙ«өЭКэҫЭј°ҙҘ·ўҝЙҝШ№иөИ¶аПо№ҰДЬЎЈ З°ЦГөҘФӘөДРиЗу·ЦОц З°ЦГөҘФӘөДФЪХыёцTCSCКөСйҝШЦЖПөНіЦРЦчТӘНкіЙТФПВ3По№ӨЧчЎЈ әНЙПО»»ъөДНЁС¶ З°ЦГөҘФӘНЁ№эUSBҪУҝЪәНЙПО»»ъНЁС¶ЎЈ Хвёц№ҰДЬКЗЖдЛьБҪёц№ҰДЬөД»щҙЎ,ТӘКөПЦХвТ»№ҰДЬ,РиТӘЙијЖЙиұё¶Л(З°ЦГөҘФӘ)әНЦч»ъ¶Л(ЙПО»»ъ)өДUSB Инјю,Іў¶ЁТеЙПО»»ъәНЗ°ЦГөҘФӘјдНЁС¶өДКэҫЭёсКҪЎЈ КэҫЭІЙјҜ З°ЦГөҘФӘТӘІЙјҜҙУөзБч(өзС№)ҙ«ёРЖчКдИлөДИэПаөзБчәНИэПаөзС№,№ІБщВ·КэҫЭЎЈөұЙПО»»ъРиТӘИэПаөзБчөзС№КэҫЭКұ,ҫН·ўЛНГьБоёшЗ°ЦГөҘФӘТӘЗуЖдҝӘКјІЙјҜКэҫЭ,ІўЙи¶ЁЛщРиІЙСщөДЦЬЖЪКэЎЈЗ°ЦГөҘФӘКХөҪГьБоәуБўјҙҝӘКјКэҫЭІЙјҜ,ІўНЁ№эUSB°СІЙјҜөДКэҫЭ°ҙФј¶ЁөДёсКҪЛНёшЦч»ъЎЈТӘКөПЦБщВ·ІЙСщ№ҰДЬ,З°ЦГөҘФӘұШРлҫЯұёІЙСщұЈіЦЖчЎў¶аВ·СЎФсЖчәНADЧӘ»»ЖчЎЈ КэҫЭІЙјҜөДЛЩ¶И·ЦОц:ТтОӘЙПО»»ъРиТӘ¶ФөзС№өзБчРЕәЕҪшРРёЯҙОРіІЁ·ЦОц,ЛщТФКэҫЭІЙјҜөДЛЩ¶ИұШРлҫЎБҝҝмЎЈS3C44B0XЧФҙшөДADЧоёЯІЙСщЖөВКОӘ100 kSPS(10ҰМsТ»ҙО) ,јУЙПЖд¶аВ·СЎФсЖчөДЗР»»КұјдОӘ15ҰМs,КөјКөДЧоҝмІЙСщЛЩ¶ИОӘ25 ҰМsТ»ҙОЎЈХвАпСЎФсГҝ0.2 ms¶ФИэПаөзС№әНИэПаөзБчёчІЙСщТ»ҙО,јҙГҝ33ҰМsІЙСщТ»ёцКэҫЭЎЈХвСщГҝёцЦЬІЁҝЙТФІЙСщ100 ҙО,ҝЙТФ·ЦОцөҪ5Ў«7ҙОРіІЁЎЈ ИэПаҫ§Хў№ЬөДҙҘ·ўҝШЦЖ ЙПО»»ъјЖЛгіцәПККөДҫ§Хў№ЬөјНЁҪЗІўНЁ№эUSBҙ«ёшЗ°ЦГөҘФӘ,З°ЦГөҘФӘК№УГҙЛөјНЁҪЗ·ўіцҫ§Хў№ЬҙҘ·ўРЕәЕЎЈТӘКөПЦҙЛ№ҰДЬ,З°ЦГөҘФӘұШРлҫЯУР3В·өзС№№эБгјаІвЖчәНҫ§Хў№ЬҙҘ·ўөзВ·,ИзНј2ЛщКҫЎЈ УІјюЙијЖ өҘФӘУІјюөзВ·өДәЛРДІҝ·ЦІЙУГ51EDAәНЗЪСР№«ЛҫБӘәПСРЦЖөД44B0XҝӘ·ў°еЎЈ ёГҝӘ·ў°еК№УГSAMSUMG S3C44B0XҙҰАнЖч,ІўјҜіЙБЛЖдЛьНвІҝЙиұё,ЦчТӘ°ьАЁ2 MB16 О»КэҫЭҝн¶ИөДПЯРФFlash( SST39VF160) , 10M TCP / IP ҪУҝЪ(RTL8019 ) , USBDeviceҪУҝЪ( Philip s PD IUSBD12) ,LCDҪУҝЪ, 7В·ADCКдИл,БҪВ·ұкЧјRS232ҪУҝЪөИөИЎЈҙЛНв,ёщҫЭҝОМвРиТӘФЪЙијЖЦР»№ЧФРРА©Х№БЛ№эБгјмІвөзВ·,ІЙСщұЈіЦөзВ·әНҝЙҝШ№иҙҘ·ўөзВ·ЎЈ  ОўҙҰАнЖчSAMSUNG S3C44B0XҪйЙЬ Т»ҝо»щУЪARM7TDM IДЪәЛөД32О»өДёЯРФДЬR ISCҙҰАнЖчЎЈ Ц§іЦ16О»ThumbәН32О»ARMЛ«ЦёБојҜ,УИЖдКЗФЪК№УГ16О»ThumbЦёБојҜКұИФИ»ПнКЬARMҙҰАнЖчөД32О»өДМШРФ,Из32О»іӨөДјДҙжЖч, 32О»өДС°Ц·ҝХјдөИ,ІўЗТөГөҪёьёЯГЬ¶ИҙъВлЎЈ ҙЛНв»№јҜіЙәЬ¶аНвЙи,°ьАЁ8НЁөАADC,НвІҝҙжҙўЖчҝШЦЖЖч, LCDҝШЦЖЖч, 4НЁөАDMA, 71ёцНЁУГIOҝЪ,ҫЯУРИХАъ№ҰДЬөДRTCКұЦУ, 5ёцPWM¶ЁКұЖч,Т»ёцДЪІҝ¶ЁКұЖчәНТ»ёцҝҙГЕ№·¶ЁКұЖч,Ж¬ДЪЛшПа»·( PLL)КұЦУ·ўЙъЖч(ЧоёЯКұЦУЖөВК66 MHz) , 2 НЁөАТмІҪҙ®ҝЪ,ҙшУР16 ЧЦҪЪF IFO, IICЎўIISЧЬПЯҝШЦЖЖчөИөИЎЈ USBҪУҝЪЖчјюPD IUSBD12ҪйЙЬ Philip s№«ЛҫНЖіцөДТ»ҝоУҰУГ№г·әөДUSB ҪУҝЪЖчјю,·ыәПUSB1.1№ж·¶,јҜіЙSIE, F IFOҙжҙўЖч,КХ·ўЖчТФј°өзС№өчХыЖч,ҝЙУлИОәОНвІҝОўҝШЦЖЖч»тОўҙҰАнЖчКөПЦёЯЛЩІўРРҪУҝЪ(2 MB / s) ,НкИ«DMAІЩЧч,Цч¶ЛөгөДЛ«»әіеЕдЦГФцјУБЛКэҫЭНМНВБҝІўЗбЛЙКөПЦКөКұКэҫЭҙ«КдЎЈ өзС№№эБгјмІвөзВ· №эБгјмІвөзВ·УЙТ»ёцөзЗЕ,№вөзёфАлј°ЖдЛьЖчјюЧйіЙ,№І3Чй,БҪёц74HC14·ҙПтГЕУГАҙҪ«өзС№ХыРООӘTTLөзЖҪ,КдИлөҪОўҙҰАнЖчS3C44B0XНвІҝЦР¶П¶Л,өұөзБҰПЯөзС№ұдОӘБгКұ,№вөзёфАлЖчЦР·ў№в¶юј«№ЬҪШЦ№,ҙЛКұПтЦР¶П¶ЛКдіцёЯөзЖҪВціеТэ·ўЦР¶ПЎЈ ІЙСщұЈіЦөзВ· ұЈіЦЖч№І6 В·,ЖдЦР3 В·ІвөзС№, 3 В·ІвөзБчЎЈІЙУГLF398РҫЖ¬,ЛьУР8ёцТэҪЕ, 1әН4ҪЕҪУөзФҙ,·¶О§ОӘ( ЎА5 Ў« ЎА18) VЦ®јд, 3ҪЕОӘКдИл¶Л,ҪУөзБҰПЯҫӯұдС№әуөДөзС№»тҫӯөзБч»ҘёРЖчЧӘ»ҜөДөзС№, 2ҪЕҪУ1 kҰёөзЧи,УГУЪөчҪЪЖҜТЖөзС№ЎЈ7ҪЕҪУІОҝјөзС№, 8 ҪЕҪУҝШЦЖРЕәЕ,ҝШЦЖРҫЖ¬өДІЙСщұЈіЦЧҙМ¬ЎЈФЪХвАпНЁ№эS3C44B0XөДНЁУГI/O ТэҪЕGPF0-5 ·ЦұрҝШЦЖ6 В·ІЙСщұЈіЦЖчөД8ҪЕЎЈ6ҪЕНвҪУұЈіЦөзИЭ,ХвАпҝјВЗөҪКөКұРФөДТӘЗу,ТтҙЛСЎФсҪПРЎөДөзИЭЦө,ИЎC1 = 0.001ҰМF,ҙЛКұІЙСщКұјдІ»і¬№э10ҰМs,Н¬КұҝЙТФВъЧг8О»өДІЙСщҫ«¶ИЎЈ ҫ§Хў№ЬҙҘ·ўөзВ· ҙҘ·ўөзВ·№І3 Чй·ЦұрҪУA, B, CИэПа,ИзНј3 ЛщКҫ,БҪёц74LS04·ҙПтГЕУГАҙФцјУЗэ¶ҜДЬБҰ,КдИл¶ЛҪУ44B0XөДНЁУГIO ҝЪGPE4-6ТэҪЕЎЈВціеұдС№ЖчN1 әНN2Т»·ҪГжҙ«өЭҙҘ·ўВціе,БнТ»·ҪГж¶ФЗҝИхөзЦ®јдЖрөҪәЬәГөДёфАлЧчУГЎЈCPU ·ўіцҙҘ·ўВціеРЕәЕЦ®әу,БҪёц·ҙПтҝЙҝШ№иөДҙҘ·ў¶Л»бН¬КұУРҙҘ·ўРЕәЕ,ө«УЙУЪДіТ»КұҝМјУФЪБҪёцҝЙҝШ№иЙПөДөзС№Ц»УРТ»ёцВъЧгөјНЁМхјю,№КЦ»УРТ»ёцҝЙҝШ№и»бөјНЁЎЈ  ИнјюЙијЖ З°ЦГөҘФӘөДИнјюТӘНкіЙәНЙПО»»ъНЁС¶ЎўAD ІЙСщәНҫ§Хў№ЬҙҘ·ў3По№ҰДЬЎЈ ЖдЦРADІЙСщЛЩВКәЬёЯЎўҫ§Хў№ЬҙҘ·ўКөКұРФәЬЗҝ,ЛщТФХвБҪПо№ҰДЬұШРлІЙУГУІјю¶ЁКұЖчАҙұЈЦӨЖдКөКұРФ,ТтҙЛЙијЖК№УГЦР¶П·юОсіМРт( Interrup t Service Routine, ISR ) АҙНкіЙХвБҪПо№ҰДЬЎЈUSBЗэ¶ҜіМРтУЙҝӘ·ў°еёҪҙш,НЁС¶өД№ҰДЬЦчТӘНЁ№эҰМC /OS-ўтЦРөДИООсАҙНкіЙ(өұИ», USB ЦР¶ПҙҰАнТІКЗұШІ»ҝЙЙЩөД)ЎЈUSB ИООсәНёчISR Ц®јдөДНЁС¶НЁ№эҰМC /OS-ўтөДН¬ІҪ»ъЦЖ(РЕәЕБҝЎўПыПў¶УБР)әНИ«ҫЦұдБҝАҙНкіЙЎЈ ЛщУРИнјюҫщКЗФЪARM№«ЛҫЧФјәөДҝӘ·ў»·ҫіADSПВКөПЦөД,ADS1ЎЈ2УРЧФјәөДC, C + +УпСФұаТлЖчј°ҝвОДјю,УРGU IҪзГжөДөчКФЖчAXDәНГьБоРРҪзГжөДөчКФЖчarmsdТФј°GU IҪзГжөДұајӯЖчCode WarriorIDE,ХвОӘҝӘ·ўИЛФұМṩБЛј«ҙуөДұгАыЎЈ өчКФ№ӨҫЯУГөДКЗJTAG·ВХжЖч, JTAG·ВХжЖчНЁ№эJTAGұЯҪзЙЁГиҝЪУлARM CPUәЛНЁРЕ,КфУЪНкИ«·ЗІеИлКҪ(јҙІ»К№УГЖ¬ЙПЧКФҙ)өчКФ,ЛьОЮРиДҝұкҙжҙўЖч,І»ХјУГДҝұкПөНіөДИОәО¶ЛҝЪ,КЗДҝЗ°ІЙУГЧо¶аөДТ»ЦЦөчКФ·ҪКҪЎЈ З¶ИлКҪКөКұІЩЧчПөНіҰМC /OS-IIҪйЙЬ ¶ФУЪёҙФУөДУҰУГ,ЦұҪУФЪВг»ъЙПҝӘ·ўФЛРРөДЗ°әуМЁПөНіҝӘ·ўЎўО¬»ӨәНА©Х№¶јәЬА§ДС,З¶ИлКҪІЩЧчПөНіУҰФЛ¶шЙъ,ЖдЧоҙуөДМШөгҫНКЗҙҰАн¶аИООс,¶шЗТФЪ№ӨҝШБмУтҙу¶аКөКұРФТӘЗуҪПЗҝ,¶шҰМC /OS-IIУӯәПБЛХвР©МШөгЎЈҰМC /OS-IIЦ§іЦ64ёцИООс,ГҝёцИООсөДУЕПИј¶ұШРлКЗІ»Н¬өД,өч¶ИЛг·ЁЧЬКЗИГҙҰУЪҫНРчЧҙМ¬өДЧоёЯУЕПИј¶ИООсПИЦҙРР, ІўМṩБЛРЕәЕБҝ( Semaphore) ЎўУКПд(Mailbox)әНПыПў¶УБР(Message Queue)өИ¶аЦЦНЁС¶Н¬ІҪФӯУпЎЈГҝёцИООс¶јҙҰФЪТФПВ5ЦЦЧҙМ¬Ц®Т»өДЧҙМ¬ПВ,Хв5ЦЦЧҙМ¬КЗРЭГЯМ¬(Dormant) ,ҫНРчМ¬(Ready) ЎўФЛРРМ¬(Running) Ўў№ТЖрМ¬(Waiting)әНұ»ЦР¶ПМ¬( Interrup ted)ЎЈҰМC /OS-IIЦРИ«ІҝПөНіөчУГөДЦҙРРКұјдКЗҝЙИ·¶Ё,ЖдПөНіөчУГөДЦҙРРКұјдІ»ТААөУЪУҰУГИООсөД¶аЙЩ,ХвТІКЗЖдКөКұРФөДұнПЦЎЈ ЦР¶П·юОсіМРт( ISR)өДЙијЖ ADІЙСщәНҫ§Хў№ЬҙҘ·ўХвБҪПо№ҰДЬУЙЦР¶П·юОсіМРт( ISR)АҙНкіЙЎЈёщҫЭҰМC /OS-ўтТӘЗу, ISRҝӘКјКұРиөчУГOSIntEnter ( )әҜКэНЁЦӘҰМC /OS-ўтПөНіҪшИлБЛISR,ISRҪбКшКұРиөчУГOSIntExit ( )әҜКэНЁЦӘҰМC /OS-ўтҪшРРҪшіМөч¶ИЎЈ ADІЙСщДЈҝйУР3 ёцISR,·ЦұрКЗ: ¶ЁКұЖч4 ISR(ІъЙъЦЬЖЪРФөДІЙСщұЈіЦРЕәЕ) ,¶ЁКұЖч5 ISR (ІъЙъ16ҰМsөДСУіЩ,ТФ·ыәПS3C44B0XөД¶аВ·СЎФсЖч¶ФЗР»»КұјдөДТӘЗу) ,AD ISR (¶БИЎADІЙСщҪб№ы,ІўҪшРРПаУҰөДІЩЧч)ЎЈПөНіұШРлФЪБҪҙОTimer4ЦР¶ПЦ®јдНкіЙ6ҙОADІЙСщ№ӨЧчЎЈҫ§Хў№ЬҙҘ·ўДЈҝйУР3ЧйЎўГҝЧй2ёцISRЎЈГҝЧйөД2ёцISR·ЦұрОӘТ»ёц№эБгјмІвISRәНТ»ёц¶ЁКұЖчISR,№ІН¬ҝШЦЖТ»ПаөДҫ§Хў№ЬҙҘ·ўЎЈ ҰМC /OS-IIИООсЙијЖ З°ЦГөҘФӘНЁ№эPD IUSBD12 өДEndpoint1 ( PacketSize = 16 B )ҪУКЬЙПО»»ъөДГьБо,·ө»ШГьБоөДЦҙРРЧҙМ¬,НЁ№эPD IUSBD12өДEndpoint2 ( Packet Size = 64 B)·ө»ШAD ІЙСщөДҪб№ыЎЈ ХвНЁ№эБҪёцәҜКэTaskUsbEp1RxDoneәНTaskUsbEp2SendData ҝЙТФКөПЦ, Н¬КұНЁ№эTaskUsbSetupPacketәҜКэАҙҙҰАнЦч»ъ·ўАҙөДЗлЗуЎЈОТГЗЙиЦГPD IUSBD12 өДEndpoint1 ( Generic Endpoint) №ӨЧчФЪInterrup t ДЈКҪ, Endpoint2 (Main Endpoint)№ӨЧчФЪBulkДЈКҪ,Фт: 1) TaskUsbEp1RxDone TaskUsbEp1RxDoneОӘЗ°ЦГ»ъҪУКЬЙПО»»ъІЙСщ»тЦГҙҘ·ўҪЗөДИООс,Жд№ӨЧчБчіМПВЛщКҫЎЈ ПИУГOSSemPend ( )өИҙэЙПО»»ъ·ўЛНГьБо,ИфЙПО»»ъ·ўАҙөДCOMM_START_ADГьБо,Фт: ИфTOTAL _ SAMPLE _ TIMES! = 0, ФтНЁ№эEndpoint1·ө»ШҙнОуРЕПўёшЙПО»»ъ,·сФтЦГAD_BUFF_P =0, TOTAL _ SAMPLE _ TIMES =ЛщРиІЙСщөДЦЬЖЪКэЎБ100,ҝӘЖфTimer4 (ІЙСщұЈіЦ¶ЁКұЖч) ,НЁ№эEndpoint1·ө»ШіЙ№ҰРЕПўёшЙПО»»ъЎЈ  ИфЙПО»»ъ·ўАҙөДКЗCOMM _SET_ANGLEГьБоФтЙиЦГПаУҰөДX_ANGLEұдБҝ,ДЬ№эEndpoint1·ө»ШіЙ№ҰРЕПўёшЙПО»»ъЎЈ 2) TaskUsbEp2SendData TaskUsbEp2SendDataИООсөД№ӨЧчҙОРтОӘПИөИҙэAD ISR·ўЛНТӘЗуҙ«ЛНКэҫЭөДПыПў,ПыПў·ўіцәу,ФЪөИҙэЙПҙОUSBҙ«ЛНҪбКш,ФЩНЁ№эEndpoint2·ўЛН»әіеЗшЦРөДКэҫЭЎЈ 3) TaskUsbSetupPacket TaskUsbSetupPacketИООс№ӨЧчҙОРтОӘПИөИҙэSetupPacketКВјю,КВјю·ўЙъәуФЩөчУГUsbControlHandler( )әҜКэҙҰАнЦч»ъөДЗлЗуЎЈ ИнјюХыМеҪб№№ ХыМеИнјюҪб№№ҝтНјИзНј4ЛщКҫ(НјЦРҫШРОҝтҙъұнЦР¶П·юОсіМРтISR,НЦФІҙъұнҰМC /OS-ўтИООсРйПЯҝтҙъұнҰМC /OS-ўтРЕәЕБҝ»тПыПў¶УБР)ЎЈ ҪбВЫ КөСйҪб№ыұнГч,КөјКПөНіКэҫЭІЙјҜЛЩ¶ИУлЙијЖКұФӨЖЪөДҪб№ы»щұҫТ»ЦВ,УЎЦӨБЛПЦҪЧ¶ОҪбәПКэҫЭІЙјҜЎўADЧӘ»»ЎўКэҫЭҙ«Кдј°ЖдЛь№ҰДЬДЈҝйИз№эБгјмІвЎўҙҘ·ўҝЙҝШ№иөИЦо¶аИООсУЪТ»МеөДёҙФУПөНі,ұШРлУР№ҰДЬЗҝҙуөДУІјюЧКФҙЖҪМЁЧцЦ§іЕ;ФЪ¶аИООсЎўКөКұРФҪПЗҝөДіЎәП,З¶ИлКҪКөКұІЩЧчПөНіКЗұШІ»ҝЙЙЩөД;ФЪКэҫЭҙ«Кд·ҪГж,USBФЪЛЩ¶И·ҪГжөДУЕКЖұИҙ«НіөДRS232ёьДЬВъЧгTCSCКөКұҝШЦЖөДТӘЗуЎЈ |

НшУСЖАВЫ