Р§ЫЕFPGAСЌди45ЃКDDRПижЦЦїМЏГЩгыЖСаДВтЪджЎАхМЖЕїЪд

ЗЂВМЪБМфЃК2016-11-9 17:07

ЗЂВМепЃКrousong1989

|

Р§ЫЕFPGAСЌди45ЃКDDRПижЦЦїМЏГЩгыЖСаДВтЪджЎАхМЖЕїЪд ЬиШЈЭЌбЇЃЌАцШЈЫљга ХфЬзР§ГЬКЭИќЖрзЪСЯЯТдиСДНгЃК http://pan.baidu.com/s/1c0nf6Qc

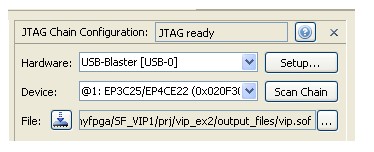

Ђй ДђПЊЁАЁ\prj\vip_ex2ЁБЮФМўМаЯТЕФЙЄГЬЁЃ Ђк ЕуЛїQuartus IIВЫЕЅРИЕФЁАToolsЈЄIn-System Memory Content EditorЁБЃЌдкНчУцЕФгвВрЃЌШчЭМ4.25ЫљЪОЃЌбЁдёЁАЁ\prj\vip_ex2\output_filesЁБЮФМўМаЯТЕФvip.sofЃЌжДааЯТдиВйзїЃЌМДЕуЛїFileгвВрЕФаЁАДХЅЁЃ

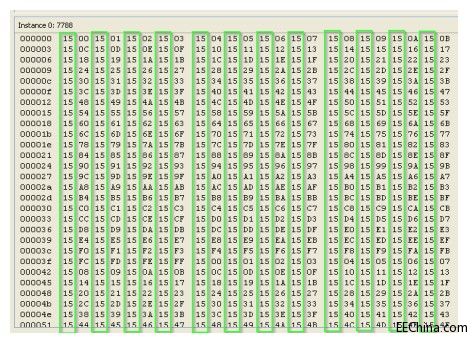

ЭМ4.25 JTAGЯТдиХфжУНчУц Ђл ЯТдиЭъГЩКѓПЩвдПДЕНVIPАхЩЯЕФжИЪОЕЦD1ЩСЫИЁЃДЫЪБЮвУЧНгзХбЁжаIndexЯТУцЕФMemoryЯюЃЌШЛКѓЕЅЛїбЛЗЖСШЁАДХЅЃЌШчЭМ4.26ЫљЪОЁЃ

ЭМ4.26 ПЩдкЯпВщПДЕФЦЌФкRAM Ђм НгзХЮвУЧПЩвдЙлВьMemoryЕБЧАЕФЪ§ОнБфЛЏЁЃШчЭМ4.27ЫљЪОЃЌОиаЮПђЦ№РДЕФИпзжНкЪ§ОнЃЌМДЮвУЧУПИєвЛУыЖрЭГвЛЕндівЛДЮЕФЪ§ОнЃЌЖјЦфКѓЕФЕЭзжНкЪ§ОндђЪМжеЪЧДг0ПЊЪМЕндіКЭЕижЗвЛвЛЖдгІЕФЕндіЪ§ОнЁЃвђДЫЃЌЮвУЧПДЕНЕФЪЕбщНсЙћЪЧЃЌетИіonchip RAMЕФЫљга16bitЕФИпзжНкУПИєвЛУыЖМЛсЕндівЛЃЌЖјЦфКѓЕФЪ§ОндђвЛжББЃГжЕБЧАзДЬЌВЛБфЁЃ

ЭМ4.27 ЕндіЕФDDR2ЖСГіЪ§Он |

ЭјгбЦРТл