Р§ЫЕFPGAСЌди43ЃКDDRПижЦЦїМЏГЩгыЖСаДВтЪджЎDDR2в§НХЕчЦНЩшжУ

ЗЂВМЪБМфЃК2016-11-3 17:55

ЗЂВМепЃКrousong1989

|

Р§ЫЕFPGAСЌди43ЃКDDRПижЦЦїМЏГЩгыЖСаДВтЪджЎDDR2в§НХЕчЦНЩшжУ ЬиШЈЭЌбЇЃЌАцШЈЫљга ХфЬзР§ГЬКЭИќЖрзЪСЯЯТдиСДНгЃК http://pan.baidu.com/s/1c0nf6Qc

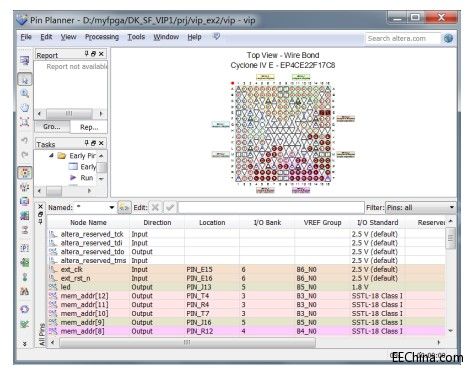

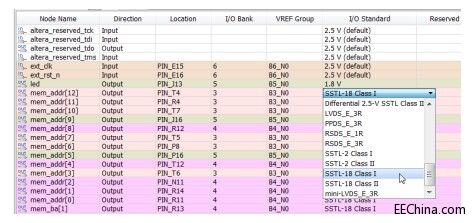

DDR2ЕФБъзМIOЕчЦНВЛЪЧЮвУЧНгДЅзюЖрЕФ3.3V TTLЃЌЖјЪЧ1.8VЕФЁАSSTL-18 Class IЁББъзМЃЌФЧУДетИіЕчЦНБъзМЃЌдкFPGAжаШчКЮЩшжУЃП ЮвУЧПЩвдЯШЕуЛїQuartus IIЕФВЫЕЅЁАAssignments ЈЄ Pin PlannerЁБЃЌДђПЊPin PlannerШчЭМ4.18ЫљЪОЁЃетРяПЩвдзіFPGAаХКХКЭЪЕМЪаОЦЌdieв§НХЕФгГЩфЃЌАќРЈв§НХЕФЕчЦНБъзМЁЂЕчСїЧПЖШЁЂЦЌФкЩЯЯТРЁЂЦЋаБТЪЕШЕШВЮЪ§ЖМПЩвддкетРяХфжУЁЃетжжСщЛюЕФв§НХПЩХфжУадЃЌЦфЪЕвВЪЧFPGAПЩБрГЬСщЛюадЕФвЛДѓЬхЯжЁЃ

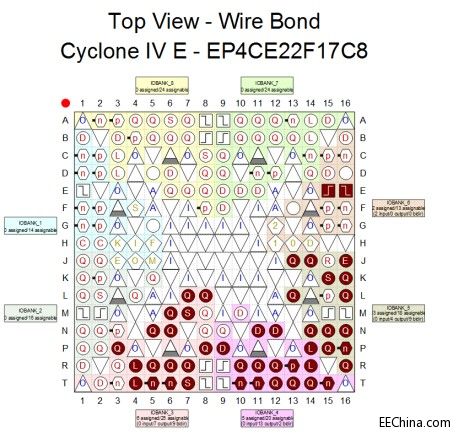

ЭМ4.18 Pin PlannerНчУц дкетИіPin PlannerНчУцжаЃЌЮвУЧПЩвдЯШПДПДЁАTop View ЈC Wire BondЁБетИіЪгЭМЁЃШчЭМ4.19ЫљЪОЃЌдкаОЦЌв§НХЪгЭМЕФЭтВрЃЌга8ИіаЁОиаЮПђЗжБ№БъЪОСЫIO BANKКХЃЌЭМжаЖдгІВЛЭЌЕФбеЩЋБэЪОСЫВЛЭЌЕФIO BANKЁЃ

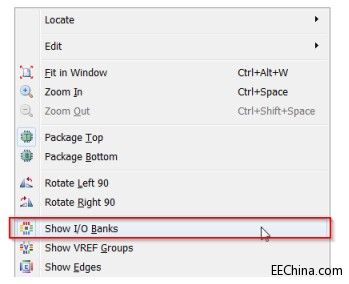

ЭМ4.18 в§НХЪгЭМ ШєЪЧЁАTop View ЈC Wire BondЁБУЛгаГіЯжВЛЭЌЕФIO BANKБъЪОЃЌФЧУДЮвУЧПЩвддкетИіЪгЭМЕФПеАзДІЕуЛїгвМќЃЌШчЭМ4.19ЫљЪОЃЌШЛКѓЕЅЛїЁАShow I/O BanksЁБбЁЯюДђПЊЁЃ

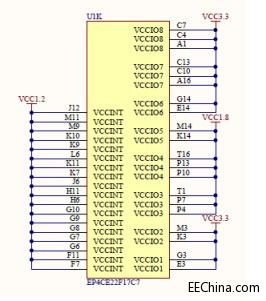

ЭМ4.19 в§НХЪгЭМЕФгвМќВЫЕЅ FPGAЕФЕчЦНБъзМЃЌЭЈГЃЪЧвдIO BANKЮЊЕЅЮЛНјааЛЎЗжЕФЃЌЖдгквЛПХFPGAаОЦЌЃЌЫќЭЈГЃЛсИљОнЪЕМЪЧщПіЃЌНЋвЛаЉОЭНќЕФв§НХЛЎЗждкЭЌвЛИіIO BANKжаЃЌВЂЧввЛПХFPGAаОЦЌзмЛсЛђЖрЛђЩйЛЎЗжГіМИИіIO BANKРДЁЃВЛЭЌЕФIO BANKПЩвдгаВЛЭЌЕФIOЕчЦНБъзМЃЌЕЋЪЧдкЭЌвЛИіIO BANKФкЕФв§НХЃЌЫќУЧЕФIOЕчЦНБъзМвЛЖЈЪЧвЛбљЕФЁЃ ЛиЕНЮвУЧЕФгІгУжаРДЃЌдкЮвУЧЕФКЫаФАхЩЯЃЌДѓЖМЪЧЕФIO BANKЕФЕчЦНЖМЪЧ3.3VЕФЃЌЖјDDR2в§НХЫљЪЙгУЕФIO BANKдђЪЧ1.8VЁЃШчЭМ4.20ЫљЪОЃЌдкдРэЭМЩшМЦЩЯЃЌVCCIOЕчбЙЙЉ1.8VЕФBANK3ЁЂBANK4КЭBANK5ЃЌЖМСЌНгСЫDDR2ЕФв§НХЁЃ

ЭМ4.20 FPGAЙЉЕчЕчТЗ ЛљгкДЫЃЌЮвУЧдкFPGAФкВПЕФв§НХЕчЦНБъзМЕФЩшЖЈЩЯЃЌЮвУЧвВашвЊзіЯргІЕФЩшЖЈЁЃШчЭМ4.21ЫљЪОЃЌЮвУЧдкЁАI/O StandardЁБвЛСажаЃЌЖдгІDDR2в§НХЃЌбЁдёЫќУЧЕФЕчЦНБъзМЮЊЁАSSTL-18 Class IЁБЁЃ

ЭМ4.21 DDR2в§НХЕчЦНЩшжУ |

ЭјгбЦРТл