基于CPLD的120MHz高速A/D采集卡的设计

发布时间:2010-7-29 11:17

发布者:lavida

|

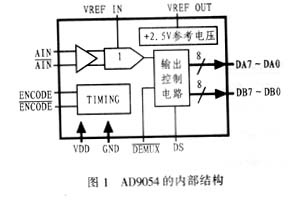

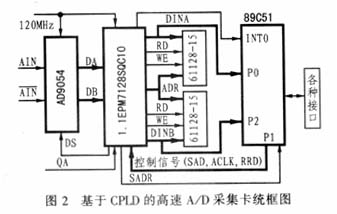

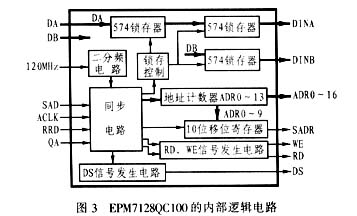

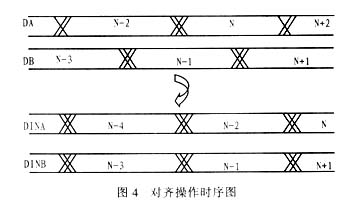

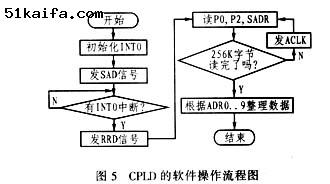

高速A/D采集技术已在许多领域得到愈来愈广泛的应用,本文将详细论述采用CPLD技术来实现120MHz高速A/D采集卡的设计方法,该采集卡具有包括负延迟触发在内的多种触发方式,采用CPLD复杂可编程逻辑器件(又称FPGA)EPM7128SQC100-7和AD公司的高速模数转换器(A/D)AD9054BST-135来实现。 1 芯片介绍 1.1 EPM7128SQC100-7简介 EPM7128SQC100-7内含128个宏单元(或2500个可用门),其引脚到引脚的最短传输延时为7ns,采用单+5V电源供电,可通过 JTAG接口实现在线编程,并带有可供84个用户使用的I/O脚(其中4个为专用输入脚)。该器件采用PQFP-100封装。其中TDI、TDO、 TMS、TCLK脚为编程脚;GCLK、GOE、GCLEAR、REDIN脚为专用输入脚;VCCINT、VCCIO脚接+5V电源;GND脚接地; I/O为用户可编程输入输出脚。在I/O脚作输出使用时,可由用户设定为0,1和Z三种状态。 1.2 AD9054BST-135简介 AD9054BST-135是一种低价位135MSPS的8位A/D转换器,其模拟输入电压峰峰值为1V,且内置2.5V参考电压,采用+5V单电源供电,并可与TTL电平接口,具有单8位或双8位A/D转换结果输出模式,采用TQFP-44脚封装形式,其内部结构如图1所示,各管脚的定义如下: AIN:模拟电压输入正端;  模拟电压输入负端; 模拟电压输入负端;ENCODE:时钟输入正端;  时钟输入负端,通常应通过电容耦合接地; 时钟输入负端,通常应通过电容耦合接地; 输出数据模式设置引脚。该脚为1时,采用单8位A/D转换结果输出模式。该脚为0时,采用双8位A/D转换结果输出模式; 输出数据模式设置引脚。该脚为1时,采用单8位A/D转换结果输出模式。该脚为0时,采用双8位A/D转换结果输出模式;DS:数据同步控制引脚,正脉冲输入; AD7~DA0:A/D转换输出; D B7~DB0:A/D转换输出; V REFOUT:+2.5V参考电压输出; V REFIN:参考电压输入; DVD:+5V电源输入端; GND:电源地。  使用时,如将接地,则AD9054工作于双8路数据输出模式。上电后,DA7~DA0及DB7~DB0均以二分之一的ENCODE频率(即120MHz/2)输出A/D 转换结果,因此从DA7~DA0及DB7~DB0读取的A/D转换结果,无法知晓DA口与DB口的数据所对应的采样点在时序上的先后。这样,需要加一个数据同步脉冲DS信号,并让DS正脉冲的后沿后的4个时钟周期上的DA口与DB口同步有效,即在DS后沿的第2N+1与2N+3个ENCODE上升沿期间输出第K点采样值的转换结果;在DS后沿后第2N+2与2N+4个ENCODE上升沿期间输出第K+1点采样值的转换结果(注:N≥1,K≥0,K=0对应的采样值为DS下降沿后ENCODE第一次上升沿时刻所对应的采样输入值)。因此,在施加DS信号后就可以得知任一时刻A口数据与B口数据所对应的采样点在时间上的先后顺序,以便读取有用的A/D转换数据。 2 系统设计原理 图2是基于CPLD的高速 A/D采集卡的系统设计原理框图。图中,89C51送往EPM7128S的控制信号包括一个A/D启动信号SAD、一个读SRAM信号RRD和一个地址加一控制脉冲ACLK。而EPM7128S送往AD9054的信号为一个DS同步信号,送往89C51的信号为转换结束信号(接INT0)和超前触发地址串行输出信号SADR。 EPM7128S送往61128-15SRAM的信号包括读信号RD、写信号WE、数据信号DINA0~7和DINB0~7以及地址信号ADR0~16。其中两片SRAM的地址信号共用。为了节省EPM7128S的I/O口线,可将61128-15的片选线接地。 QA信号为外触发A/D转换控制信号。  在本文所介绍的A/D数据采集卡中,负延迟触发存贮深度为2k字节。上电复位后, 89C51向EPM7128S发一个A/D启动信号时,EPM7128S也会发一个DS同步脉冲给AD9054,在四个时钟后,EPM7128S输出WE 信号有效,同时将AD9054输出的双8位数据信号以60MHz的频率经锁存处理后送往SRAM,每锁存AD9054数据一次(2字节)将地址 ADR0~13加1。当地址为3FF时(即1k),清地址计数器以使其为零。此后,地址计数器仍以60MHz的频率加1计数,而锁存器仍以60MHz的频率锁存双8位数据并写入SRAM。当地址为3FF时再一次清零,在外触发信号QA到来之前,CPLD就这样控制着整个电路以使其在2k字节存贮深度内作超前循环采集。当某一时刻的QA信号到来时,CPLD首先将此时的地址信号的前10位ADR0~9锁存,随后将地址计数器置为400H,而后地址计数器仍以 60MHz的频率加1计数,而锁存器也以60MHz的频率锁存双8位数据并写入SRAM。当地址计数器为1FFFFH(即128k)时,地址计数器停止计数,锁存器停止锁存数据并对外输出高阻态,CPLD向89C51送出转换结束信号ADEND,并置WE信号无效。 当89C51收到ADEND中断信号后,就可以读取SRAM中的A/D数据以及CPLD中的超前地址ADR0~9。首先89C51将送出一个RRD信号给 EPM7128S,EPM7128S收到RRD信号后立即置RD信号有效,同时将地址计数器清零。此时,两片SRAM均输出地址为0的单元的数据,同时由 CPLD的SADR线输出负延迟触发地址ADR0~9中的ADR0位。89C51则可通过P0和P2口由DINA和DINB分别读取SRAM中的数据,并通过P1口由SADR读地址ADR0位。此后89C51便向EPM7128S发出一个地址加一脉冲ACLK,EPM7128S在收到这个ACLK脉冲后使 ADR0~13加1,同时CPLD由SADR线输出负延迟触发地址ADR0~9中的ADR1位。这样,89C51便可通过不断地发ACLK脉冲来使P0、 P2口的DINA和DINB分别读取SRAM中的数据,并通过P1口来由SADR读负延迟触发地址ADR0~9。 3 CPLD部分的设计 由于EPM7128SQC100的内部逻辑电路是整个系统设计的关键,因此,了解EPM7128SQC100的内图2基于CPLD的高速A/D采集卡统框图基于复杂可编程逻辑器件(CPLD)的120MHz高速A/D采集卡的设计部结构十分重要。图3是其内部结构原理框图。  图3中有三个574锁存器,其作用是将AD9054输出的在时序上未对齐的DA、DB两组数据变为时序上对齐的两组数据DINA、DINB,图4是其对齐操作时序图。 将120MHz信号二分频后所得到的60MHz信号可作为整个逻辑电路的工作频率。工作时,同步控制电路首先将外输入信号与内部60MHz信号同步,然后送往各单元电路。地址计数器的工作情况有两种:一是进行A/D采集时以60MHz频率计数,二是89C51读数时以ACLK脉冲频率计数。RD、WE发生电路的作用是当89C51发SAD信号时,电路输出WE信号有效,RD信号无效;而当89C51发RRD信号时,电路输出RD信号有效,WE信号无效。 DS信号发生电路的作用是在收到89C51的SAD信号时发送一个DS正脉冲。 10位移位寄存器的作用是当外触发信号QA到达时将地址计数器中的ADR0~9锁存,当收到RRD信号后,系统每接收一个ACLK脉冲便将寄存器移位输出一次,顺序是低位在前。 4 单片机的软件设计 单片机的软件设计主要是负责把各种控制信号和数据送给CPLD,并把采集到的数据通过接口送到上位机或其它设备。本卡中的接口有串口和并口两种类型。对CPLD的操作的软件流程框图如图5所示。   由于采用了负延迟触发,所以由SRAM所读取的256k字节并不是按时间的先后顺序存放的,因此必须进行重新排序整理。 5 注意事项 在利用本文的设计方法进行120MHz A/D设计时应注意以下几点: (1)应选用高速器件。 (2)电路中的器件布局要合理,高频信号线应尽量的短。 (3)进行时序分析时应充分考虑器件延时,必要时应考虑长线传输延时,这也是高频信号线应尽量短些的原因之一。 (4)尽量采用同步设计。也就是说整个电路要尽最大可能按某一高频时钟同步工作。本电路的同步时钟为60MHz。 (5)电路内部要尽量滤去毛刺。特别是触发器、计数器的时钟信号、清零信号和置位信号,更应如此。 |

网友评论