Р§ЫЕFPGAСЌди39ЃКDDRПижЦЦїМЏГЩгыЖСаДВтЪджЎFPGAЦЌФкRAMЩшжУгыМЏГЩ

ЗЂВМЪБМфЃК2016-10-14 17:48

ЗЂВМепЃКrousong1989

|

Р§ЫЕFPGAСЌди39ЃКDDRПижЦЦїМЏГЩгыЖСаДВтЪджЎFPGAЦЌФкRAMЩшжУгыМЏГЩ ЬиШЈЭЌбЇЃЌАцШЈЫљга ХфЬзР§ГЬКЭИќЖрзЪСЯЯТдиСДНгЃК http://pan.baidu.com/s/1c0nf6Qc

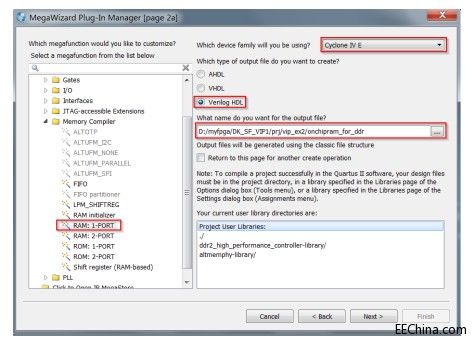

Ђй Quartus IIЙЄГЬжаЃЌЕуЛїВЫЕЅЁАToolsЈЄMegaWizard Plug-In ManagerЁБЃЌДДНЈIPКЫФЃПщЁЃ Ђк дкЕЏГіЕФбЁЯюПЈжабЁдёЁАCreat a new custom megafunction variationЁБЃЌШЛКѓЕуЛїЁАNextЁБЁЃ Ђл бЁдёЮвУЧЫљашвЊЕФIPКЫЃЌШчЭМ4.3ЫљЪОНјааЩшжУЁЃ Ёё дкЁАSelect a megafunction from the list belowЁБЯТУцбЁдёIPКЫЮЊЁАMemory Compiler ЈЄ RAM: 1-PORTЁБЁЃ Ёё дкЁАWhat device family will you be usingЁБКѓУцЕФЯТРРИжабЁдёЮвУЧЫљЪЙгУЕФЦїМўЯЕСаЮЊЁАCyclone IV EЁБЁЃ Ёё дкЁАWhat type of output file do you want to create?ЁБЯТУцбЁдёгябдЮЊЁАVerilog HDLЁБЁЃ Ёё дкЁАWhat name do you want for the output file?ЁБЯТУцЪфШыЙЄГЬЫљдкЕФТЗОЖЃЌВЂЧвдкзюКѓУцМгЩЯвЛИіУћГЦЃЌетИіУћГЦЪЧЮвУЧЯждке§дкР§ЛЏЕФЦЌФкRAM IPКЫЕФУћГЦЃЌетРяЮвУЧПЩвдИјЫћЦ№УћНаonchipram_for_ddrЃЌШЛКѓЕуЛїNextНјШыЯТвЛИівГУцЁЃ

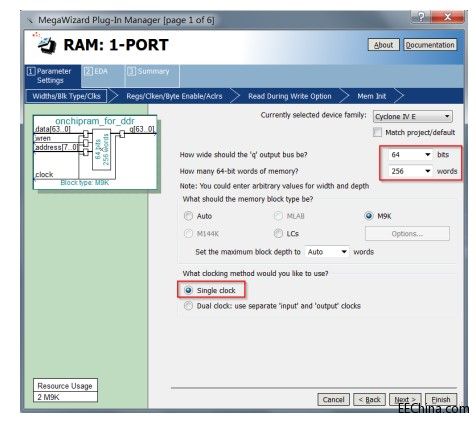

ЭМ4.3 ЕЅПкRAMДДНЈЯђЕМ Ђм ШчЭМ4.4ЫљЪОЃЌдкЕквЛИіХфжУвГУцЁАParameter Settings ЈЄ Widths/Blk Type/ClksЁБжаЃЌЮвУЧашвЊзіШчЯТЕФЩшжУЁЃ Ёё дкЁАHow wide should the ЁЏqЁЏ output bus be?ЁБКѓУцЪфШыЁА64ЁБbitsЃЌМДИУЦЌФкRAMЕФДцДЂЮЛПэЪЧ64ЁЃ Ёё дкЁАHow many 64-bit words of memory?ЁБКѓУцЪфШыЁА256ЁБwordsЃЌМДИУЦЌФкRAMЕФДцДЂЩюЖШЮЊ256ЁЃ Ёё дкЁАWhat should the memory block type be?ЁБЯТУцПЩвдбЁдёЁАAutoЁБЃЌвВПЩвдбЁдёЁАM9KЁБЃЌБэЪОЮвУЧЕФRAMЪЧЪЙгУFPGAЙЬгаЕФЦЌФкДцДЂЦїзЪдДЛЙЪЧТпМЃЈLCsЃЉзЪдДЁЃ Ёё дкЁАWhat clocking method would you like to use?ЁБЯТУцбЁдёЁАSignal clockЁБЃЌБэЪОИУRAMЕФЖСВйзїЛђаДВйзїЪЙгУЭЌвЛИіЪБжгЁЃ

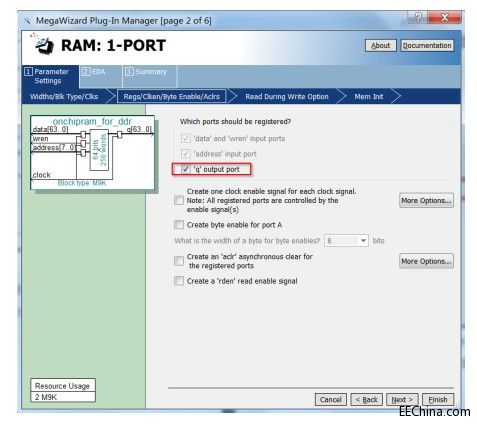

ЭМ4.4 RAMВЮЪ§ЩшжУ1 Ђн ШчЭМ4.5ЫљЪОЃЌдкЕкЖўИіХфжУвГУцЁАParameter Settings ЈЄ Regs/Clken/Byte Enable/AclrsЁБжаЃЌзіШчЯТЩшжУЁЃ Ёё дкЁАWhich ports should be registered?ЁБЯТУцбЁдёЁАЁЏqЁЏ output portЁБЃЌБэЪОЁЎqЁЏаХКХЪфГіЪБЛсгУЪБжгclockДђвЛХФЃЌетбљИќгаРћгкЪБађЪеСВЁЃ

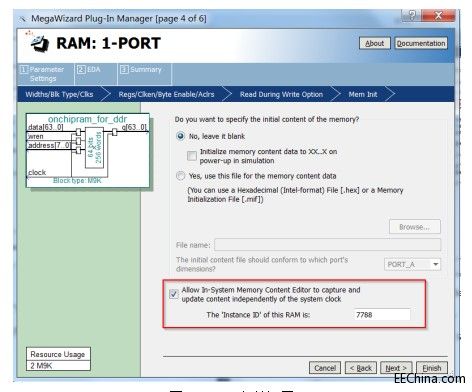

ЭМ4.5 RAMВЮЪ§ЩшжУ2 Ђо ЕкШ§ИіХфжУвГУцЁАParameter Settings ЈЄ Read During Write OptionЁБПЩвдВЛгУРэЛсЃЌФЌШЯЩшжУОЭКУЁЃ Ђп ЕкЫФИіХфжУвГУцЁАParameter Settings ЈЄ Mem InitЁБдђашвЊЬиБ№ЩшжУвЛЯТЃЌШчЭМ4.6ЫљЪОЁЃ Ёё дкЁАDo you want to specify the initial content of the memory?ЁБЯТУцЙДбЁЁАNo,leave it blankЁБЁЃБэЪОЮвУЧВЛашвЊЩшжУRAMЕФГѕЪМЛЏЮФМўЃЌЕБШЛСЫЃЌдкФГаЉЬиЪтгІгУжаЃЌЩшМЦепЯЃЭћгаГѕЪМЛЏRAMЮФМўЃЌФЧУДПЩвдЙДЩЯЁАYes,use this file for the memory content dataЁБбЁЯюЃЌШЛКѓдкИпССЕФЁАFile nameЁБКѓУцбЁдёГѕЪМЛЏRAMЮФМўЁЃ Ёё ЙДбЁЩЯЁАAllow In-System Memory Content Editor to capture and update content independently of the system clockЁБЃЌвђЮЊЮвУЧдкАхМЖЕїЪдЪБЃЌНЋЛсгУЕНIn-System Memory Content EditorЙЄОпРДЪЕЪБВщПДRAMжаЕФФкШнБфЛЏЁЃЁАThe ЁЎInstance IDЁЏ of this RAM is:ЁБКѓУцЫцБуЪфШывЛИіЪ§ОнЃЌШчЮвУЧЪфШыЁА7788ЁБЃЌетИіЪ§ОнРрЫЦвЛИіIDКХЃЌЫќжївЊЪЧЧјЗжIn-System Memory Content EditorЙЄОпВщПДВЛЭЌЕФRAMЁЃ

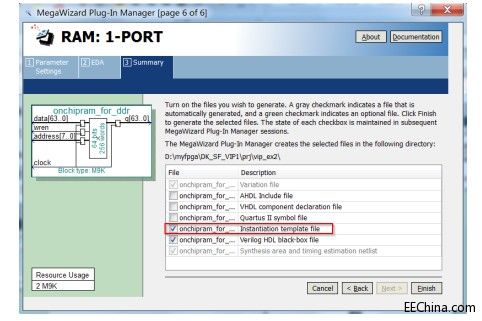

ЭМ4.6 RAMВЮЪ§ЩшжУ3 Ђр зюКѓЃЌдкЁАSummaryЁБвГУцжаЃЌШчЭМ4.7ЫљЪОЃЌЙДбЁЩЯЁАonchipram_for_ddr_inst.vЁБЮФМўЫљдкбЁЯюЁЃЕуЛїЁАFinishЁБЭъГЩЩшжУЁЃ

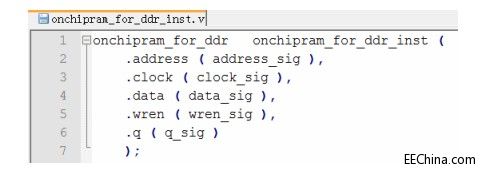

ЭМ4.7 RAMХфжУSummaryвГУц onchipram_for_ddr_inst.vЮФМўДђПЊШчЭМ4.8ЫљЪОЃЌетРягааТНЈRAMЕФНгПкР§ЛЏФЃАхЃЌПЩвдИДжЦЕНЙЄГЬЖЅВудДТыжажиаТзіНгПкгГЩфЁЃ

ЭМ4.8 RAM IPКЫР§ЛЏФЃАх |

ЭјгбЦРТл