ЛљгкXilinx MIS IPЕФDDR3ЖСаДUser InterfaceНтЮі

ЗЂВМЪБМфЃК2016-10-13 14:53

ЗЂВМепЃКrousong1989

|

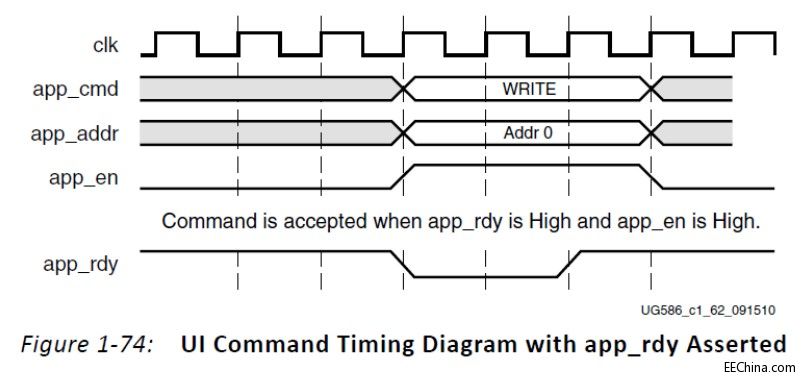

ЛљгкXilinx MIS IPЕФDDR3ЖСаДUser InterfaceНтЮі ЬиШЈЭЌбЇЃЌАцШЈЫљгаЃЌзЊдиЧызЂУїГіДІ ВЮПМЮФЕЕЃКug586_7Series_MIS.pdf 1. CommandЪБађ ЪзЯШЃЌЙигкUser InterfaceЕФCommandЪБађЃЌugжажЛИјГівдЯТВЈаЮЁЃМђЕЅЕФРДНВЃЌapp_cmdКЭapp_addrгааЇЃЌЧвapp_enРИпЃЌapp_rdyРИпЃЌдђИУУќСюГЩЙІЗЂЫЭИјDDR3 Controller IPЃЛШєЪЧдкapp_cmdЁЂapp_addrКЭapp_enЖМгааЇЪБЃЌapp_rdyЮЊЕЭЃЌФЧУДБиаыБЃГжapp_cmdЁЂapp_addrКЭapp_enЕФгааЇзДЬЌжБЕНapp_rdyРИпЃЌФЧУДИУУќСюВХЫуЪЧГЩЙІЗЂЫЭИјDDR3 Controller IPЁЃ

еввЛИіЪЕР§РДПДЃЌШчЭМЫљЪОЃЌдкapp_enСЌајРИпЗЂЦ№ЖрДЮаДШыУќСюЪБЃЌЕк58ИіЪБжгжмЦкЃЌгіЕНСЫapp_rdyРЕЭЕФЧщПіЃЌДЫЪБашвЊБЃГжЕБЧАЕФapp_cmdКЭapp_addrВЛБфЃЌapp_enвВМЬајЮЊИпЃЌжБЕНЕк59ИіЪБжгжмЦкЃЌapp_rdyРИпСЫЃЌФЧУДЫЕУїИУаДУќСюГЩЙІЁЃ

2. Ъ§ОнаДШыЪБађ ЖдгкЕЅДЮЕФЪ§ОнаДШыDDR3 Controller IPЃЌugжавВжЛИјГіШчЭМЫљЪОЕФЪБађВЈаЮЁЃетРяЖдгІаДШыcommandЗЂЦ№ЕФЧАКѓга1ЁЂ2КЭ3ВЛЭЌЪБМфЕФData WriteЪБађЃЌвВОЭЪЧЫЕЃЌЖдгІетИіаДШыcommandЃЌЪ§ОнБШcommandдчвЛЕуЛђЭэвЛЕуаДШыЖМЪЧПЩвдЕФЁЃ

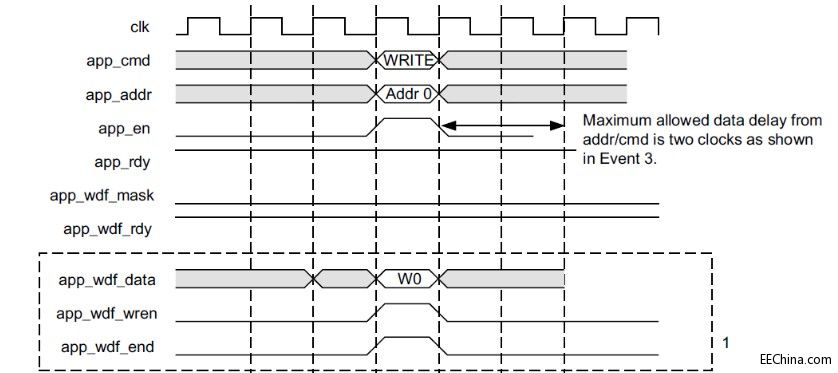

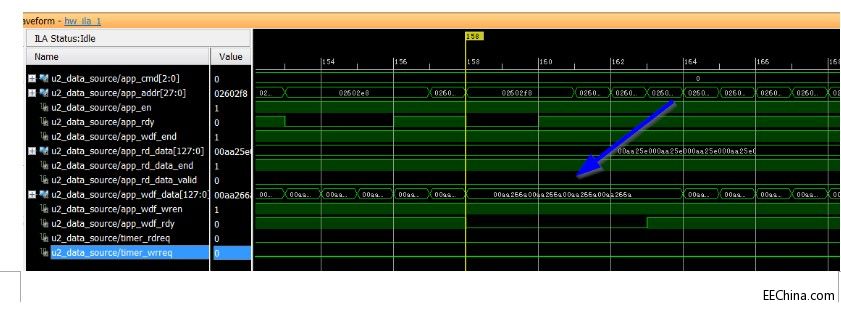

дѕУДРэНтЁАЪ§ОнБШcommandдчвЛЕуЛђЭэвЛЕуаДШыЖМЪЧПЩвдЕФЁБетОфЛАЃПugгаЬсЕНЃЌcommandвдМАdataЖМгаИїздЕФFIFOЃЌвђДЫЫћУЧЪЧашвЊЭЌВНЕФЃЌЛЛОфЛАЫЕЃЌШчЙћШУЮвЩшМЦетИіcontrollerЕФUser InterfaceЃЌВЂЧвКЭФПЧАЕФЛњжЦвЛбљЃЌcommandКЭdataЖМгаFIFOЃЌФЧУДКмМђЕЅЃЌЮвЛсИљОнcommand FIFOжаЕФаТУќСюЃЌЖдгІШЁвЛИіdata FIFOжаЕФаДШыЪ§ОнЃЌвВВЛгУЙмЫќУЧЫЯШБЛЫЭЕНИїздЕФFIFOжаЁЃЕБШЛСЫЃЌcommand FIFOгаУќСюЪЧdata FIFOШЁЪ§ОнЕФЯШОіЬѕМўЁЃжСгкСНИіFIFOЭђвЛВЛЭЌВНЃЌФЧУДдѕУДАьЃПУЛАьЗЈЃЌгУЛЇБиаыБЃжЄЫќУЧЭЌВНЁЃЪТЪЕОЭЪЧетУДВаПсЃЌЬиШЈЭЌбЇдкетРяГдОЁПрЭЗЃЌзмЫуЪЧИуУїАзСЫЃЌБиаыmarkвЛЯТЁЃ ЧАУцЫЕcommandЪБЙизЂНгПкapp_cmdЁЂapp_addrЁЂapp_enКЭapp_rdyЃЌетРяаДЪ§ОндђашвЊЙизЂНгПкapp_wdf_dataЁЂapp_wdf_wrenЁЂapp_wdf_endКЭapp_wdf_rdyЁЃ ЯШЫЕapp_wdf_endЃЌDDR3ЪЕМЪЖСаДЕФBurst =8ЃЌОйР§РДЫЕЃЌDDR3ЕФЪ§ОнЮЛПэЮЊ16bitЃЌBurstЮЊ8ЃЌОЭЪЧЫЕУПДЮЖдDDR3жДааЖСаДЃЌБиаыЪЧСЌајЕФ8*16bitЪ§ОнЁЃФЧУДдкUser InterfaceетЖЫЃЌШчЙћТпМЪБжгЮЊDDR3ЪБжгЕФ4ЗжЦЕЃЌЧвЪ§ОнЮЛПэЮЊ128bitЃЌФЧУДЕЅИіЪБжгжмЦкОЭЖдгІBurst=8ЕФвЛДЮЖСаДВйзїЃЛЖјШчЙћЪ§ОнЮЛПэЮЊ64bitЃЌФЧУДБиаыжДаа2ДЮЪ§ОнВйзїВХФмЙЛЭъГЩвЛДЮBurst=8ЕФЖСаДЁЃЖдгкЧАепЃЌapp_wdf_endЪМжеЮЊ1ОЭПЩвдСЫЃЛЖјЖдгкКѓепЃЌapp_wdf_endУП2ИіаДЪ§ОнЪБжгжмЦкФкЃЌЧАвЛДЮРЕЭЃЌКѓвЛДЮРИпЁЃ грЯТ3ИіаХКХapp_wdf_dataЁЂapp_wdf_wrenКЭapp_wdf_rdyЃЌЫћУЧЕФЙЄзїдРэКЭcommandЪБађРрЫЦЁЃapp_wdf_dataгааЇЃЌЧвapp_wdf_wrenРИпЃЌБиаыapp_wdf_rdyвВЮЊИпЃЌВХБэЪОЕБЧАЪ§ОнаДШыDDR3 Controller IPЁЃ РДПДИіЪЕР§ЃЌШчЭМЫљЪОЃЌapp_wdf_enвЛжБРИпНјааЪ§ОнаДШыЁЃЕк158ИіЪБжгжмЦкЃЌapp_wdf_rdyРЕЭСЌај5ИіЪБжгжмЦкЃЌДЫЪБМДБуapp_wdf_enвЛжБРИпвВЮоЗЈЭъГЩЪ§ОнаДШыЃЌapp_wdf_dataБиаывЛжБholdжБЕНЕк163ИіЪБжгжмЦкapp_wdf_rdyРИпЁЃ

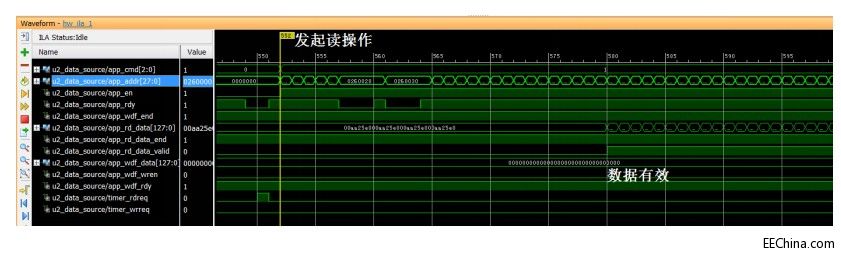

БиаыЬсабЕФЪЧЃЌжДаааДЪ§ОнcommandКЭжДаааДЪ§ОнВйзїЃЌЫќУЧЪЧвЛвЛЖдгІЕФЃЌЫфШЛПижЦЪБађПЩвдЗжПЊЪЕЯжЁЃ 3. ЖСЪ§ОнЪБађ РэНтСЫаДЪБађЃЌЖСЪБађвВОЭКмШнвзСьЛсСЫЃЌЫќУЧБОжЪЩЯЪЧвЛбљЕФЁЃУПИіЪ§ОнЕФЖСВйзїЃЌвВашвЊЯШгаЖСcommandЕФЗЂЦ№ЃЌЕБгааЇЖСcommandЗЂЦ№КѓЃЌШєИЩИіЪБжгжмЦкКѓЃЌapp_rd_data_validРИпЃЌДЫЪБapp_rd_dataгааЇЃЌгУЛЇТпМОнДЫЖСГіЪ§ОнМДПЩЃЌЗЧГЃМђЕЅЁЃЖдгкСЌајЖСШЁвВЪЧвЛбљЕФЁЃUser InterfaceПЩвдЛЉЛЉЫЭвЛДѓЖбЖСcommandЃЌзЂвтетаЉЖСcommandБиаыЖМЪЧгааЇcommandЃЌЫцКѓОЭЕШзХapp_rd_data_validРИпНгЪеapp_rd_dataМДПЩЁЃ

вВПДПДЪЕМЪВйзїЃЌШчЭМЫљЪОЃЌЗЂЦ№Ъ§ОнЖСВйзїКѓЃЌДѓдМОЙ§30ИіЪБжгжмЦкКѓЃЌЪ§ОнВХСЌајГіЯжЁЃЪ§ОнЪЧpipelineЗНЪНГіЯжЕФЃЌЫљвдОЁПЩФмСЌајЕФЖСШЁЪ§ОнПЩвдДѓДѓЬсИпЪ§ОнЭЬЭТСПЁЃ

|

ЭјгбЦРТл