ПьЕуPCBЈOФужЊЕРЖрЩйзшПЙПижЦЃП

|

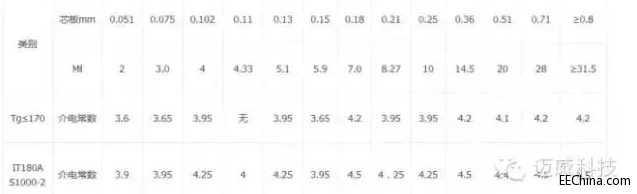

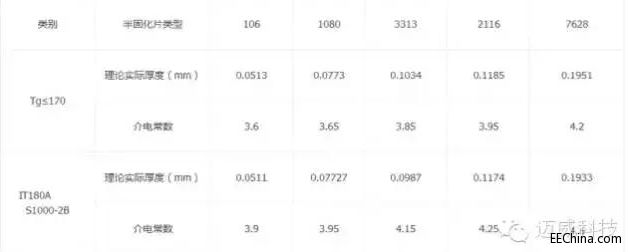

1ЁЂзшПЙПижЦИХФюНщЩм ЮЊЧјБ№жБСїЕч(DC)ЕФЕчзшЃЌАбНЛСїЕчЫљгіЕНЕФзшСІГЦЮЊзшПЙ(Z0)ЃЌАќРЈЕчзш(R)ЁЂИаПЙ(XC)КЭШнПЙ(XL)ЁЃ ЬиадзшПЙгжГЦЁАЬиеїзшПЙЁБЁЃЪЧжИдкФГвЛЦЕТЪЯТЃЌДЋЪфаХКХЯпжа(вВОЭЪЧЮвУЧжЦзїЕФЯпТЗАхЕФЭЯп)ЃЌЯрЖдФГвЛВЮПМВу(вВОЭЪЧГЃЫЕЕФЦСБЮВуЁЂгАЩфВуЛђВЮПМВу)ЃЌЦфИпЦЕаХКХЛђЕчДХВЈдкДЋВЅЙ§ГЬжаЫљЪмЕФзшСІГЦжЎЮЊЬиадзшПЙЃЌЫќЪЕМЪЩЯЪЧЕчзшПЙЁЂЕчИаПЙЁЂЕчШнПЙЕШвЛИіЪИСПзмКЭЁЃ 2ЁЂПижЦPCBЬиадзшПЙЕФвтвх PCBдкЕчзгВњЦЗжаВЛНіЦ№ЕчСїЕМЭЈЕФзїгУ,ЭЌЪБвВЦ№аХКХДЋЫЭЕФзїгУ; ЕчзгВњЦЗЕФИпЦЕЁЂИпЫйЛЏЃЌвЊЧѓPCBЬсЙЉЕФЕчТЗадФмБиаыБЃжЄаХКХдкДЋЪфЙ§ГЬжаВЛЗЂЩњЗДЩфЃЌБЃГжаХКХЭъећЁЂВЛЪЇецЃЛ ЬиадзшПЙЪЧНтОіаХКХЭъећадЮЪЬтЕФКЫаФЫљдкЃЛ ЕчзгЩшБИЃЈШчЕчФдЁЂЭЈаХНЛЛЛЛњЕШЃЉВйзїЪБЃЌЧ§ЖЏдЊМў(Driver)ЫљЗЂГіЕФаХКХЃЌашЭЈЙ§PCBаХКХЯпЕНДяНгЪедЊМўЃЈReceiverЃЉЁЃЮЊБЃжЄаХКХЭъећадЃЌвЊЧѓPCBЕФаХКХЯпЕФЬиадзшПЙЃЈZ0ЃЉБиаыгыЭЗЮВдЊМўЕФЁАЕчзгзшПЙЁБЦЅХфЃЛ ЕБДЋЪфЯпЁн1/3ЩЯЩ§ЪБМфГЄЖШЪБЃЌаХКХЛсЗЂЩњЗДЩфЃЌаыПМТЧЬиадзшПЙЁЃ 3ЁЂгАЯьЬиадзшПЙЕФвђЫи НщжЪНщЕчГЃЪ§ЃЌгыЬиадзшПЙжЕГЩЗДБШ(Er)ЃЌЯТЭМЮЊГЃЙцЕФАхВФВЮЪ§:

ЯпТЗВугыНгЕиВу(ЛђЭтВу)МфНщжЪКёЖШ,гыЬиадзшПЙжЕГЩе§БШ(H),ЯТЭМЮЊГЃЙцЕФАхВФВЮЪ§:

зшПЙЯпЯпЕзПэЖШ(ЯТЖЫW1);ЯпУц(ЩЯЖЫW2)ПэЖШ,гыЬиадзшПЙГЩЗДБШЁЃ ЭКё,гыЬиадзшПЙжЕГЩЗДБШ(T) ЯрСкЯпТЗгыЯпТЗжЎМфЕФМфОр,гыЬиадзшПЙжЕГЩе§БШЃЈВюЗжзшПЙЃЉ(S) ЛљВФзшКИКёЖШ,гызшПЙжЕГЩЗДБШ(C) 4ЁЂгАЯьзшПЙЕФЙЄвевђЫи гЩгкЪДПЬдвђЃЌдкЭКё>2ozЪБЖдзшПЙгАЯьКмДѓЃЌвЛАуЮоЗЈПижЦзшПЙЁЃ ЩшМЦжаУЛгаЭКЭЯпЕФВуУцПеАздкЩњВњЪБашвЊгУЙЬЛЏЦЌШЅЬюГфЃЌдкМЦЫузшПЙЪБОЭВЛФмжБНгДњгУАхВФЙЉгІЩЬЬсЙЉЕФНщжЪКёЖШЃЌЖјашвЊМѕШЅЙЬЛЏЦЌЬюГфетаЉПеАзЕиЗНЕФКёЖШЃЌетОЭЪЧздМКМЦЫуЕФзшПЙКЭЩњВњГЇМвНсЙћВЛвЛжТЕФжївЊдвђжЎвЛЁЃ 5ЁЂзшПЙЕФМЦЫу зшПЙЕФМЦЫуЪЧЯрЖдБШНЯЗБЫіЕФЃЌЕЋЮвУЧПЩвдзмНсвЛаЉОбщжЕАяжњЬсИпМЦЫуаЇТЪЁЃЖдгкГЃгУЕФFR4ЃЌ50ohmЕФЮЂДјЯпЃЌЯпПэвЛАуЕШгкНщжЪКёЖШЕФ2БЖЃЛ50ohmЕФДјзДЯпЃЌЯпПэЕШгкСНЦНУцМфНщжЪзмКёЖШЕФЖўЗжжЎвЛЃЌетПЩвдАяЮвУЧПьЫйЫјЖЈЯпПэЗЖЮЇЃЌзЂвтвЛАуМЦЫуГіРДЕФЯпПэБШИУжЕаЁаЉЁЃ Г§СЫЬсЩ§МЦЫуаЇТЪЃЌЮвУЧЛЙвЊЬсИпМЦЫуОЋЖШЁЃДѓМвЪЧВЛЪЧОГЃгіЕНздМКЫуЕФзшПЙКЭАхГЇЫуЕФВЛвЛжТФиЃПгаШЫЛсЫЕетгаЪВУДЙиЯЕЃЌжБНгШУАхГЇЕїАЁЁЃЕЋЛсВЛЛсгаАхГЇЕїВЛСЫЃЌШУФуЗХЫЩзшПЙЙмПиЕФЧщПіФиЃПвЊзіКУВњЦЗЛЙЪЧвЛЧаОЁдкздМКЕФеЦЮеБШНЯКУЁЃ вдЯТЬсГіМИЕуЩшМЦЕўВуЫузшПЙЪБЕФзЂвтЪТЯюЙЉДѓМвВЮПМЃК aЃЌЯпПэФўдИПэЃЌВЛвЊЯИЁЃетЪЧЪВУДвтЫМФиЃПвђЮЊЮвУЧжЊЕРжЦГЬРяДцдкЯИЕФМЋЯоЃЌПэЪЧУЛгаМЋЯоЕФЁЃШчЙћЕНЪБКђЮЊСЫЕїзшПЙАбЯпПэЕїЯИЖјХіЕНМЋЯоЪБФЧОЭТщЗГСЫЃЌвЊУДдіМгГЩБОЃЌвЊУДЗХЫЩзшПЙЙмПиЁЃЫљвддкМЦЫуЪБЯрЖдПэОЭвтЮЖзХФПБъзшПЙЩдЮЂЦЋЕЭЃЌБШШчЕЅЯпзшПЙ50ohmЃЌЮвУЧЫуЕН49ohmОЭПЩвдСЫЃЌОЁСПВЛвЊЫуЕН51ohmЁЃ bЃЌећЬхГЪЯжвЛИіЧїЪЦЁЃЮвУЧЕФЩшМЦжаПЩФмгаЖрИізшПЙЙмПиФПБъЃЌФЧУДОЭећЬхЦЋДѓЛђЦЋаЁЃЌВЛвЊ100ohmЕФЦЋДѓЃЌ90ohmЕФЦЋаЁЁЃ cЃЌПМТЧВаЭТЪКЭСїНКСПЁЃЕБАыЙЬЛЏЦЌвЛБпЛђСНБпЪЧЪДПЬЯпТЗЪБЃЌбЙКЯЙ§ГЬжаНКЛсШЅЬюВЙЪДПЬЕФПеЯЖДІЃЌетбљСНВуМфЕФНККёЖШЪБМфЛсМѕаЁЃЌВаЭТЪдНаЁЃЌЬюЕФдНЖрЃЌЪЃЯТЕФдНЩйЁЃЫљвдШчЙћФуашвЊЕФСНВуМфАыЙЬЛЏЦЌКёЖШЪЧ5milЃЌвЊИљОнВаЭТЪбЁдёЩдКёЕФАыЙЬЛЏЦЌЁЃ dЃЌжИЖЈВЃВМКЭКЌНКСПЁЃПДЙ§АхВФdatasheetЕФЙЄГЬЪІЖМжЊЕРВЛЭЌЕФВЃВМЃЌВЛЭЌЕФКЌНКСПЕФАыЙЬЛЏЦЌЛђаОАхЕФНщЕчЯЕЪ§ЪЧВЛЭЌЕФЃЌМДЪЙЪЧВюВЛЖрИпЖШЕФвВПЩФмЪЧ3.5КЭ4ЕФВюБ№ЃЌетИіВюБ№ПЩвдв§Ц№ЕЅЯпзшПЙ3ohmзѓгвЕФБфЛЏЁЃСэЭтВЃЯЫаЇгІКЭВЃВМПЊДАДѓаЁУмЧаЯрЙиЃЌШчЙћФуЪЧ10GbpsЛђИќИпЫйЕФЩшМЦЃЌЖјФуЕФЕўВугжУЛгажИЖЈВФСЯЃЌАхГЇгУСЫЕЅеХ1080ЕФВФСЯЃЌФЧОЭПЩФмГіЯжаХКХЭъећадЮЪЬтЁЃ |

ЭјгбЦРТл