前言 基于学习的目的,详细讲解关于 Cube 库中的 DAC 的功能。本次介绍 DAC。

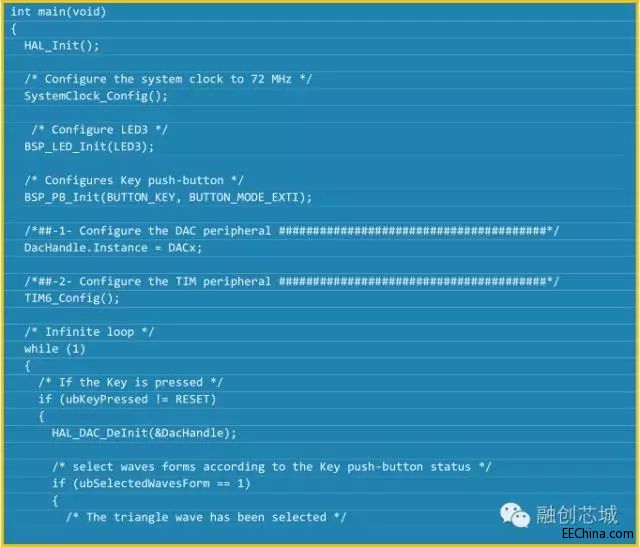

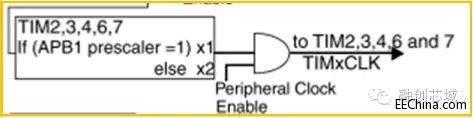

一、示例详解 基于硬件平台:STM32F10C-EVAL,MCU 的型号是 STM32F107VCT6。 软件则是其 Cube 库,路径: STM32Cube\Repository\STM32Cube_FW_F1_V1.3.0\Projects\STM3210C_EVAL\Examples\DAC\DAC_SignalsGeneration 。 1、主程序 软件配置,运行程序可以发现,系统时钟设置为 72MHz,定时器使用到的是 TIM6;

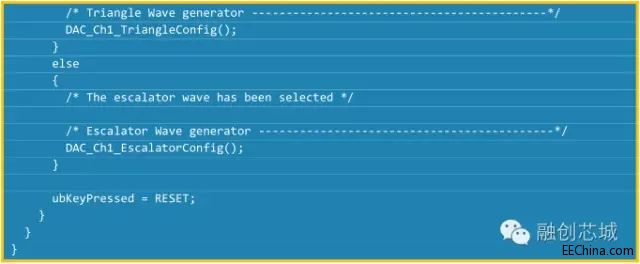

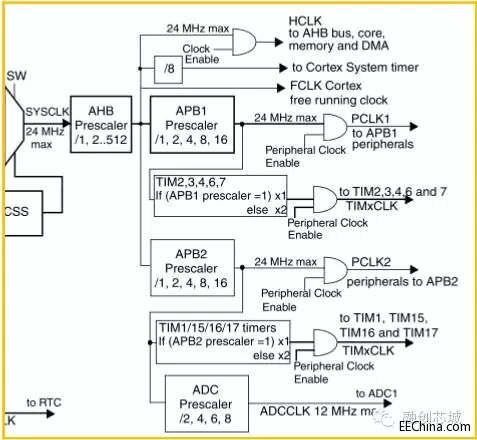

根据时钟树的图谱及其程序, 该示例选择的是内部时钟源作为定时器的时钟源;TIM6 的时钟源来自 APB1 的分频。

AHB 时钟 (HCLK)在 RCC_CFGR 寄存器中的分频系数 HPRE 的值为 0,即 SYSCLK not divided,即/1,所以 HCLK 就是72MHz; APB1 的 prescaler 的系数是 PPRE1:0x4,HCLK divided 2,即/2,APB1CLK 为 36MHz;由于 APB1 的 prescaler 系数部 分频,即/4,所以倍频器起作用,即为上图中的 TIMxCLK = 72Mhz。 2、 定时器 Tim6

设置的是向上计数,周期是 0x7FF(2047),从 0 开始计数到 2047,所以该定时器的更新周期:(2047+1)/72 = 28us,

所以传输的 6 个数值:

对于8位的DAC,程序中设定的是右对齐, 所以,对应的DOR分别为

0x000(0), 0x330(816), 0x660(1632), 0x990(2448), 0xCC0(3264), 0xFF0(4080) ;

而 Vref = 3.3V, 所以:

Vdac 分别等于:也是约在 0V; 0.66V; 1.32V; 1.98V; 2.64V; 3.3V 之间;

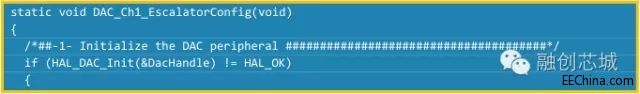

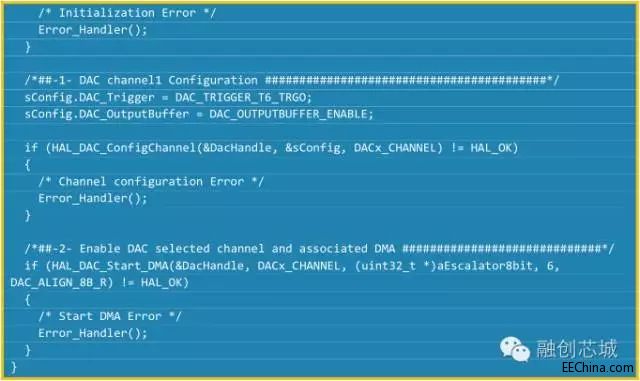

3、阶梯波形

对于阶梯波形比较简单: 就是上述的 6 个数值每个 28us 触发 DMA 传输一次到 DOR 的寄存器;

所以测得的实际波形(6 个梯阶,电压分别 0V; 0.66V; 1.32V; 1.98V; 2.64V; 3.3V; 周期 28*6 = 168us);

重要通知 - 请仔细阅读 意法半导体公司及其子公司(“ST”)保留随时对ST 产品和/ 或本文档进行变更、更正、增强、修改和改进的权利,恕不另行通知。买方订货之前应获取关于ST 产品的最新信息。ST 产品的销售依照订单确认时的相关ST 销售条款。 买方自行负责对ST 产品的选择和使用, ST 概不承担与应用协助或买方产品设计相关的任何责任。 ST 不对任何知识产权进行任何明示或默示的授权或许可。 转售的ST 产品如有不同于此处提供的信息的规定,将导致ST 针对该产品授予的任何保证失效。 ST 和ST 徽标是ST 的商标。所有其他产品或服务名称均为其各自所有者的财产。 本文档中的信息取代本文档所有早期版本中提供的信息。

|