Р§ЫЕFPGAСЌди30ЃКPLLР§ЛЏХфжУгыLEDжЎЙІФмИХЪі

ЗЂВМЪБМфЃК2016-9-9 18:12

ЗЂВМепЃКrousong1989

|

Р§ЫЕFPGAСЌди30ЃКPLLР§ЛЏХфжУгыLEDжЎЙІФмИХЪі ЬиШЈЭЌбЇЃЌАцШЈЫљга ХфЬзР§ГЬКЭИќЖрзЪСЯЯТдиСДНгЃК http://pan.baidu.com/s/1c0nf6Qc

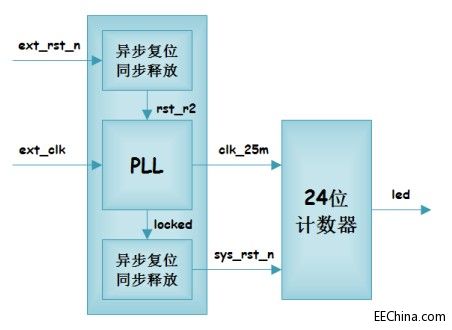

БОЪЕР§ЪЙгУQuartus IIжагУгкР§ЛЏIPКЫЕФMegafunctionХфжУвЛИіPLLФЃПщЃЌPLLФЃПщВњЩњЕФ25MHzЪБжгНјаа24ЮЛбЛЗМЦЪ§ЃЌ24ЮЛМЦЪ§ЦїЕФзюИпЮЛИГжЕИјСЌНгЕНLEDжИЪОЕЦЕФв§НХЩЯЃЌгЩДЫЪЕЯжСЫLEDвдЙЬЖЈЦЕТЪЩСЫИЕФаЇЙћЁЃ ИУЪЕР§ЕФЙІФмПђЭМШчЭМ3.1ЫљЪОЁЃFPGAЭтВПв§НХЕФИДЮЛаХКХНјШыFPGAКѓЃЌЪзЯШзіСЫвЛДЮЁАвьВНИДЮЛЃЌЭЌВНЪЭЗХЁБЕФДІРэЃЌШЛКѓетИіИДЮЛаХКХЪфШыЕНPLLФЃПщЃЌдкPLLФЃПщЪфГіЪБжггааЇКѓЃЌЫќЕФЫјЖЈаХКХlockedОЭЛсРИпЃЌЮвУЧвдДЫаХКХзїЮЊЯЕЭГЕФИДЮЛаХКХЃЌвђДЫвВзіСЫЁАвьВНИДЮЛЃЌЭЌВНЪЭЗХЁБЕФДІРэЁЃPLLЕФЪфШыЪБжгЮЊFPGAЭтВПОЇеёВњЩњЕФЪБжгаХКХЃЌЫќОЙ§PLLДІРэКѓВњЩњвЛИі25MHzЕФЪБжгаХКХЃЌ24ЮЛМЦЪ§ЦїдкетИіPLLЪБжгЕФЁАНкХФЁБЯТВЛЭЃЕФМЦЪ§ЁЃ

ЭМ3.1 ЙЄГЬЪЕР§1ЙІФмПђЭМ |

ЭјгбЦРТл