例说FPGA连载24:FX2(USB 2.0)外设子板设计

发布时间:2016-8-24 17:13

发布者:rousong1989

|

例说FPGA连载24:FX2(USB 2.0)外设子板设计 特权同学,版权所有 配套例程和更多资料下载链接: http://pan.baidu.com/s/1c0nf6Qc

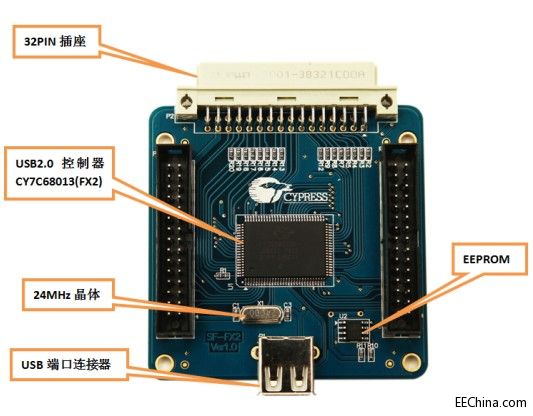

SF-FX2子板的实物照片如图2.41所示。

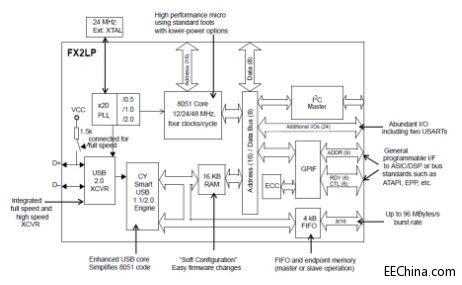

图2.41 SF-FX2子板实物照片 FX2(CY7C68013)是一款集成8051单片机的灵活的USB2.0控制器,其带宽可以接近USB2.0标称的480Mbps。 FX2的内部功能框图如图2.42所示。从图中不难看出,8051实际上并不直接参与USB数据的实际传输,而只是做一些基本的配置。从GPIF(或SlaveFIFO)接口传输的数据,在FX2内部传到了RAM中进行缓存,并且可以直接送到USB2.0的phy中传输给USB设备。

图2.42 FX2内部功能框图 SF-FX2子板和SF-VIP核心板需要进行连接的主要接口定义如表2.5所示。 表2.5 SF-FX2子板连接引脚定义

|

网友评论