Р§ЫЕFPGAСЌди16ЃКЕчдДЕчТЗЩшМЦ

ЗЂВМЪБМфЃК2016-8-5 16:01

ЗЂВМепЃКrousong1989

|

Р§ЫЕFPGAСЌди16ЃКЕчдДЕчТЗЩшМЦ ЬиШЈЭЌбЇЃЌАцШЈЫљга ХфЬзР§ГЬКЭИќЖрзЪСЯЯТдиСДНгЃК http://pan.baidu.com/s/1c0nf6Qc

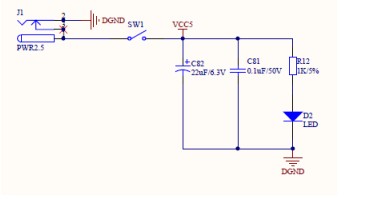

ШчЭМ2.9ЫљЪОЃЌJ1ЮЊFPGAЕФЕчдДВхзљЃЌSW1ЮЊЕчдДПЊЙиЃЌЖМЪЧЪаУцЩЯзюГЃМћЕФдЊМўЃЌD2дђЪЧЕчдДжИЪОЕЦЃЌЕБПЊЙиSW1БеКЯЪБЃЌD2ЕуССЃЌжИЪОЕБЧАЯЕЭГЙЉЕчзДЬЌЁЃ

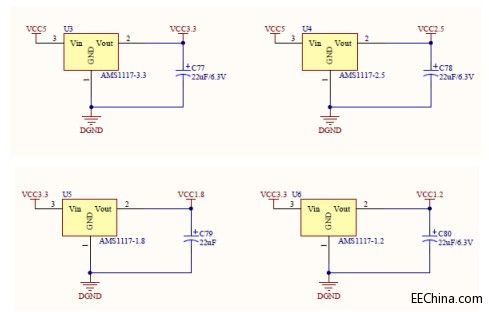

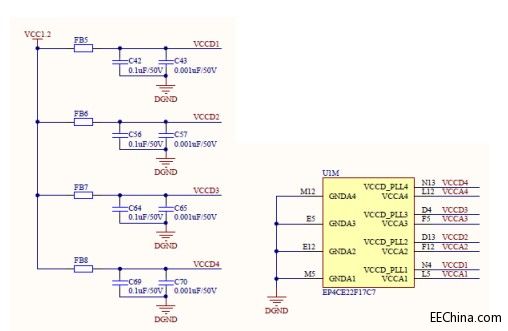

ЭМ2.9 FPGAЕчдДВхзљЕчТЗ гЩгкЮвУЧЫљбЁдёЕФCyclone IVЯЕСаFPGAЦїМўећЬхЙІКФВЂВЛДѓЃЌвђДЫЛёЕУИќКУЕЭЮЦВЈЕчдДадФмЃЌШчЭМ2.10ЫљЪОЃЌЮвУЧЪЙгУСЫ4ПХLDOВњЩњFPGAЫљашвЊЕФ3.3VЁЂ2.5VЁЂ1.8VКЭ1.2VетЫФЕЕЕчбЙЁЃ

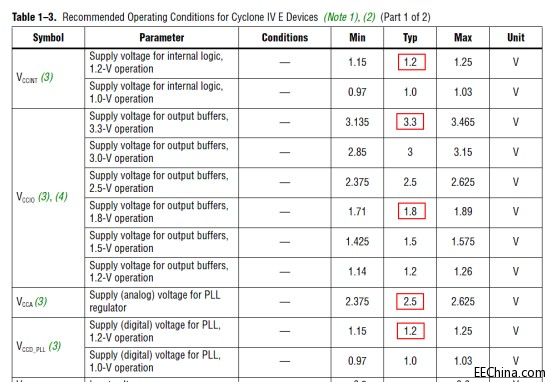

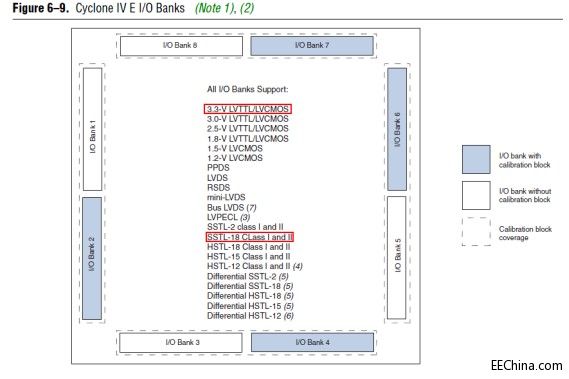

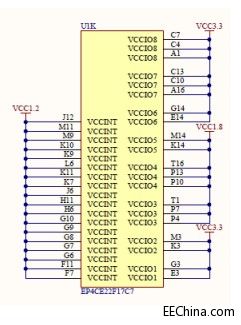

ЭМ2.10 FPGAЫФЕЕЕчдДЕчбЙВњЩњЕчТЗ ШчЭМ2.11ЫљЪОЃЌДгCyclone IV Device HandbookжаПЩвдВщЕНЃЌCyclone IVЯЕСаЦїМўЕФЙЉЕчвЛАуЪЧЗж4ДѓРрЃЌбЙжЕга3-4ЕЕЃЈПЩФмИќЖрЕЕЃЌетжївЊШЁОігкВЛЭЌbankЕФI/OЕчбЙЪЧЗёгаЬиЪтЙЉЕчашЧѓЃЉЁЃет4РрЕчдДЗжБ№ЪЧФкКЫЕчбЙVCCINTЁЂI/OЕчбЙVCCI/OЁЂPLLФЃФтЕчбЙVCCAКЭPLLЪ§зжЕчбЙVCCD_PLLЁЃет4РрЕчдДЕчбЙжаЃЌФкКЫЕчбЙЙЬЖЈ1.2VЁЂPLLФЃФтЕчбЙЙЬЖЈ2.5VЁЂPLLЪ§зжЕчбЙЙЬЖЈ1.2VЃЛЮЈвЛВЛШЗЖЈЃЌЛђепЫЕгабЁдёгрЕиЕФЕчдДЪЧI/OЕчбЙЃЌЫќПЩвдИљОнгУЛЇЪЕМЪгІгУЫљашвЊЕФI/OБъзМбЁдёВЛЭЌЕФЕчбЙЃЌЮвУЧЕФАхзггЩгкашвЊЪЙгУDDR2 SDRAMЃЌЫќЫљСЌНгЕФFPGA bankЖдгІЕФI/OЕчбЙЪЧ1.8VЃЌЦфЫћЕФbankЖМЪЙгУзюГЃМћЕФ3.3VЙЉЕчЁЃ

ЭМ2.11 Cyclone IVЯЕСаЦїМўЕФЙЉЕчБъзМ ЫЕЕНI/OЕчбЙЃЌЮвУЧВЛЕУВЛЖрЬсСНОфЃЌБЯОЙПЩвдМцШнЗЧГЃЖрЕФI/OЕчбЙБъзМЪЧFPGAЕФвЛДѓгХЪЦЃЌгШЦфЪЧИїжжИпЫйВюЗжаХКХЕФжЇГжЁЃЭМ2.12жаСаГіСЫЮвУЧетПюЦїМўжЇГжЕФИїжжI/OЕчЦНБъзМЁЃЗНаЮПђГіЕФ3.3-V LVTTLКЭSSTL-18 Class IдђЪЧЮвУЧетПюFPGAКЫаФАхжаЪЕМЪЪЙгУЕФI/OЕчЦНБъзМЁЃ

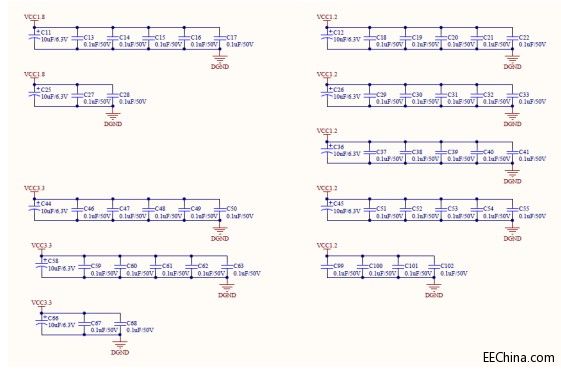

ЭМ2.12 Cyclone IV FPGAЫљжЇГжЕФИїжжЕчЦНБъзМ FPGAЕФЙЉЕчЕчТЗШчЭМ2.13ЁЂЭМ2.14ЫљЪОЁЃдкFPGAЕФЙЉЕчЕчТЗжаЃЌУП1-2ИіЕчдДв§НХЮвУЧЖМХфга1ИіШЅёюЕчШнЁЃЕБШЛСЫЃЌдкПеМфдЪаэЕФЧщПіЯТЃЌУПИіЕчдДв§НХОЁСПЖМОЭНќЗХжУШЅёюЕчШнЁЃ

ЭМ2.13 FPGA PLLЙЉЕчЕчТЗ

ЭМ2.14 FPGA I/OКЭКЫбЙЙЉЕчЕчТЗ ЙигкFPGAЕчдДЕчТЗЕФPCB LayoutЩшМЦЃЌЭЈГЃашвЊзёбвдЯТЕФддђЁЃ Ёё ЭъећЕФЛђЗжИюЕФЕчдДВуЖМгІИУОЭНќгыЦфЖдгІЕФЕиВуЁЃ Ёё ЕчдДВуКЭЕиВужЎМфЕФОјдЕВугІИУОЁПЩФмЕФБЁЃЌвддіЧПёюКЯЕчШнгыЦНУцЕчШнЃЈЭЈГЃШЁ3-4milЃЉЁЃ Ёё ЮЊСЫзюаЁЛЏЕчИажЕЃЌЕчдДв§НХгІЕБОЭНќжБНгСЌЕНЯргІЕФЕчдДВуЁЃБмУтЦїМўЕФЕчдДв§НХгыЙЉЕчдДЖЫЛђЕчдДВужЎМфЕФзпЯпПэЖШЙ§еЁЃАхМЖЩшМЦепгІИУЖрВЮПМЕчдДаОЦЌГЇЩЬЬсЙЉЕФЩшМЦжИФЯЁЃ Ёё ЕчдДЗжИюЯпЕФМфОргІИУдк25milЕН100milЁЃ Ёё ВЛЭЌЕчдДв§НХВЛФмЙЛЙВгУвЛИіЙ§ПзЁЃЛЛОфЛАЫЕЃЌУПИіЕчдДв§НХЖМгІИУжСЩйгавЛИізЈгУЕФЙ§ПзСЌНгЕНЕчдДВуЁЃ |

ЭјгбЦРТл